Fターム[5J106KK37]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 目的、効果 (3,441) | IC化,LSI化 (197)

Fターム[5J106KK37]に分類される特許

41 - 60 / 197

周波数発生のための装置及び方法

広帯域周波数発生器は、フリップチップパッケージ内の同一のダイに配置された異なる周波数帯域のための2つ以上の発振器を有する。2つの発振器の誘導子間の結合は、一方の誘導子がダイに配置され、他方の誘導子がパッケージに配置され、これら誘導子がハンダバンプの直径によって離されることで、減少させられる。弱結合されたこれら誘導子では、一方の発振器の帯域を増加させるために他方の発振器のLCタンク回路の操作をしたり、その逆を行ったりできる。一方の発振器の振動の好ましくないモードを防ぐことは、他方の発振器の粗同調バンクの全容量といった大容量を他方の発振器のLCタンク回路に与えることによって達成され得る。好ましくないモードを防ぐことは、他方の発振器のLCタンクのQファクタを減少させ、タンク回路内の損失を増加させることによっても達成され得る。 (もっと読む)

時間デジタル変換器

【課題】時間遅延量の最適値制御が行える時間デジタル変換器を提供すること。

【解決手段】入力されるクロック信号を多段に遅延する複数の遅延段を有し、該複数の遅延段の少なくとも1つが可変遅延段である遅延回路と、前記遅延回路の遅延段と同数個設けられ、参照信号の入力に応答して並列に対応する遅延段の出力を取り込む複数のフリップフロップと、前記複数のフリップフロップの各出力の立ち上がりと立ち下がりの一方または両方を検出するエッジ検出回路と、前記エッジ検出回路が検出したエッジ数をカウントするカウンタ回路と、前記カウンタ回路がカウントしたエッジ数に応じて前記可変遅延段の遅延量を制御する制御回路とを備える。

(もっと読む)

クロック分配回路およびクロック分配方法

【課題】クロック分配網間のクロックスキューをより低減する。

【解決手段】リファレンスクロック信号11の位相を調整してクロック分配網に分配するPLL回路1、2と、クロック分配網における複数のフィードバック点PA1〜PAn、PB1〜PBnからそれぞれフィードバッククロック信号HA1〜HAn、HB1〜HBnを入力し、PLL回路1、2でリファレンスクロック信号11の位相比較対象とされる複数のフィードバッククロック信号から一つの信号を、複数のフィードバッククロック信号のそれぞれの遅延値に基づいて選択するフィードバッククロック信号選択回路9、16と、を複数のクロック分配網のそれぞれに対応して備える。

(もっと読む)

位相同期発振器アレイ

【課題】小型でIC化が可能な位相同期発振器を実現すること。

【解決手段】 位相同期した複数の発振信号を得る位相同期発振器アレイにおいて、位相が180度異なる2つの信号を入力する第1入力端子と第2入力端子とを有したn個の第1差動増幅器から第n差動増幅器と、1≦k<nの全ての自然数kに対して、第k差動増幅器の第2入力端子と第k+1差動増幅器の第1入力端子との間の全て、及び、第n差動増幅器の第2入力端子と第1差動増幅器の第1入力端子との間を、それぞれ、逆相で結合するn個のフィルタFと、を設けたことを特徴とする位相同期発振器アレイ。フィルタFは、一方の差動増幅器1の第2入力端子B12と接地間に配設された第2インダクタL12と、他方の差動増幅器2の第1入力端子B21と接地間に配設された第1インダクタとL21、一方の差動増幅器1の第2入力端子と他方の差動増幅器2の第1入力端子との間を接続する第3容量C15と第3インダクタL23との直列接続回路とを有する。

(もっと読む)

集積回路、集積回路システム、シリアルパラレル変換装置およびスキュー調整方法

【課題】簡単な回路または簡単な処理によりスキュー調整する。

【解決手段】集積回路3は、入力された外クロック信号を遅延させた内クロック信号を出力するクロック遅延回路43と、入力されたデータ信号を内クロック信号によりラッチするラッチ回路45と、クロック遅延回路43に対して、外クロック信号に対する内クロック信号の遅延量として、複数の遅延量を設定する遅延量設定回路58と、複数の遅延量それぞれの設定の下でのラッチ回路45の出力信号を判定するラッチ判定回路52と、ラッチ判定回路52による複数の遅延量それぞれについての複数の判定値を記憶する記憶部53と、記憶部53に記憶された複数の判定値とクロック遅延回路43に設定した複数の遅延量との関係から、クロック遅延回路43による内クロック信号の遅延量を取得する遅延量取得部とを有する。

(もっと読む)

非重複クロック生成のための技術

【解決手段】望ましい周波数範囲にわたって、正確な非重複時間及びクロックフェーズ遅延時間を生成する技術が提供される。一構成において、装置はそれに結合されるクロック生成回路への制御電圧を順に生成する遅延ロックループ(DLL)回路を含む非重複クロック生成回路を備えている。制御電圧はクロック生成回路によって生成される非重複遅延クロック信号の正確なタイミング関係を維持するように動作する。一態様において、DLL回路は知られたデューティサイクルによる入力クロックを受信し、入力クロックサイクルの特定の部分へのユニット遅延をフィックスする出力制御電圧を得る。更なる態様において、クロック生成回路は製造プロセス変化とは関係ない非重複時間(tnlp)でクロック信号の第1のセットから遅延されたクロック信号の第2のセット及びクロック信号の第1のセットを生成するDLL回路に結合される複数の電圧制御遅延セルを備えている。 (もっと読む)

ディザ処理型クロック発生器

【課題】 位相分解能を高くし周波数スペクトラムのピークを低減したスペクトラム拡散クロック発生器を提供する。

【解決手段】 本発明のスペクトラム拡散クロック発生器100は、基準クロック信号と帰還クロック信号の位相差を検出する位相比較器20、チャージポンプ22、ループフィルタ24、多相のクロック信号を発生する多相VCO22、多相VCO26からの隣合う位相のクロック信号の位相を補間する位相補間部120、位相補完部120の位相選択を制御する位相選択部130、一定のステップ幅で段階的に変化する1周期分の変調波形データを記憶する変調データ部140、ディザステップ信号DSを出力するディザ処理部150、変調波形データとディザステップ信号を加算する加算器160を有する。位相選択部130は、ディザステップ信号が加算された変調波形データに基づき位相の補間を行う。

(もっと読む)

原子発振器

【課題】安価な原子発振器を構成する。

【解決手段】原子共鳴器10が発生する共鳴信号54を増幅する増幅器18と、所定の周波数の低周波信号LWVを出力する低周波位相変調信号発生器21と、共鳴信号54と低周波信号LWVとに基づき制御電圧VCを出力する位相弁別器20と、制御電圧VCに基づき原子共鳴器10が正常に動作しているか否かを示すアラーム信号ALMを出力するアラーム回路30と、所定の電圧VDを発生する電圧発生部32と、アラーム信号ALMに基づき原子共鳴器10が正常に動作している場合は制御電圧VCを出力し、正常に動作していない場合は所定の電圧VDを出力するスイッチ回路34と、スイッチ回路34の出力に基づき出力信号OUTの周波数が制御される電圧制御水晶発振器23と、出力信号OUTと低周波信号LWVとに基づき逓倍及び合成したマイクロ波MWVを出力する周波数逓倍合成変調部22と、を含む原子発振器1。

(もっと読む)

半導体装置、携帯通信端末、ICカード及びマイクロコンピュータ

【課題】搬送波からクロック信号の抽出が出来ないときも内部動作が停止することなく通信動作を行うことができる非接触インタフェース技術を提供する。

【解決手段】変調された搬送波をアンテナ(10)から入力し、入力した搬送波から抽出したクロック信号(CLKREF)に基づいて内部クロック信号(CLKPLL)を生成し、内部クロック信号に同期動作する半導体装置(11)において、抽出されたクロック信号を入力して内部クロック信号を生成するPLL回路(13)に、前記搬送波から抽出されたクロック信号が離散的に途切れた場合に内部クロック信号をその直前の周波数に維持させる電圧制御発振機能を搭載する。これにより、前記搬送波から抽出されるクロック信号が途切れてもデコードやバスインタフェースなどの内部のデータ処理を継続することができる。

(もっと読む)

デジタルクロック・データ復元機およびこれを適用したトランシーバー

本発明は、デジタルフィルタ回路(digital filter)とデジタル制御発振器(DCO;digitally controlled oscillator)を用いて回路全体をデジタル回路化したクロック・データ復元機に関するものであり、本発明に係るデジタル制御発振器は、複数個のインバータチェーンを備えており、それぞれのインバータに電源電流を供給する電源電圧とインバータの間に可変抵抗スイッチングマトリックスを構成して供給電源を変化させ、発振周波数をチューニングする。

ここで、可変抵抗スイッチングマトリックスは、PMOSトランジスタ配列を用いて具現化するものの、低いレベルでの周波数チューニングステップと高いレベルでの周波数チューニングステップを互いに均等化するために、スイッチングマトリックスの列と列の間に垂直抵抗を追加挿入している。また、ジッタ発生問題を解消するために、第1シグマデルタモジュレータを用いてディザリング回路を具現化しており、セグメントサーモメーター方式を適用して少ない個数のルーティングラインでデジタル制御発振器をチューニングしている。  (もっと読む)

(もっと読む)

PLL回路

【課題】位相比較回路と、チャージポンプと、ループフィルタと、電圧制御発振回路とがこの順に接続されてなるPLL回路において、ループ帯域幅に変動が起こっても容易に対応できるPLL回路を提供する。

【解決手段】位相比較回路は、電圧制御発振回路から出力される帰還信号と、外部より入力される基準信号とが接続される2入力を備え、チャージポンプは種々の利得に対応した電流源を備え、基準信号と位相比較回路の出力からPLLがロックしたときのロック信号を出力するPLLロック検出回路と、基準信号をカウントするカウント回路と、ロック信号とカウンタ回路のカウンタ信号からロック時のカウンタ信号をラッチするラッチ回路と、基準信号を入力する前に一定の利得に対応した電流源のコードに設定され、基準信号を入力後ロック信号及びラッチされたカウンタ信号から適切な利得に対応した電流源のコードを選択して出力する選択手段とを備えている。

(もっと読む)

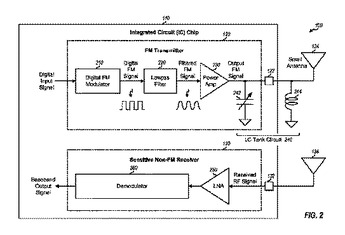

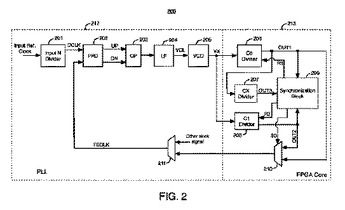

シングルチップ上に集積されたFM送信機及び非FM受信機

例示的な態様は、周波数変調(FM)送信機及び非FM受信機を含み、それらは同一のICチップ上にインプリメントされる。FM送信機は、デジタルFM変調器、ロウパスフィルタ、増幅器、及びLCタンク回路を含む。デジタルFM変調器は、デジタル入力信号を受け取り、デジタル入力信号によってFM変調を行い、デジタルFM信号を供給する。ロウパスフィルタは、デジタルFM信号をフィルタし、フィルタされたFM信号を供給する。増幅器は、フィルタされたFM信号を増幅し、出力FM信号を供給する。LCタンク回路は、出力FM信号をフィルタする。デジタルFM変調器は、PLL内のマルチモジュール分周器の可変分周比を変化させることによってFM変調を行う。デルタ−シグマ変調器は、デジタル入力信号を受け取り、可変分周比を得るために用いられる変調器出力信号を発生する。  (もっと読む)

(もっと読む)

情報システムおよび半導体装置とその制御方法

【課題】周期の小さいジッタに対する低減効果を向上する。

【解決手段】入力クロック信号CLKiを電圧制御遅延回路14を介して出力クロック信号CLKoとして出力すると共に、入力クロック信号CLKiと出力クロック信号CLKoとの位相比較結果に基づいて電圧制御遅延回路14における遅延量を制御する。位相補正回路21は、入力クロック信号CLKiおよび出力クロック信号CLKoを入力とし、DLL回路がロック状態に入った後に、入力クロック信号CLKiおよび出力クロック信号CLKoの位相がずれた場合に、出力クロック信号CLKoの位相に基づいて入力クロック信号CLKiの位相に補正を加え、電圧制御遅延回路14に出力する。

(もっと読む)

遅延制御方法および遅延装置

【課題】遅延装置の回路規模を抑制する。

【解決手段】DLL回路120は、遅延素子122に入力された基準クロックが遅延素子122により1周期分遅延されるように遅延素子122を制御する第1の制御信号CTR1を生成する。遅延素子140は、遅延素子122と同一の構成を有し、外部からのストローブ信号S1を、第2の制御信号CTR2に応じた遅延量の分だけ遅延させる。ストローブ遅延制御回路130は、第1の制御信号CTR1と、遅延素子140による遅延量の期待値とから、遅延素子140に出力する第2の制御信号CTR2を生成する。クロック供給回路110は、遅延素子140に入力されるストローブ信号S1の周波数より高い周波数を有する基準クロックをDLL回路に供する。

(もっと読む)

半導体集積回路

【課題】リアルタイムクロック用の半導体集積回路の消費電力をさらに低減すると共に、生成されたクロック信号を周辺回路においても利用できるようにする。

【解決手段】この半導体集積回路は、外部から供給される電源電圧に基づいて、第1の電源電圧及び第2の電源電圧を生成する定電圧回路と、第2の電源電圧が供給され、発振動作を行うことにより原振クロック信号を生成する発振回路と、第2の電源電圧が供給され、原振クロック信号を分周することにより複数種類の分周クロック信号を生成する分周回路と、第1の電源電圧が供給され、分周回路によって生成される少なくとも1種類の分周クロック信号に基づいて計時情報を管理するロジック回路と、原振クロック信号と所定数の分周クロック信号との内の1つを選択するセレクタ回路と、選択されたクロック信号を出力端子に供給する出力回路とを具備する。

(もっと読む)

分数クロック信号を生成するための技術

回路は、位相検出回路と、クロック信号生成回路と、第1の分周器と、第2の分周器とを含む。位相検出回路は、入力クロック信号をフィードバック信号と比較して、制御信号を生成する。クロック信号生成回路は、制御信号に応答して、周期的出力信号を生成する。第1の分周器は、周期的出力信号の周波数を第1の値によって分割して、第1の分周信号を生成する。第2の分周器は、周期的出力信号の周波数を第2の値によって分割して、第2の分周信号を生成する。第1および第2の分周信号は、異なる時間間隔の間に、フィードバック信号として位相検出回路に経路指定される。  (もっと読む)

(もっと読む)

PLL回路

【課題】ループ帯域幅に変動が起こっても、容易に対応できるPLL回路を提供する。

【解決手段】位相比較回路は、帰還信号と外部より入力される基準信号との位相差を検出してチャージポンプに出力し、さらに帰還信号のみが入力した場合、帰還信号に同期したUP信号のみを出力するUPパルス制御を備えておりチャージポンプにその出力を入力し、チャージポンプの出力が入力したループフィルタの出力は電圧制御発振回路に入力し、さらにループフィルタの出力は比較回路の入力に接続され、比較回路の他の入力には基準電圧が入力し、基準電圧は電圧制御発振回路に入力し、比較回路の出力はラッチ回路に接続され、さらに基準信号が入力されたカウンタ回路の出力がラッチ回路に入力し、チャージポンプはラッチされたカウンタ回路によりカウントされた値に従って電流源を選択する選択手段を備えている。

(もっと読む)

PLL回路および通信用半導体集積回路装置

【課題】スプリアス特性の向上が実現可能なPLL回路およびそれを搭載した通信用半導体集積回路装置を提供する。

【解決手段】例えば、PLL回路を含む高周波ICチップRF_CP3において、PLL回路内に複数の電圧制御発振回路ブロックVCO_BK1〜VCO_BK3を設ける。そして、ループフィルタの一部となる2次のループフィルタFLT_Aを位相検出等を行うシンセサイザブロックSYNに配置し、他の一部となる1次のループフィルタFLT_BをVCO_BK1〜VCO_BK3のそれぞれに配置する。さらに、VCO_BK1〜VCO_BK3のそれぞれにおいては、インダクタL1,L2をRF_CP3の内側でなく外側(外周の一辺)に近くなるような向きにレイアウトする。

(もっと読む)

正確で安定したLC型基準発振器のための方法、システム、および装置

【課題】周波数の安定性およびジッタの要件を満たしつつ、CMOS技術における既存の最適化プロセスの手順に依拠した集積化の解決手法を利用した、温度に対して非依存型のLC型発振器を提供する。

【解決手段】実質的に温度に非依存のLC型発振器は、温度ヌル位相に実質的に等しい位相でタンク発振を生成するLC発振器タンク10を用いて達成される。該温度ヌル位相は、LC型発振器の出力発振の周波数の温度変化に伴う変動が最小化されるときの、LC発振器タンク10の位相である。該LC型発振器はさらに、該LC発振器タンク10に接続されて、該温度ヌル位相に実質的に等しい位相で該LC発振器タンク10を発振させる周波数安定化回路を含む。

(もっと読む)

半導体集積回路及びその制御方法

【課題】本発明は、安定ているクロックを生成するために、DLL回路のスマートパワーダウンモードを具現する半導体集積回路及びその制御方法を提供する。

【解決手段】本発明の半導体集積回路は、スマートパワーダウン信号がイネーブルされると、周期的にイネーブルされるパルス信号であるバッファイネーブル信号を生成するDLL制御手段;及び、バッファイネーブル信号に応じて外部クロックの位相を制御して、出力クロックを生成するDLL回路を含む。

(もっと読む)

41 - 60 / 197

[ Back to top ]