Fターム[5J106KK37]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 目的、効果 (3,441) | IC化,LSI化 (197)

Fターム[5J106KK37]に分類される特許

81 - 100 / 197

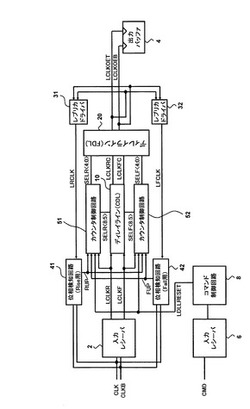

DLL回路及びこれを用いた半導体記憶装置、並びに、データ処理システム

【課題】FDLを調整するカウント信号のビット数を増加させても、高速に遅延量を確定させることが可能なDLL回路を提供する。

【解決手段】相対的に粗い調整ピッチでクロック信号を遅延させるディレイライン(CDL)10と、相対的に細かい調整ピッチでクロック信号を遅延させるディレイライン(FDL)20と、ディレイライン10,20の遅延量を制御する位相検知回路41,42及びカウンタ制御回路51,52とを備える。カウンタ制御回路51,52は、線形探索法によってディレイライン10を制御するとともに、二分探索法によってディレイライン20を制御する。これにより、ディレイライン20を調整するカウント信号のビット数を増加させても、高速に遅延量を確定させることが可能となる。

(もっと読む)

位相ロックループ回路

【課題】回路面積の増大、ピン数の浪費、入出力位相誤差特性の悪化を招くことなく、ループバンド幅の狭い位相ロックループ回路を提供する。

【解決手段】位相ロックループ回路は、フィルタ回路と電圧制御発振回路との間に設けられ、フィルタ回路から供給される第1のアナログ電圧のゲインを1/n(nは1よりも大きい値)に抑制した第2のアナログ電圧を電圧制御発振回路に供給するゲイン抑制回路を備える。ゲイン抑制回路は、第1のアナログ電圧が、その可動範囲の上限電圧もしくは下限電圧に到達している期間は、第2のアナログ電圧の可動範囲の上限電圧が、最大で電圧制御発振回路の入力電圧範囲の上限電圧になるまで一定の比率で平行移動させる、もしくは、第2のアナログ電圧の可動範囲の下限電圧が、最小で電圧制御発振回路の入力電圧範囲の下限電圧になるまで一定の比率で平行移動させる。

(もっと読む)

周波数シンセサイザ

【課題】 低いジッター成分を持つ周波数シンセサイザと電力消耗が最小化された周波数シンセサイザを提供することを課題とする。

【解決手段】基準信号と比較信号が入力されて周波数と位相の差を検出し、これによって、アップ信号、又はダウン信号を発生させる位相比較器と、前記アップ信号又はダウン信号によって、電圧を充電又は放電して制御信号を出力する電荷ポンピング回路と、前記ポンピング回路より出力される制御信号によって、周波数を持つ信号を発振出力信号と出力する電圧制御発振器と、前記電圧制御発振器と連結されて、デューティサイクルを補正するデューティサイクル補正回路と、及び前記発振出力信号の周波数を分割して、前記位相比較器に前記比較信号を提供するフィードバッグディバイダーが含まれる。

(もっと読む)

可変タイミングメモリ

【課題】同期回路装置の設計に於いて、タイミング最適化の作業工程を削減化する。

【解決手段】同期回路装置10内の可変タイミングメモリ20のモジュールは、メモリアレイ21とその入出力メモリ制御回路22,23に加えて、クロック端子Tに入力したクロック信号CLKを遅延する信号線24と、クロック信号CLKをそのまま伝送する信号線25と、両信号線24,25を入力とするセレクタSL1と、メモリライト/リード信号が印加され且つセレクタSL1のセレクト端子と繋がったタイミングモード端子TMTとを有する。セレクタSL1は、メモリライト信号の受信に応じて信号線24を選択し、遅延されたクロック信号を入出力メモリ制御回路22,23に印加する。他方、メモリリード信号の受信に応じてセレクタSL1は信号線25を選択し、クロック信号CLKをそのまま入出力メモリ制御回路22,23に印加する。

(もっと読む)

クロック位相制御装置

【課題】 サンプル毎にトランジスタなどの構成素子の特性が製造誤差などによってばらついたとしても、すべてのサンプルにおいて制御電圧―遅延時間特性がばらつきの影響を受け難い電圧制御遅延手段を有するクロック位相制御装置を提供する。

【解決手段】 高周波クロックが入力されて多相クロックを生成する多相クロック生成手段を有するクロック位相制御装置であって、前記多相クロック生成手段は、電圧制御遅延手段を有し、該電圧制御遅延手段は、入力された制御電圧を電流に変換する電圧電流変換部108を含み、該電圧電流変換部108により変換された電流に比例した制御電流を出力する制御手段と、高周波クロックを前記制御電流に応じた時間だけ遅延させて出力する遅延手段とを備え、前記電圧電流変換部108は、所定の入力電圧範囲において線形の電圧電流変換特性を有している。

(もっと読む)

半導体装置

【課題】高速応答性と動作の安定化を実現したPLL回路を備えた半導体装置を提供する。

【解決手段】低電源電圧VddLで動作する位相比較回路の低振幅信号を夫々高電源電圧で動作するNチャネルMOSFET入力構成の第1差動回路とPチャネルMOSFET入力構成の第2差動回路に入力する。上記第1及び第2差動回路の負荷としてダイオード接続MOSFETとクロスカップル接続のMOSFETを並列構成にして用いる。ゲートに所定のバイアス電圧が供給されたPチャネルMOSFET,NチャネルMOSFETを直列接続する。上記PチャネルMOSFETのソースは、上記第1差動回路の出力信号で制御し、NチャネルMOSFETのソースは、上記第2差動回路の出力信号で制御し、PチャネルMOSFET及びNチャネルMOSFETのドレインからアップ電流又はダウン電流を形成する。

(もっと読む)

位相ロック回路

【課題】位相ロック回路において、電圧制御発振回路や分周回路の性能が設計時よりばらついた場合であっても、電圧制御発振回路が出力する高速クロックを分周回路で良好に分周できるようにして、不良品を低減する。

【解決手段】第1の分周回路4に加えて、この分周回路4よりも動作速度の遅い第2の分周回路5を備える。前記2つの分周回路4、5で分周されたクロックの周波数同士を周波数比較回路6で比較し、第2の分周回路5の分周クロックの周波数よりも第1の分周回路4の分周クロックの周波数の方が速い場合には、VCO発振抑制回路7が電圧制御発振回路3出力クロックFoutの発振周波数を抑制する。

(もっと読む)

分周回路および分周方法

【課題】50%デューティ・サイクルを有するプログラマブル整数クロック分割の回路お

よび方法。

【解決手段】整数分割値により入力信号の周波数を分割する回路および方法。回路は一般

的に(a)入力信号を受信する第1の複数の直列接続された遅延要素および第1の設定可

能なフィードバック・ネットワークを含む第1周波数分割器、(b)入力信号の逆転を受

信する第2の複数の直列接続された遅延要素および第2の設定可能なフィードバック・ネ

ットワークを含む第2周波数分割器、(c)第1および第2周波数分割器の出力を選択し

および/あるいは組み合わせ、周波数分割出力信号を形成するよう構成される設定可能な

論理、および(d)第1および第2の設定可能なフィードバック・ネットワークおよび設

定可能な論理を選択可能な形で設定するよう構成されるプログラマブル回路、を含む。

(もっと読む)

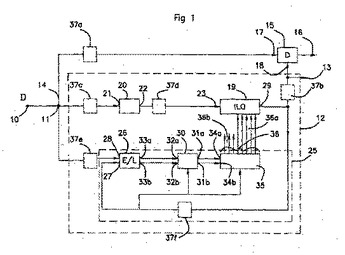

外部制御を必要としないデジタル位相ロックによるクロック抽出装置

本発明は、注入ロック発振器(19)と、デジタル位相検出器(26)を有する位相制御ループ(25)とを備えた、ベースバンドシリアル信号からクロックを抽出する装置に関する。発振器(19)はその周波数の値を制御するデジタル制御入力部(24)を備え、位相制御ループ(25)は、デジタル位相検出器(26)から供給されるデジタル信号の相対値を累算し、発振器(19)用のデジタル形態の制御信号を渡す、カウント回路(30、35)を備える。  (もっと読む)

(もっと読む)

デジタルシンセサイザ

【課題】位相比較器および信号発振器をデジタル化することによって短時間に同期を確立し、同期状態を高精度でしかも高安定に保持することができるデジタルシンセサイザあるいはデジタル同期発振器を提供する。

【解決手段】少なくとも、デジタル位相比較器21と、デジタル制御発振器22と、分周器23から構成する。

【効果】通信システムにおいて同じ周波数であることが必須の2つの入力信号の間で短時間に同期を確立し、入力信号が停止した場合あるいは取去られた場合にも、同期状態を高精度でしかも高安定に保持する。

(もっと読む)

半導体集積回路装置

【課題】製造プロセスなどに依存することなく、安定した高精度なサンプリングクロックを生成する。

【解決手段】遅延段検出回路14は、位相検出部13の位相検出結果から、デジタル可変遅延ライン12の出力信号が基本クロックCLKrefから1周期遅延するバッファの遅延段数を検出する。遅延段数選定部21は、遅延段検出回路14が検出した最新の検出結果と過去の任意の回数分の検出結果との差を算出し、設定された遅延段数以下の際に最新の検出結果を出力する。位相/遅延段数変換部15は、入力された位相遅延の設定信号と使用検出遅延段数保持部22の遅延段数のデータとから、位相遅延に必要なバッファの遅延段数を算出し、遅延設定データとして算出し、デジタル可変遅延ライン111 〜11n は、遅延設定データに基づいて遅延したサンプリング信号を生成する。

(もっと読む)

集積回路装置

【課題】VCOを備える周波数シンセサイザに関し、VCOのf−V特性のばらつきに対処する手法を提案する。

【解決手段】制御電圧V1に応じて発振周波数f1が変化する第1の電圧制御発振器を備え、基準周波数に応じた周波数の信号を発振する第1の周波数シンセサイザと、制御電圧V2に応じて発振周波数f2が変化する第2の電圧制御発振器を備え、前記第1の周波数シンセサイザと同じチップ上に設けられており、前記基準周波数に応じた周波数の信号を発振する第2の周波数シンセサイザと、前記第1の電圧制御発振器の制御電圧V1をモニタし、前記第1の周波数シンセサイザの周波数がロックしているときにモニタされた前記制御電圧V1と基準電圧とを比較し、前記制御電圧V1と前記基準電圧との比較結果に基づいて、前記第2の電圧制御発振器のf2−V2(発振周波数−制御電圧)特性を変化させるコンパレータとを備えることを特徴とする集積回路装置。

(もっと読む)

高周波発振回路、位相同期ループ回路、半導体装置及び通信装置

【課題】より大きなQのインダクタを必要とせず、従来技術に比較してより小さいサイズでかつより高い発振周波数で発振させることができる高周波発振回路を提供する。

【解決手段】帰還型高周波発振回路は、短絡スタブ用伝送線路に接続されたゲートと、発振出力端子に接続されたドレインとを有する電界効果トランジスタ1と、電界効果トランジスタ1のソースに接続されたドレインを有するソース接地の電界効果トランジスタ2とを含み構成され、短絡スタブ用伝送線路11及び電界効果トランジスタ2を帰還回路として発振する。また、電界効果トランジスタ2のゲートと、電界効果トランジスタ1のドレインとの間に帰還用キャパシタを接続する。

(もっと読む)

クロックデータリカバリー回路及び通信装置

【課題】LSI化に適し且つ従来のPLLを用いたのと同等の特性を設定できるシリアルデータインターフェースのCDR回路を提供する。

【解決手段】本発明のCDR回路は、所定周波数のクロックの周期T1をN分割したT2時間ずつずらしたN相のクロックを出力する手段、シリアル転送されたデータをT2時間毎にサンプリングする手段、サンプリングしたデータを周期T1毎に第1のNビットパラレルデータに変換する手段、サンプリングしたデータのデータ変化点を示す第2のNビットパラレルデータに変換する手段、及び、第2のNビットパラレルデータを位相情報入力としてシリアルデータのデータ変化点の略中間位置を示す第3のNビットパラレルデータを出力する手段を有し、第3のNビットパラレルデータが示したビット位置と同じ、第1のNビットパラレルデータのビット位置データを復元データとすることを特徴とする。

(もっと読む)

周波数シンセサイザ及びこれを用いた無線通信装置

【課題】インダクタの使用による面積増大や、製造ばらつきによる歩留まり低下を防ぎつつ、動作周波数範囲を拡大する。

【解決手段】制御電圧によって制御される周波数で発振して発振信号を出力する電圧制御発振器106と;発振信号を分周して第1の分周信号を出力する、自走周波数が制御可能なプリスケーラ107と;第1の分周信号を分周して第2の分周信号を出力するプログラマブル・ディバイダ102と;第2の分周信号の位相と基準クロック信号の位相を比較して位相差に対応する信号を出力する位相比較器108を含み、位相差に対応して制御電圧を生成する制御電圧生成部と;第2の分周信号の周波数と基準クロック信号の周波数を比較して周波数差に対応した信号を出力する周波数比較器103と;周波数差に対応した信号に従って周波数差を最小化するように自走周波数を制御する制御部109と;を具備する。

(もっと読む)

位相補間器

【課題】プロセス条件、電源電圧、温度の変動によらず、微小な位相をプログラマブルに調整できる位相補間器を提供する。

【解決手段】PLL回路のフィードバック信号(FBCLK)に非等間隔なクロックを入力し、PLL回路が本来備える位相合せ機能により、基準信号REFCLKとフィードバック信号FBCLK間に微小な位相差を与え、かつ、アップ、ダウン電流が等しいチャージポンプ(CP)回路を用いてプロセス条件、電源電圧、温度依存性が無い位相差を実現する。

(もっと読む)

無線受信回路および入力妨害波低減回路

【課題】広い周波数領域に渡って妨害波を低減できる入力妨害波低減回路の小型化、およびそのような入力妨害波低減回路を備える無線受信回路の小型化を図る。

【解決手段】受信信号は、トランジスタQ1のゲートに与えられる。トランジスタQ1はトランジスタQA〜QDに接続され、トランジスタQ1、QA〜QDにより4個の増幅器が構成される。トランジスタQA〜QDには、それぞれ調整回路13A〜13Dが接続されている。調整回路13A〜13Dは、LC共振回路であり、その共振周波数は調整信号および微調整信号により調整される。選択信号は、4個の増幅器の中から使用すべき増幅器を選択する。選択された増幅器の利得周波数は、対応する調整回路(13A〜13D)の共振周波数に応じて決まる。選択された増幅器により増幅された信号が出力される。

(もっと読む)

PLL周波数シンセサイザ

【課題】ループフィルタの帯域幅切換時の周波数変動を低減することによって、高速に周波数切換が可能なPLL周波数シンセサイザを提供する。

【解決手段】本発明の一実施形態のPLL周波数シンセサイザ1は、分周器30と、位相比較器40と、チャージポンプ50と、ループフィルタ60と、電圧制御発振器70と、切換スイッチ(切換部80の内部)とを備える。ループフィルタ60は、半導体基板上の基準電位を接地電位とし、切換スイッチは、半導体基板2上に形成され、ループフィルタ60の時定数を切り換えるためにループフィルタ60の中間ノードと半導体基板2上の基準電位とを接続するか否かを切り換える。

(もっと読む)

位相差検出回路、PLL回路、位相差検出方法及び位相差検出プログラム

【課題】 ゼロクロスポイント検出用のハードを用いることなく、位相差の検出機能を実現する。

【解決手段】 位相差検出回路は、検出信号と内部基準信号の位相差を検出するための回路であって、d−q軸変換ユニット5と、1周期全加算ユニット6と、位相差算出ユニット7とを備えている。d−q軸変換ユニット5は、内部基準信号を用いて検出信号をd−q軸変換することで、瞬時値有効分dと瞬時値無効分qとを算出する。1周期全加算ユニット6は、瞬時値有効分dを1周期全加算することで有効分Dを算出して、さらに瞬時値無効分qを1周期全加算することで無効分Qを算出する。位相差算出ユニット7は、有効分Dと無効分Qを用いて位相差を算出する。

(もっと読む)

クロック同期システム及び半導体集積回路

【課題】クロック同期システムにおいて、LSIチップの大規模化・高集積化・高密度化に因る物理現象の複雑化に伴いギガ・ヘルツ級の高い周波数を持つ被分周クロックあるいは分周クロックをLSIチップ全面に渡り長距離配線を分配し且つシグナルインテグリティを確保することが困難である。

【解決手段】基準クロックに基づき逓倍クロックを生成する位相同期回路と、逓倍クロックに基づき分周クロックを生成する分周回路と、基準クロックを分周してフレームパルスを生成するフレームパルス生成回路とを備え、前記分周クロックは前記フレームパルスにより位相同期化がなされることを特徴とする。

(もっと読む)

81 - 100 / 197

[ Back to top ]