Fターム[5J106RR04]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成要素 (681) | ミキサー(ループ内) (26)

Fターム[5J106RR04]に分類される特許

1 - 20 / 26

周波数シンセサイザ及び周波数合成方法

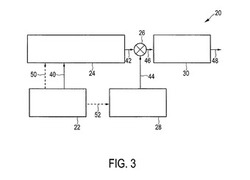

【課題】広い帯域幅、高い周波数分解能及び低い位相ノイズを提供する周波数シンセサイザ及び対応する周波数合成方法を提供する。

【解決手段】第1のリファレンス信号を提供するリファレンス信号源22と、合成周波数出力信号を所定の周波数で生成する周波数信号生成部24と、前記合成周波数出力信号を周波数チューニング信号とミキシングして、ミキシング信号46を出力するミキシング部26と、前記周波数チューニング信号を提供する周波数チューニング部28とを備え、前記周波数チューニング部28は、前記周波数チューニング信号を交互に提供する、第1のサブ周波数チューニング部及び第2のサブ周波数チューニング部を有し、前記ミキシング信号から所望の周波数レンジを選択して周波数シンセサイザ出力信号を出力する周波数選択部30を備えた。

(もっと読む)

PLL周波数シンセサイザ

【課題】改善された位相雑音特性を有するPLL周波数シンセサイザを提供する。

【解決手段】VCO20は、制御電圧VCNTに応じた周波数fVCOで発振する。周波数ミキサ22は、VCO20の出力信号SVCOとローカル周波数fLOを有するローカル信号SLOを周波数ミキシングする。第1フィルタ26は、ミキサ22によるミキシングにより得られる差周波信号SDIFFを抽出する。位相誤差検出部12は、第1フィルタ26により抽出された差周波信号SDIFFと基準周波数fREFを有する基準信号SREFの位相を比較し、位相差に応じた位相誤差信号VPEを生成する。ループフィルタ18は、位相誤差信号VPEをフィルタリングし、制御電圧VCNTを生成する。第2フィルタ28は、ミキサ22によるミキシングにより得られる和周波信号SSUMを抽出し、出力端子OUTから和周波信号SSUMを出力する。

(もっと読む)

周波数シンセサイザ及び周波数シンセサイザの調整方法

【課題】位相雑音を改善すると共に、安定して作動する周波数シンセサイザ等を提供する。

【解決手段】電圧制御発振部から出力された周波数信号と周波数設定部から出力された周波数信号との差分を増幅して得られた差分信号を、前記周波数設定部から出力された周波数信号と直交する検波信号と直交検波して得た両周波数信号の位相差に基づいて前記電圧制御発振部の制御電圧を調整する周波数シンセサイザを立ち上げる際に、前記差分信号を得る差動増幅器から電圧制御発振部を切り離した状態で、第1の位相補正部により予め定めた補正量だけ前記検波信号の位相を補正し、第2の位相補正部により前記検波信号をクロック単位で遅らせて出力することにより、前記周波数設定部よりディジタルの周波数信号が出力された時点から前記差分信号が得られるまでのタイミングと、検波信号が得られるまでのタイミングとをそろえる。

(もっと読む)

基準周波数信号源

【課題】大幅なハードウエア変更を必要とすることなく、異なる基準信号に対応可能な基準周波数信号源を得る。

【解決手段】基準信号と基準信号の周波数fiに応じた制御信号Cとに基づいてクロック信号および局部発振信号を生成する周波数変換回路10と、クロック信号に同期して、周波数制御データに応じた周波数信号を生成するDDS2と、DDS2からの周波数信号に含まれる不要波成分を抑圧するフィルタ3と、局部発振信号と電圧制御発振器の出力信号とを周波数混合するミクサ8と、ミクサ8からの混合信号に含まれる不要波成分を抑圧するフィルタ9と、フィルタ3を介した周波数信号とフィルタ9を介した混合信号との位相差を検出する位相比較器5と、位相比較器5からの位相差信号を濾波するループフィルタ6と、ループフィルタ6を介した位相差信号に応じて出力信号を生成する電圧制御発振器7とを備える。

(もっと読む)

高周波発振源

【課題】3倍波を位相関係により抑圧して2倍波を出力する高周波発振源を得る。

【解決手段】2つの入力端子、第1および第2の入力端子から、同一の周波数を入力することが可能なダブルバランスミクサ21と、ダブルバランスミクサ21の第1および第2の入力端子にそれぞれ接続され、同一の周波数を出力する電圧制御発振器11,12と、電圧制御発振器11,12の位相が同相または逆相となるように制御する位相制御手段31とを備え、同一の周波数を出力する2つの電圧制御発振器11,12に0度または180度の位相差を与えてダブルバランスミクサ21に入力することで、3倍波を位相関係により抑圧して2倍波を出力することが可能となる。

(もっと読む)

周波数シンセサイザ

【課題】設計が容易で、かつノイズ特性を良好にする。

【解決手段】周波数foutの出力信号Soutを生成するVCO5、周波数f1の低周波信号S1を生成する低周波信号生成部3、周波数f2の高周波信号S2を生成する高周波信号生成部4、ミキサ部6、ミキシング信号Smix中の差周波数信号Sdiを通過させる低域フィルタ部7、比較用信号S4を出力する信号処理部10、位相比較部8およびループフィルタ9を備え、信号処理部10は、周波数f2が新たに設定された際に、fout<f2のときには比較用信号S4の出力を停止し、fout≧f2で、かつ差周波数信号Sdiの絶対周波数fdiが低域フィルタ部7のカットオフ周波数fco以上のときには周波数f3(>f1)の基準信号S3を比較用信号S4として出力し、fout≧f2で、かつfdi<fcoのときには差周波数信号Sdiを比較用信号S4として出力する。

(もっと読む)

PLL回路

【課題】PLL回路の不安定状態や位相雑音特性の劣化を回避する。

【解決手段】

発振周波数が電圧制御発振器からのフィードバック信号と外部から入力される基準信号との位相差に応じて制御されるPLL回路において、前記フィードバック信号を分周する分周器と、前記基準信号を逓倍する逓倍器と、前記分周器からの出力信号と前記逓倍器からの出力信号とをミキシングし周波数変換するミキサと、前記ミキサからの出力信号を分周しデジタル分周信号を出力する第一のデジタル分周器と、前記基準信号を分周しデジタル分周信号を出力する第二のデジタル分周器と、前記第一のデジタル分周器からのデジタル分周信号と、前記第二のデジタル分周器からのデジタル分周信号とを、デジタル位相比較する位相比較器と、を備える。

(もっと読む)

複数の同調ループを有する周波数シンセサイザ

【解決手段】複数の同調ループ、例えば微同調ループと粗同調ループ、を有する周波数シンセサイザが述べられる。微同調ループは、制限された同調レンジにわたって動作し、細かい周波数分解能を有し得る。粗同調ループは、広い同調レンジにわたって動作し、粗な周波数分解能を有し得る。微同調ループは、参照周波数の参照信号を受信し、細かいステップで調整可能な第1周波数の微同調信号を生成し得る。粗同調ループは、参照信号を受信し、出力信号と微同調信号とに基づいて第2周波数の微同調信号を生成し得る。第2周波数は、粗なステップ、例えば参照周波数の整数倍で調整可能であり得る。出力周波数は、第1周波数及び第2周波数に基づいて決定され得る。 (もっと読む)

周波数シンセサイザ及び無線送信装置

【課題】VCOの出力帯域を選択設定可能な周波数シンセサイザにおける消費電力を低減すること。

【解決手段】互いに並列に接続されたミキサ111と分周器112とを有する周波数変換回路110を設け、VCO101の周波数帯域選択時に分周器112を用いることにより、VCO101の周波数帯域選択時の位相比較器102の最高動作周波数を低くすることができ、消費電力を低減できる。また、送信時にはミキサ111を用いることにより、送信時のループゲインを下げずに済む。

(もっと読む)

周波数シンセサイザ

【課題】回路規模が小さく、回路構成を簡単にする。

【解決手段】電圧制御発振器19が出力する信号を入力して分周する分周器11、12と、分周器11、12の出力信号を混合する周波数混合器13と、周波数混合器13が出力する2つの周波数の内の一方の周波数の信号を入力して分周する分周器14を、電圧制御発振器19と位相比較器17との間のPLL回路内の帰還ループ中に備える。位相比較器17は、分周器14が出力する信号を一方の入力端に入力し、基準信号発生器16が出力する基準クロック信号を他方の入力端に入力する。ループフィルタ18は、位相比較器17の位相比較結果に基づいた電圧を電圧制御発振器19に与える。電圧制御発振器19は、入力される電圧に対応した周波数で発振する信号を分周器11、12に与える。

(もっと読む)

無線送信回路及びそれを用いた送受信機

【課題】 部品点数を削減でき、小型化に適した移動体通信機用の無線送信回路を提供する。

【解決手段】 従来の移動体通信機で必要とされていたTX,RF,IF周波数帯の3つの発振器のうちRF周波数帯PLLと、IF周波数帯PLLとを1つのPLLシンセサイザSSで兼用し、チップ内で大きな面積を専有する必要な発振器の個数を低減して部品点数を削減する。具体的には、RF周波数帯PLLのVCO21の出力を分周することにより、RF,IF周波数帯で用いる局部発振信号を生成する構成とする。

(もっと読む)

高周波発振源

【課題】長いディレイラインを用いることなく、信号波の位相雑音を低減することができる高周波発振源を提供する。

【解決手段】周波数変換器2と、中心周波数f0の帯域通過フィルタ3と、2分周器4とを直列接続したものを1段の基本構成として、前記基本構成を(N−1)段(N:2以上の整数)直列接続し、前記第1段目の周波数変換器における第1の入力端子及び前記第1段目から第(N−1)段目の周波数変換器における第2の入力端子に接続されてそれぞれに設けられた発振周波数f0の発振器1,1aを備えた高周波発振源。

(もっと読む)

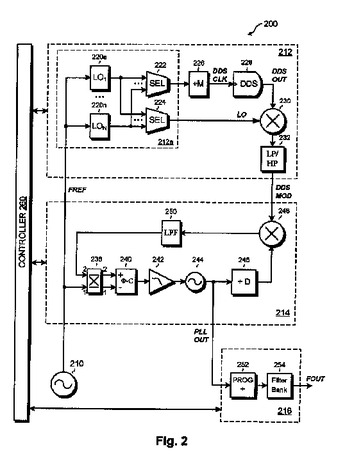

コスト的に有効な低ノイズの単一ループシンセサイザー

低コストで低位相ノイズのマイクロ波シンセサイザーは、DDS変調回路と位相ロックループを含む。DDS変調回路はDDSの出力を高周波数に変調する。位相ロックループはDDS出力をダウンコンバートし、ダウンコンバート信号を比較的低周波数の固定されたリファレンスにロックする。  (もっと読む)

(もっと読む)

周波数シンセサイザ

【課題】 AD変換器への入力レベルが変化したときに、PLL制御が正常に動作しない状況を防止して周波数ずれの発生を防止できる周波数シンセサイザを提供する。

【解決手段】 キャリアリムーブ16と、逆回転ベクトル乗算部17と、位相の時間差検出部18と、加算器19と、位相差の累積加算部20と、ループフィルタ21と、パラメータ出力部25と、振幅情報検出部26と、フィルタ27と、乗算器28とをFPGAで構成し、振幅情報検出部26で検出された振幅情報の値をアンロック検出手段が監視し、当該値が適正範囲内であれば、PLL制御におけるロック(同期)処理を行い、当該値が適正範囲外であれば、PLL制御におけるアンロックを検出するようにした周波数シンセサイザである。

(もっと読む)

PLL周波数シンセサイザ

【課題】低位相雑音特性を満足しつつ任意の周波数の信号を出力可能なPLL周波数シンセサイザを提供することを目的とする。

【解決手段】出力周波数の比較周波数を設定するPLL制御ループ内の混合手段としてサンプリングフェーズディテクタ20を用い、サンプリングフェーズディテクタ20をハーモニックス・ダウンコンバータとして動作させることにより上記課題を解決する。

(もっと読む)

同期および追跡動作モードを有する位相同期ループシステム

実施形態は、位相同期ループ(PLL)回路に関係する。PLLは、所望の周波数で信号を出力する電圧制御発振器を含む。位相検波器が電圧制御発振器からの出力に結合されている。位相検波器は、電圧制御発振器(VCO)からの信号出力の位相を基準信号の位相と比較する。ループフィルタがVCOと位相検波器とに結合されている。VCO信号の位相を基準信号の位相に同期させるために、ループフィルタは同期動作モードを有する。引き続いてループフィルタを追跡動作モードに置くことができ、追跡動作モードはVCO信号の位相を調整して、基準信号の位相を追跡する。 (もっと読む)

自動周波数制御ループ回路

【課題】高い精密度を有しながら周波数を広帯域で発振させることができる自動周波数制御ループ回路を提供すること。

【解決手段】基準周波数を発生させるクロック発振部と、基準周波数を第1分周比で分周する第1分周器、発振周波数を第2分周比で分周する第2分周器、第1分周器によって分周された第1分周周波数と第2分周器によって分周された第2分周周波数との間の位相差を検出する位相検出器、位相差に対応して発振周波数を発生させる電圧制御発振器と、入力周波数と発振周波数に対応して出力周波数を出力する周波数変換器を含む周波数合成部と、出力周波数を設定周波数と比較して誤差を検出する誤差検出器、誤差を積分する積分器と、積分器の積分値に対応する制御信号を計算する演算器を含む復調部とを含み、制御信号に応じて第1分周比及び第2分周比を変更して誤差を補正することを特徴とする。

(もっと読む)

位相制御方法及び位相制御発振装置、送信用アレーアンテナ

【課題】 マイクロ波帯域用の移相器を用いることなく、VCOの出力するマイクロ波帯域の出力信号の位相を制御すること。

【解決手段】 VCO10の出力信号FOUTの位相を制御するために、第1基準信号FRef1を用いて出力信号FOUTをダウンコンバートし、調整対象信号SCOを生成する一方、調整対象信号SCOと同一周波数を有する第2基準信号FRef2を所望とする移相量を示す移相信号SPSに従って移相して第3基準信号FRef3を生成し、調整対象信号SPSの位相と第3基準信号FRef3の位相を一致させるようにしてVCO10を制御するPLLを形成する。これにより、出力信号FOUTよりも低い周波数の信号の位相制御をもって出力信号FOUTの位相制御を行うことができる。

(もっと読む)

送受信機の周波数合成の方法および装置

【課題】受信機参照周波数信号から受信機周波数信号を合成するように構成されるプライマリ周波数シンセサイザを提供し、フラクショナル−N分周を使用することにより受信機周波数信号から送信機周波数信号を合成するように構成されるオフセット周波数シンセサイザを提供することに基づく、送受信機の周波数合成に関する方法および装置である。かかる構成が、要求される受信および送信周波数間の非整数のデュプレックス距離を可能とする。プライマリ周波数シンセサイザは、フラクショナル−N周波数シンセサイザとして作動されることもできる。これは受信機周波数信号が受信機参照周波数信号との非整数の関係を有することもできることを意味する。フラクショナル−N周波数合成と共に作動するようにプライマリおよびオフセット周波数シンセサイザを構成することが、プライマリおよびセカンダリ周波数シンセサイザの独立した周波数の調整/最適化を許容する。 (もっと読む)

サンプラ回路

【課題】 サンプラ回路の入力周波数信号について、広帯域にわたって周波数変換損失を良好な特性に維持することができるサンプラ回路を実現する。

【解決手段】 ローカル信号の高調波で所定のパルス幅を有するサンプル周波数信号を生成する第1回路と、前記サンプル周波数信号により入力周波数信号をサンプルし、前記サンプル周波数信号と前記入力周波数信号の差分周波数信号を出力する第2回路を有するサンプラ回路において、前記パルス幅を変更するパルス幅変更手段を備える。

(もっと読む)

1 - 20 / 26

[ Back to top ]