Fターム[5J500AH38]の内容

Fターム[5J500AH38]の下位に属するFターム

電子的スイッチング素子 (871)

連動スイツチ (27)

リレー (16)

Fターム[5J500AH38]に分類される特許

81 - 100 / 999

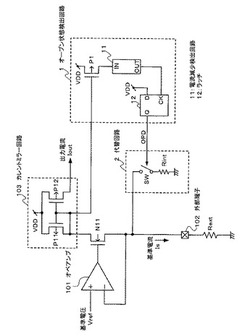

定電流回路

【課題】外付け抵抗の接続に不良が発生しても、正常な出力電流を得ることのできる定電流回路を提供する。

【解決手段】実施形態の定電流回路は、半導体集積回路に搭載され、出力電流を生成するカレントミラー回路103を備え、外部端子102に外付け抵抗Rextを接続することにより、カレントミラー回路103へ供給する基準電流Isが生成される定電流回路であって、オープン状態検出回路1が、外部端子102がオープン状態となったことを検出すると、代替回路2が、基準電流Isに相当する代替電流Iaをカレントミラー回路103へ供給する。

(もっと読む)

容量性負荷駆動回路

【課題】容量性負荷の駆動信号にキャリアリップルが重畳することを回避する。

【解決手段】駆動波形信号をパルス変調して変調信号を生成し、電力増幅した後に平滑フィルターを通すことによって生成した駆動信号を容量性負荷に印加する。また、駆動信号に位相進み補償を行って帰還信号を生成し、駆動波形信号に負帰還させる。平滑フィルターと容量性負荷とは取り替え可能な配線によって接続されている。平滑フィルターと容量性負荷とを配線によって接続すると、その配線に関する配線情報が取得され、そして、配線情報に応じたキャリア周波数でパルス変調が行われる。こうすれば、配線に応じたキャリア周波数でパルス変調されるので、駆動信号にキャリアリップルが重畳することを回避することができる。

(もっと読む)

チョッパ増幅とデジタル変換の複合回路

【課題】チョッパアンプの出力電圧には所定時間毎に反転する増幅後電圧(Vs)または所定時間毎に反転するオフセット電圧が含まれており、出力電圧から増幅後電圧(Vs)のみを取出してデジタル変換する必要があり、回路が大規模化する。

【解決手段】チョッパアンプとデジタル変換回路を構成する比較回路の間に伝達回路を設ける。伝達回路は、重畳電圧(V1)とデジタル値から変換したアナログ電圧(Vd)を入力し、2種類の電圧(第1出力電圧(VI),第2出力電圧(VII))を出力する。第1出力電圧(VI)と第2出力電圧(VII)の差は、増幅後電圧(Vs)とアナログ電圧(Vd)の差に比例している。この結果、比較回路で増幅後電圧(Vs)とアナログ電圧(Vd)の大小関係を判別することができ、カウンタ回路のカウント値をアップまたはダウンさせ、カウント値を増幅後電圧(Vs)に追従させることができる。

(もっと読む)

低歪み可変利得増幅器(VGA)

【課題】非対称な信号の非対称性を補正する。

【解決手段】第1抵抗は、増幅器の入力ノード及び出力ノードの間に接続され、入力ノードは非対称信号を受信する。第2抵抗は、増幅器の入力ノードに接続される。第2抵抗は、線形レジスタを含む。第3抵抗は、第2抵抗に接続される。出力ノードにおける非対称信号を補正するべく、増幅器によって提供される非対称補正量を調整するように第3抵抗を変化させる。非対称補正量は、第1抵抗及び第2抵抗と第3抵抗との組み合わせの関数である。

(もっと読む)

利得切換型増幅器およびそれを用いたオーディオ機器

【課題】ポップノイズの発生を、再生時の音声品質を維持しつつ、防ぐ。

【解決手段】オペアンプ回路1の出力端子からの出力信号を、オペアンプ回路1の反転入力端子にフィードバックするフィードバック回路2を具備し、フィードバック回路2でフィードバックする帰還電圧を減衰することにより利得切換を行い、オペアンプ回路1に入力された入力信号の出力レベル調整を行う利得切換型増幅器において、オペアンプ回路1の非反転入力端子に、入力信号を減衰して入力するアッテネータ回路3を設け、このアッテネータ回路3の減衰率の設定とフィードバック回路2の減衰率の設定の組み合わせにより、信号出力レベルの切換分解能を上げることで、例えば音声出力レベルを連続的に変化させることを可能とし、ポップノイズの発生を防ぐ。

(もっと読む)

ドライバモジュール用の突入電流リミッタ回路

【課題】リミッタ回路が出力電流(突入電流)を制御して電流変化の割合を制限し、上流ドライバモジュールを保護する。

【解決手段】リミッタ回路が入力と出力を有する電圧レールを含み、この入力は印加入力電圧を受ける。切替装置は、電圧レールと電気的に連通し、電圧レールの出力を流れる電流を選択的に制御する。リミッタコンデンサは、電圧レールの入力及び切替装置と電気的に連通し、入力と電気接地との間で、切替装置と並列接続で電気的に連通する。第1の抵抗器は、リミッタコンデンサと電気接地との間に配置され、抵抗器のインピーダンスとリミッタコンデンサにより、リミッタコンデンサを充電するための時定数が定義される。このリミッタコンデンサの時定数により、切替装置に印加される電圧と、電圧レールの出力を流れる電流が制御される。

(もっと読む)

基準電圧源回路

【課題】抵抗を使用せずナノアンペアレベルの電流で動作可能なBGR回路及びサブBGR回路を提供する。

【解決手段】電流源回路10は所定の電流を発生し、電圧発生回路20は、PNPバイポーラトランジスタQ1を含み、電流源回路10からの電流に基づいて、半導体素子のバンドギャップ電圧に基づいた負の温度特性を有するPNPバイポーラトランジスタQ1のベースエミッタ間電圧VBEを出力し、温度特性制御回路30は、電流源回路10からの電流に基づいてベースエミッタ間電圧VBEの負の温度特性を実質的に相殺する正の温度特性を有する電圧VGGを発生し、ベースエミッタ間電圧VBEに電圧VGGを加算して出力電圧VREF1を出力する。

(もっと読む)

電力増幅装置

【課題】複数段構成による電力増幅器において、前段の増幅器が故障したときにも対応可能な増幅装置を提供する。

【解決手段】信号を入力する前段電力増幅器12と、該増幅器の出力電力を並列に増幅する複数の電力増幅器16a、16b、16c、16dで構成される後段電力増幅器と、後段電力増幅器に分配する分配器14と、前記後段電力増幅器の出力電力を合成する合成器18とを有し、前段後段の全ての増幅器12,16a、16b、16c、16dはいずれも同じ構成とする。前段増幅器12が故障したときは接続を変えて後段の増幅器16a、16b、16c、16dの一つを前段の増幅器にとり変える。前記後段電力増幅器の一つを前記前段電力増幅器に代える操作はコネクタ接続の変更により行う。

(もっと読む)

スイッチトキャパシタ回路

【課題】エスティメートフェーズとレベルシフトフェーズとで、レベルシフト用コンデンサCca、Ccbを、全差動演算増幅器AMP2の出力のサンプルと全差動演算増幅器のAMP2位相補償とに兼用する方式のCLS技術を適用したスイッチトキャパシタ回路100において、入出力コモン電圧の変動を抑止するこれにより、同相入力レンジの大きさに関する要求水準を低減させて、十分な低電圧化が図られて消費電力が低減されたスイッチトキャパシタ回路を実現する。

【解決手段】エスティメートフェーズからレベルシフトフェーズへの移行に際して、複数の全差動演算増幅器AMP1、AMP2のうちの初段の全差動演算増幅器および最後段の全差動演算増幅器の各出力コモン電圧が等しくなるように保持する出力コモン電圧保持回路110を備えた。

(もっと読む)

光受信装置,光局側装置および光ネットワークシステム

【課題】立ち上がり時間短縮と同符号連続耐力の確保とを両立する。

【解決手段】バースト光信号を受光し、バースト光信号の受光レベルに応じた信号を出力する受光部2と、受光部2から出力された信号について増幅出力する増幅部3と、バースト光信号のプリアンブル領域において、増幅部3から出力される増幅後の信号の平均値相当の成分を受光部から出力された信号の直流成分として取り出し、取り出した直流成分を受光部から出力された信号から除去する応答時定数可変の直流成分除去部4a,4bと、前記バースト光信号の立ち上がりを示す信号に基づいて応答時定数を増加させる制御を行なう応答時定数制御部5と、をそなえる。

(もっと読む)

半導体集積回路装置

【課題】アンプの動作周波数に依存性を有するバイアス電流を供給することにより、消費電流を大幅に低減する。

【解決手段】DLL回路2は、入力されたクロック信号CKに基づいて、該クロック信号CKの周波数に比例関係を持つ制御電圧VCNTLを生成する。トランスリニア回路3は、DLL回路2が生成した制御電圧VCNTLに基づいて、クロック信号CKの周波数の2乗の関係を持つ電流を生成する。カレントミラー回路5は、トランスリニア回路3が生成した電流からアンプ電流を生成し、アンプ4のテール電流として該アンプ4に供給する。

(もっと読む)

バースト受信機,バースト受信制御方法、およびシステム

【課題】 ONU毎にレーザ立上り時間Tonが異なるバースト信号を受信しても、利得切替を確実にバーストプリアンブル期間に制限し、BER劣化を防ぐことを目的とする。

【解決手段】 OLTは、バースト信号毎にトランスインピーダンスアンプの利得切替許容期間を設定し、常に最適な利得切替許容期間となるよう制御する。具体的には、ONU登録時にONUから通知されたTonとONU識別子の対応を保持し、受信するバースト信号毎にTon時間に基づいて適切な切替許可時間Tselを決定し、トランスインピーダンスアンプの利得切替を許容する期間を設定する。

(もっと読む)

高周波電力増幅器

【課題】高周波電力増幅器と方向性結合器を多層基板内に一体化した高周波モジュールであって、小型、低コスト、高性能な高周波モジュール及び、高周波モジュールを搭載することで、小型化、低コスト化が可能な無線装置を提供する。

【解決手段】多層基板と前記多層基板の上層部で構成された高周波電力増幅器と前記多層基板の内層の上下2層を用いた方向性結合器と、前記高周波電力増幅器と前記方向性結合器の間にある内層のグランドパターンと、前記内層のグランドパターンと裏面のグランドパターン間に設けられている前記高周波電力増幅器用の多数のサーマルビアが方向性結合器と同じ層にある前記高周波電力増幅器用のバイアスラインとの間に設けられている高周波モジュールとする。このことによって小型、低コスト、高性能な高周波モジュールが実現出来る。

(もっと読む)

通信装置および歪補償方法

【課題】DPD方式の歪補償機能を有する簡易な構成の通信装置および当該通信装置の歪補償方法を提供することである。

【解決手段】サーキュレータ12は、第1、第2、第3の端子を備える、第1の端子は、送信信号処理部201からの送信信号を受け、第2の端子は、送受信アンテナ10からの受信信号を受けるとともに、送受信アンテナ10へ第1の端子から入力された送信信号を出力し、第3の端子は、第2の端子から入力された受信信号を出力し、かつ第1の端子から入力された送信信号が漏れ出した信号をフィードバック信号として出力する。受信信号およびフィードバック信号処理部204は、受信信号に対して増幅を行なう低雑音増幅器26を含むとともに、受信信号およびフィードバック信号に対して無線周波波数帯から中間周波数帯への周波数変換を行なう。フィードバック信号は、さらに歪補償部56に入力される。

(もっと読む)

保護装置、相補型保護装置、信号出力装置、ラッチアップ阻止方法、及びプログラム

【課題】保護対象のスイッチング素子のラッチアップを阻止することができる保護装置、相補型保護装置、信号出力装置及びプログラムを提供する。

【解決手段】PMOSトランジスタ106に対して過電流が流れていない状態でPMOSトランジスタ106を非導通状態にする場合、PMOSトランジスタ20A及びPMOSトランジスタ22の各々を導通状態とするように制御し、PMOSトランジスタ106に対して過電流が流れている状態でPMOSトランジスタ106を非道通状態にする場合、PMOSトランジスタ20Aを導通状態にすると共にPMOSトランジスタ22を非導通状態にするように制御する。

(もっと読む)

増幅回路システム

【課題】増幅回路のゲイン精度を向上することのできる増幅回路システムの提供を図る。

【解決手段】ゲイン設定抵抗Ra,Rbによりゲインが設定される増幅回路1と、該増幅回路の後段に設けられた半導体集積回路2と、を有する増幅回路システムであって、前記ゲイン設定抵抗Ra,Rbが、前記半導体集積回路2の内部に形成されているように構成する。

(もっと読む)

増幅回路

【課題】適切な利得制御を行うことが可能な増幅回路を提供すること。

【解決手段】入力信号Itiaを増幅する増幅器10と、増幅器10の出力信号Vtiaを平均化して制御信号Vagcを生成し、時定数τs1と、τs1より大きいτl1とで時定数を切り換え可能な制御回路20と、Vagcに基づいて時定数制御信号Vsw0を生成する時定数制御回路30と、Vsw0を遅延させる遅延回路35と、制御回路20に接続されたノードN1を有し、遅延回路35に遅延されたVsw1に基づく信号の入力に応じて、Vtiaの電位のコピー電位をノードN1に出力し、時定数をτl1からτs1に切り換え、ノードN1をフローティングとし、時定数をτs1からτl1に切り換えるスイッチ回路200と、コピー電位出力までの時間を速めるアンプ300又は分流回路400と、Vagcに基づいてItiaをバイパスするバイパス回路40と、を具備する増幅回路。

(もっと読む)

増幅器及びアンプ制御方法

【課題】 各アンテナへ供給可能な最大電力の配分をフレキシブルに変更可能な送信機及びアンプ制御方法を提供する。

【解決手段】 送信機は、第1乃至第3のアンプと、入力側及び出力側スイッチ部と、切替制御部とを具備する。第1のアンプは、第1のアンテナの第1の接続経路に接続される。第2のアンプは、第2のアンテナの第2の接続経路に接続される。入力側スイッチ部は、第1のアンプと第3のアンプとの間を接続する第1の入力スイッチと、第2のアンプと第3のアンプとの間を接続する第2の入力スイッチとを有する。出力側スイッチ部は、第1のアンプと第3のアンプとの間を接続する第1の出力スイッチと、第2のアンプと第3のアンプとの間を接続する第2の出力スイッチとを有する。切替制御部は、入力切替信号及び出力切替信号を同期して入力側スイッチ部及び出力側スイッチ部へ出力し、第3のアンプが第1及び第2のアンプのいずれに接続するか制御する。

(もっと読む)

高周波電力増幅器

【課題】部品の使用点数を減少させて実装面積を縮小すると共に、信号のスイッチ通過による通過損失を抑制する高周波電力増幅器を提供する。

【解決手段】整合回路23,25,26,27と少なくとも1以上の高周波電力増幅素子24とを有する高周波電力増幅器21であって、前記整合回路は2つのリアクタンス素子37,38,39,40が直列に接続された第1の整合ライン41及び第2の整合ライン42が並列に接続された回路と、前記第1の整合ラインの前記リアクタンス素子間及び前記第2の整合ラインの前記リアクタンス素子間とグランドに接続され何れか一方を選択可能なスイッチ43とを有し、該スイッチを切替えることで前記第1の整合ライン及び前記第2の整合ラインの何れか一方に信号を伝搬させ、他方を前記グランドに接続させる。

(もっと読む)

双方向中継器

【課題】中継器内でループ発振の発生を抑制することができ、ひいては、動作を安定させることができる双方向中継器を得る。

【解決手段】入力されたディジタル信号を等化する等化器11a、11bと、等化器11a、11bの出力を増幅する可変利得増幅器12a、12bと、可変利得増幅器12a、12bの出力をオンオフするオンオフ回路13a、13bと、等化器11a、11bから出力されるディジタル信号のレベルを検出するレベル検出回路15a、15bと、レベル検出回路15a、15bによって検出された信号レベルと閾値電圧Vthとを比較し、信号レベルが閾値電圧Vthよりも小さい場合には、オンオフ回路13a、13bをオフする制御信号を出力するオンオフ制御回路16a、16bとを設けた。

(もっと読む)

81 - 100 / 999

[ Back to top ]