Fターム[5J500AH38]の内容

Fターム[5J500AH38]の下位に属するFターム

電子的スイッチング素子 (871)

連動スイツチ (27)

リレー (16)

Fターム[5J500AH38]に分類される特許

21 - 40 / 999

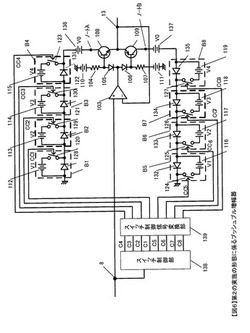

電源回路

【課題】 広帯域無線通信を行う送信機に用いられ、電源変換効率を向上させることができる電源回路を提供する。

【解決手段】 入力信号をプッシュプル増幅方式で増幅するプッシュプル増幅部と、制御信号によりプッシュプル増幅部に提供する電源電圧の電圧レベルを複数の電源112〜115、116〜119の選択接続によって可変とする可変電源部と、制御信号として、入力信号に基づいて電源電圧の電圧レベルを制御するために複数の電源を選択する選択信号C1〜C8を出力するスイッチ制御部138と、可変電源部における複数の電源112〜115、116〜119の負荷が一定となるよう、選択信号による電源の選択先を変更するスイッチ制御信号変換部139とを備えた電源回路としている。

(もっと読む)

増幅システム

【課題】プラズマ生成時の負荷変動に高速に対応すると共に、自動インピーダンス制御回路の長寿命化を図ることが可能な増幅システムを提供する。

【解決手段】プラズマの生成によりインピーダンスが変動する負荷と接続する増幅システムは、入力線路、第1及び第2の増幅器、出力線路、接続線路及びインピーダンス制御回路を具備する。入力線路、出力線路及び接続線路の電気長は、駆動前調整により予め設定される。インピーダンス制御回路は、駆動前調整において、入力から前記負荷側を見たインピーダンスが第1のインピーダンスと等しくなるように制御する。駆動中には、第1の増幅器は、プラズマ生成前後において第1のインピーダンスを目標として信号を増幅する。第2の増幅器は、プラズマ生成前には増幅機能をオフとし、プラズマ生成後には第1のインピーダンスを目標として信号を増幅する。

(もっと読む)

増幅装置、無線通信装置、及び負荷変動器

【課題】新規な負荷変動器を提供する。

【解決手段】 可変位相器を用いた負荷変動器3001であって、前記可変位相器は、信号が入力される第1ポートP1と、信号が出力される第2ポートP2と、第1可変インピーダンス3021が接続される第3ポートP3と、第2可変インピーダンス3022が接続される第4ポートP4と、を備えている。可変位相器は、第1ポートP1から入力された信号の位相が第1可変インピーダンス2021及び第2可変インピーダンス3022によって変化するものである。第1可変インピーダンス3021及び第2可変インピーダンス3022は、前記第1可変インピーダンスと第2可変インピーダンスとの間のインピーダンス差を調整可能に設けられている。インピーダンス差の調整によって、第1ポートP1及び第2ポートP2間の負荷が変動する。

(もっと読む)

高周波電力増幅装置

【課題】出力電力を高効率で伝達可能な高周波電力増幅装置を提供する。

【解決手段】例えば、差動増幅器AD101,AD102と、その各出力インピーダンスを整合するトランスフォーマTR101を備え、AD101の差動出力ノード間にインダクタL101、スイッチS101、インダクタL102を直列に接続する。AD102が動作状態、AD101が非動作状態の場合には、S101がオンに制御される。この場合、AD101に含まれる差動対のトランジスタのオフ容量を踏まえて1次コイルLD111/LD112の両端から見たAD101側のインピーダンスが高インピーダンス状態(並列共振状態)となり、等価的に、AD102の動作に際してLD111/LD112は影響しなくなる。

(もっと読む)

電力増幅回路

【課題】簡単な構成により利得を下げずに効率を向上させることができる電力増幅回路を得る。

【解決手段】基板1上に、熱感応式分配器2、電力増幅素子3a,3b、及び合成器4が設けられている。熱感応式分配器2は、入力信号を最大で2つに分配する。電力増幅素子3a,3bは、分配された入力信号をそれぞれ電力増幅する。合成器4は、電力増幅素子3a,3bの出力信号を1つに合成する。電力増幅素子3a,3bで発生した熱が、基板1を介して熱感応式分配器2に伝わる。熱感応式分配器2は、温度が高くなるほど多くの電力増幅素子3a,3bに入力信号を分配する。

(もっと読む)

リミッター回路

【課題】接続される低雑音増幅器の破壊を防止すると共に、この増幅器の飽和の範囲を狭くし正常動作の範囲を広くすることが可能なリミッター回路を提供すること。

【解決手段】一例のリミッター回路は、高周波入力端子に接続され、一定の飽和入力電力範囲を有する低雑音増幅器の入力端子と接地との間に接続されたPINダイオードと、前記低雑音増幅器の入力端子に一端を接続され他端は接地される、所定周波数の1/4波長の長さの伝送線路と、前記低雑音増幅器の入力端子に前記飽和入力電力範囲に入る信号が入力されるときに、前記伝送線路の他端と接地との間に、直列接続される電力設定用抵抗器及び定電圧電源を接続し、前記低雑音増幅器の入力端子に入る信号を、この範囲より電力の小さい正常入力電力範囲の信号に下げて前記低雑音増幅器の入力端子に入力する手段と、を有する。

(もっと読む)

F級増幅回路及びこれを用いた送信装置

【課題】基本波周波数の異なる複数の入力信号が入力する場合でも、各基本周波数に応じた高周波処理が行えるようにする。

【解決手段】 基本角周波数の異なる複数の信号をF級増幅し、該基本角周波数の信号成分及び、その高調波の信号成分を含んだ信号を出力するF級増幅器と、F級増幅器の後段に設けられて、当該F級増幅器に寄生する寄生回路のインピーダンスを取り込んで回路設定されることにより、信号の直流成分及び偶数次高調波の信号成分に対しては短絡状態とし、奇数次高調波の信号成分に対しては開放状態となる高調波処理部と、高調波処理部の後段に設けられて、高調波の信号成分に対しては短絡状態にする短絡部と、を備える。

(もっと読む)

光信号受信回路

【課題】耐ノイズ性を高めつつ、ノイズ光を誤検知しても消費電力を抑えることができる光信号受信回路を提供する。

【解決手段】光信号受信回路10は、光信号を受信して電流信号を出力するフォトダイオードPDと、復調信号を出力する信号処理回路20と、信号処理回路20の電流源を制御する電流源制御回路30とを備えている。電流源制御回路30は、フォトダイオードPDからの電流信号に応じて光信号を検出した場合に、光信号検出信号を出力する第1の制御回路32と、光信号検出信号に基づいて信号処理回路20のアクティブ型のバンドパスフィルタである第1のBPF回路23へバイアス電流を供給する第1の電流源回路33と、第1のBPF回路23からの信号でキャリア成分を検出した場合に、キャリア検出信号を出力する第2の制御回路35と、キャリア検出信号に基づいて信号処理回路20へバイアス電流を供給する第2の電流源回路36とを備えている。

(もっと読む)

可変調整精度を有する増幅器回路

【課題】 増幅器回路の可変精度の調整を実現するシステム及び方法を提供する。

【解決手段】 本開示の一態様によると、システムは、増幅器の利得を離散的な利得レベルに設定する複数の調整段を有する増幅器を有する。特定の実施形態では、調整段は直列に接続され、調整段の各々は、スイッチに並列に接続された抵抗器を有し、該スイッチはオフにされ、増幅器に利得を隣接する利得レベルに設定させる。特定の実施形態では、複数の利得レベルのうちの隣接する各々間の利得の差は、低い利得レベルより高い利得レベルにおいて大きい。

(もっと読む)

ソースフォロア回路

【課題】電流源側の駆動能力の大幅な改善を図り、回路の消費電力やエリアの大幅な削減を図るようにしたソースフォロア回路の提供。

【解決手段】この発明は、入力電圧を受けるMOSトランジスタM1と、MOSトランジスタM1とカスコード接続される電流源10とを備えている。電流源10は、MOSトランジスタM1とカスコード接続されるMOSトランジスタM2と、MOSトランジスタM1とMOSトランジスタM2との共通接続部と、MOSトランジスタM2のゲートとの間に接続されるコンデンサC1と、MOSトランジスタM2のバイアスを印加する経路上に配置される抵抗R1とを備えている。

(もっと読む)

出力回路

【課題】2つの出力信号間のタイミングのずれを低減すること。

【解決手段】入力信号IN,XINはトランジスタM1,M2のゲートに供給される。トランジスタM1のドレインはトランジスタM3のドレインとトランジスタM4のゲートに接続され、トランジスタM2のドレインはトランジスタM3のゲートとトランジスタM4のドレインに接続される。また、トランジスタM1,M2のドレインは差動対のトランジスタM11,M12のゲートに接続される。トランジスタM3,M4のソースには、ゲートにバイアス電圧VBが供給されるトランジスタM5が接続される。トランジスタM11,M12のソースには、ゲートにバイアス電圧VBが供給されるトランジスタM13が接続される。

(もっと読む)

信号平均化回路

【課題】信号の平均化値のずれを抑制した信号平均化回路を提供する。

【解決手段】キャパシタCa1の正端子に接続され、キャパシタCa1への信号の入力を制御するスイッチング素子S9と、キャパシタCa2の正端子に接続され、キャパシタCa2への信号の入力を制御するスイッチング素子S10と、キャパシタCa1とキャパシタCa2の正端子同士とを接続する平均化スイッチ素子S13と、を備え、パワーオフ期間後にキャパシタCa1に信号を入力することにより充電を行うプリチャージ期間と、プリチャージ期間後に、キャパシタCa2に信号を入力することにより充電を行う第1サンプリング期間と、第1サンプリング期間後にキャパシタCa1に信号を入力することにより再充電を行う第2サンプリング期間と、前記第2サンプリング期間後にキャパシタCa1,Ca2の正端子同士を接続した状態とする平均化期間と、を設ける。

(もっと読む)

増幅回路、ヘッド駆動回路、及び、液体噴射装置

【課題】増幅される波形の精度を高めつつ省電力を図ること。

【解決手段】入力信号を増幅信号に増幅する増幅回路であって、前記入力信号と前記増幅信号との差分に応じて密度変調した密度変調パルスを出力するパルス密度変調部と、前記密度変調パルスの出力を前記差分に応じて遅延させる遅延回路と、前記増幅のための電力を供給する電力供給部と、前記遅延回路から出力されたパルスに応じて、前記電力供給部からの電力供給のスイッチを切り替えて前記増幅信号を出力するスイッチ部と、を備える増幅回路。

(もっと読む)

増幅回路、ヘッド駆動回路、及び、液体噴射装置

【課題】電力増幅を行うに際し省電力化を図ること。

【解決手段】入力信号を増幅信号に増幅する増幅回路であって、前記入力信号と前記増幅信号との差分に応じて密度変調された密度変調パルスを出力するパルス密度変調部と、前記密度変調パルスの出力を前記入力信号に応じて遅延させる遅延回路と、前記増幅のための電源を供給する電源供給部と、前記遅延回路から出力されたパルスに応じて、前記電源供給部からの電源供給のスイッチを切り替えて前記増幅信号を出力するスイッチ部と、を備える増幅回路。

(もっと読む)

増幅器

【課題】増幅器の出力雑音電圧を抑制する。

【解決手段】正転入力電圧と反転入力電圧の差分を増幅する差動入力回路1と、差動入力回路1の出力信号を増幅して出力端子に出力する出力回路2と、差動入力回路1の電流源MP3と出力回路2の電流源MP4にバイアス電圧を出力するバイアス回路5を備えた増幅器である。差動入力回路1の正転入力電圧と反転入力電圧が共に接地電圧のときに出力端子に現れる出力雑音電圧を検出し、該雑音電圧のレベルが高いほど、バイアス回路5が、電流源MP3,MP4の電流を増大させるバイアス電圧を出力するようにした。

(もっと読む)

オフセット補正装置、及び補正方法

【課題】オフセット電圧をより高精度に補正すること。

【解決手段】オフセット補正装置は、所定の入力信号と、所定ビット前に入力された入力信号に基づいた信号と、を加算する加算手段と、加算手段により加算された信号に対してオフセット補正を行うオフセット補正手段と、オフセット補正手段により補正された信号のレベルを判定し、該判定結果を加算手段に対して出力する判定手段と、判定手段による判定結果に基づいて、オフセット補正手段を制御するオフセット補正制御手段と、判定手段による判定結果を加算手段に対して出力させる場合と遮断する場合とに切替える切替手段と、を備えている。

(もっと読む)

バイアス制御回路、バイアス制御方法、増幅器、および、送信装置

【課題】入力信号を増幅する増幅器が負のバイアスで動作する場合であっても、入力信号がない間の消費電力を低減することが可能なバイアス制御回路を提供すること。

【解決手段】入力信号を増幅する増幅素子2に増幅作用を発生させる第1のバイアスを、増幅素子2に印加するか否かを切り替える第1のスイッチ部11と、第1のバイアスより低い第2のバイアスを増幅素子2に印加するか否かを切り替える第2のスイッチ部12と、入力信号の有無を表す検出信号に基づいて、入力信号が有るときには第1のスイッチ部11をオンにするとともに第2のスイッチ部12をオフにするよう制御し、入力信号が無いときには第1のスイッチ部11をオフにするとともに第2のスイッチ部12をオンにするよう制御する切替部13を備える。

(もっと読む)

受光増幅回路及びそれを用いた光ピックアップ装置

【課題】光ディスクの高倍速化により高い周波数応答特性が必要な場合においても、RF信号成分の信号振幅を低下させない受光増幅回路を提供することを目的とする。

【解決手段】入力された光電流を電圧に変換するとともに、変換した電圧のうち第1カットオフ周波数より低い周波数に対応する電圧のみを出力する電流電圧変換アンプ102と、電流電圧変換アンプ102の後段に接続され、電流電圧変換アンプ102から出力された電圧のうち第2カットオフ周波数より低い周波数に対応する電圧のみを出力するCRローパスフィルタ回路103と、CRローパスフィルタ回路103の後段に接続され、CRローパスフィルタ回路103から出力された電圧を増幅する電圧増幅アンプ104と、少なくとも電圧増幅アンプ104と接続され、電圧増幅アンプ104から出力された電圧を加算増幅するRF増幅加算アンプ105と、を備える。

(もっと読む)

電力増幅器

【課題】素子ばらつきや周波数特性に対して鈍感であり低損失な電力増幅器を得る。

【解決手段】入力端子INから入力した入力信号を増幅素子Tr1が増幅する。増幅素子Tr1の出力信号を増幅素子Tr2が増幅する。増幅素子Tr2の出力信号は出力端子OUTから出力される。増幅素子Tr2の出力と出力端子OUTとの間に整合回路M3a,M3bが接続されている。増幅素子Tr1の出力と増幅素子Tr2の入力との間にスイッチSW1が接続されている。増幅素子Tr1の出力にスイッチSW2の一端が接続されている。整合回路M3a,M3bは、増幅素子Tr2の出力と接地点との間に直列に接続されたインダクタL5及びキャパシタC1を有する。インダクタL5とキャパシタC1を接続する接続点Xに、スイッチSW2の他端が接続されている。

(もっと読む)

増幅回路および窒化物半導体装置

【課題】大電力入力時に、出力電力の低下またはゲインの低下を抑制し、かつドレインアイドル電流のドリフトが生じた場合に、ゲインの低下またはひずみ特性の劣化を抑制すること。

【解決手段】Si基板またはSiC基板と前記Si基板またはSiC基板上に形成された窒化物半導体層とを有し、かつ高周波信号がゲート端子に入力されるFET10からなるパワーアンプ11と、前記パワーアンプのドレインアイドル電流を検出する検出部12と、前記検出されたドレインアイドル電流が所定値より小さい場合は、前記ドレインアイドル電流に応じたゲートバイアス電圧を前記パワーアンプのゲート端子に出力し、前記検出されたドレインアイドル電流が所定値以上の場合は、固定値のゲートバイアス電圧を前記パワーアンプのゲート端子に出力する制御部14と、を具備する増幅回路

(もっと読む)

21 - 40 / 999

[ Back to top ]