Fターム[5J500AK02]の内容

Fターム[5J500AK02]に分類される特許

141 - 160 / 1,173

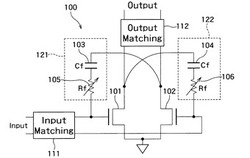

高周波差動増幅回路

【課題】安定性が高く、かつ高い利得を有する高周波差動増幅回路を提供する。

【解決手段】本発明の一実施形態としての高周波差増増幅回路は、第1MOSトランジスタ、第2MOSトランジスタ、第1正帰還素子および第2正帰還素子を備える。前記第1MOSトランジスタおよび第2MOSトランジスタは、ソースがそれぞれ第1電源に接続され、ドレインがそれぞれ負荷を介して第2電源に接続され、互いに反転した位相関係にある第1および第2入力信号をゲートで受ける。前記第1正帰還素子は、前記第1MOSトランジスタのゲートと、前記第2MOSトランジスタのドレインとの間に直列接続された第1キャパシタおよび第1可変抵抗を含む。前記第2正帰還素子は、前記第2MOSトランジスタのゲートと、前記第1MOSトランジスタのドレインとの間に直列接続された第2キャパシタおよび第2可変抵抗を含む。

(もっと読む)

増幅回路

【課題】適切な利得制御を行うことが可能な増幅回路を提供すること。

【解決手段】入力信号Itiaを増幅する増幅器10と、増幅器10の出力信号Vtiaを平均化して制御信号Vagcを生成し、時定数τs1と、τs1より大きいτl1とで時定数を切り換え可能な制御回路20と、Vagcに基づいて時定数制御信号Vsw0を生成する時定数制御回路30と、Vsw0を遅延させる遅延回路35と、制御回路20に接続されたノードN1を有し、遅延回路35に遅延されたVsw1に基づく信号の入力に応じて、Vtiaの電位のコピー電位をノードN1に出力し、時定数をτl1からτs1に切り換え、ノードN1をフローティングとし、時定数をτs1からτl1に切り換えるスイッチ回路200と、コピー電位出力までの時間を速めるアンプ300又は分流回路400と、Vagcに基づいてItiaをバイパスするバイパス回路40と、を具備する増幅回路。

(もっと読む)

増幅回路

【課題】複数の増幅部の動作時の出力電圧の波形を後段回路の処理可能な電圧範囲内に収めることができる増幅回路を提供する。

【解決手段】信号入力端子66に入力されたデジタル信号のレベルが所定の値以下である場合には、増幅率変更部64は、スイッチ35をオンにして増幅部62を動作状態にするとともに、スイッチ41をオフにして増幅部63を停止状態にし、かつ、増幅部62に流し込み電流を流し込むよう流し込み電流源65を制御する。それに対し、信号入力端子66に入力されたデジタル信号のレベルが所定の値を超える場合には、増幅率変更部24は、スイッチ35をオフにして増幅部62を停止状態にするとともに、スイッチ41をオンにして増幅部63を動作状態にし、かつ、増幅部62に流し込み電流を流し込まないよう流し込み電流源65を制御する。

(もっと読む)

ドライバアンプ回路および通信システム

【課題】バイアス調整回路やプリドライバ回路が不要で、しかも出力波形の波形歪みを低減することが可能なドライバアンプ回路および通信システムを提供する。

【解決手段】スイッチングトランジスタM11〜M14を駆動するゲート電圧を均一にするため、スイッチングトランジスタM11〜M14を電源およびGND側に配置し、さらに、スイッチングトランジスタM11〜M14の駆動振幅を安定させるために、各スイッチングトランジスタM11のドレインと出力ノードND11、ND12間にそれぞれ第1から第4の抵抗素子R11〜R14を接続している。

(もっと読む)

オーディオ増幅器

【課題】電源供給を停止したときに生じるボツ音を防止し、電源電圧が低い場合であっても高精度な定電圧源を不要にしたオーディオ増幅器を提供する。

【解決手段】電源電圧Vddが正常に供給されているとき、トランジスタM1はトランジスタM2の電流より小さな電流が流れるように設定されており、電源電圧Vddの供給が停止されたとき、キャパシタC1の電荷蓄積により基準電圧Vrefの低下が電源電圧Vddの低下より緩慢になり、トランジスタM4の電流がトランジスタM1の電流より小さくなると、電流比較器11から、出力回路40の動作を停止させる遮断信号が出力する。

(もっと読む)

電流切り替え回路

【課題】定電流回路の定電流源トランジスタを破損せずに、安定的にシャットダウンを行う。

【解決手段】電流切り替え回路は、エミッタフォロア回路(EF回路)と、定電流回路と、定電流回路をオン/オフするスイッチSW1とを備える。EF回路は、ベースが信号入力端子IN1に接続され、コレクタが電源VCC1に接続され、エミッタが信号出力端子OUT1に接続されたトランジスタQ1からなる。定電流回路は、ベースがスイッチSW1の出力に接続され、コレクタがトランジスタQ1のエミッタに接続されたトランジスタQ2と、第1の端子がトランジスタQ2のエミッタに接続され、第2の端子が電源VEE1に接続された抵抗RS1と、第1の端子がトランジスタQ2のコレクタに接続され、第2の端子が電源VEE1に接続されたリーク電流源JREAK1とからなる。

(もっと読む)

信号増幅装置及び方法

【課題】 LINC装置における信号の過入力を簡単な構成で高精度に検出する。

【解決手段】 信号増幅装置1は、入力信号Sinを分割して、所定の振幅を有し且つ位相の相異なる複数の分割信号Sa、Sbを生成する信号生成器10と、FET(Field Effect Transistor)を用いて複数の分割信号を夫々増幅する複数の増幅器20a、20bと、前記複数の増幅器の夫々で増幅された信号が通過する、長さが相異なり且つ端子間のアイソレーションを有しない伝送線路30a、30bと、複数の増幅器の夫々に入力されるゲート電流を比較することで、複数の増幅器のいずれかにおいて飽和状態を超過する分割信号の過入力が生じているか否かを検出する検出器40とを備える。

(もっと読む)

スイッチドキャパシター回路、検出装置及び電子機器

【課題】負荷電流による電圧ドロップを抑制するスイッチドキャパシター回路、検出装置及び電子機器等を提供すること。

【解決手段】スイッチドキャパシター回路は、出力用の演算増幅器OPBと、スイッチドキャパシター動作を行うための複数のスイッチ素子SB1〜SB8と、スイッチドキャパシター動作を行うための複数のキャパシターCB1,CB2と、スイッチドキャパシター回路の出力端子ノードNTと第1のスイッチ素子SB6との間に設けられる静電保護用の抵抗素子RB1と、を含む。

(もっと読む)

増幅回路

【課題】消費電流と回路規模を削減しつつ、同相信号除去比を高めることが可能な増幅回路を提供する。

【解決手段】P型トランジスタM1のソース端子がN型トランジスタM3のゲート端子に接続され、P型トランジスタM2のソース端子がN型トランジスタM4のゲート端子に接続され、P型トランジスタM1のドレイン端子がN型トランジスタM3のソース端子に接続され、P型トランジスタM2のドレイン端子がN型トランジスタM4のソース端子に接続され、入力差動対と出力差動対が逆極性を有するトランジスタで構成される。

(もっと読む)

出力回路

【課題】出力波形のオーバーシュート又はアンダーシュートを抑制することが可能な出力回路を提供すること。

【解決手段】本発明にかかる出力回路は、高電位側電源端子と外部出力端子との間に設けられ、外部入力信号に基づいてソース−ドレイン間に流れる電流が制御される出力トランジスタMP13と、低電位側電源端子と外部出力端子との間に設けられ、外部入力信号に基づいてソース−ドレイン間に流れる電流が制御される出力トランジスタMN14と、出力トランジスタMP13のゲートに第1の端子及び制御端子が接続され、出力トランジスタMP13のドレインに第2の端子が接続されたクランプ用トランジスタMP15と、を備える。

(もっと読む)

差動増幅器及びその制御方法

【課題】オーバーシュートやアンダーシュートを低減し、安定した出力電圧を生成することが可能な差動増幅器を提供すること。

【解決手段】本発明にかかる差動増幅器は、入力信号Vinとフィードバック信号とに応じた1対の信号を出力する差動増幅段回路110と、1対の信号に基づいて出力電圧VOUTを生成する出力段回路120と、を備える。出力段回路120は、外部出力端子と高電位側電源端子との間に設けられ、1対の信号の一方に基づいて抵抗値が制御されるトランジスタ11と、外部出力端子と中間電源端子との間に設けられ、1対の信号の他方に基づいて抵抗値が制御されるトランジスタ12と、外部出力端子と2種類の電源電圧を排他的に切り替えて出力する切り替えスイッチSW3、SW4との間に設けられ、1対の信号の他方に基づいて抵抗値が制御されるトランジスタ15と、2種類の電源電圧として、中間電圧と接地電圧とを備える。

(もっと読む)

オペアンプ

【課題】負荷電流の範囲を増加させることが可能なオペアンプを提供する。

【解決手段】入力端子−IN,+INに入力される入力信号の電位差を増幅して出力する第1の差動増幅回路11と、該回路11の差動対11bでの電位差を増幅して出力する第2の差動増幅回路12と、該回路12の差動対12bでの電位差に基づいて動作する差動対13bを含む第3の差動増幅回路13を有する。プルアップ側のトランジスタTP41は第2の差動増幅回路12の出力ノードN2の電位で動作し、プルダウン側のトランジスタTN41は第1の差動増幅回路11の出力ノードN1の電位で動作し、同プルダウン側のトランジスタTN42は第3の差動増幅回路13の出力ノードN3の電位で動作する。

(もっと読む)

半導体装置

【課題】最大出力電圧範囲を制限することができる増幅器を備えた半導体装置を提供する。

【解決手段】半導体装置1は、増幅部20と電源部10とを備える。増幅部20は、第1および第2の電源入力ノードN3,N4を有し、入力信号を、第1および第2の電源入力ノードN3,N4間に印加される駆動電圧に応じた振幅の信号に増幅して外部に出力する。電源部10は、入力信号を増幅部20によって線形増幅する通常モードまたは非通常モードを表わす制御信号CTLを受け、第1および第2の電源入力ノードN3,N4の少なくとも一方に制御信号CTLに応じた電源電位を供給する。この場合、電源部10は、通常モードを表わす制御信号を受けた場合には非通常モードを表わす制御信号を受けた場合よりも駆動電圧が小さくなるように、出力する電源電位の大きさを変更する。

(もっと読む)

演算増幅回路

【課題】数多くの出力電圧レベルを出力可能で、かつ、製造ばらつきに伴う出力オフセット電圧を低減し得る演算増幅回路を提供する。さらに、出力オフセット電圧の低減精度が、入力電圧に依存しないようにする。

【解決手段】第1および第2の回路状態を切り替えるスイッチ群を設ける。n+1種類の出力電圧レベルを出力できるよう、n個の入力用差動対を設ける。第1の回路状態において、各入力用差動対に一対の入力電圧群を供給して、カレントミラー回路を介して出力オフセット電圧を容量に保持する。第2の回路状態において、容量に保持された電圧を用いて出力オフセット電圧をキャンセルする。

(もっと読む)

電荷検出回路

【課題】差動アンプの入力側のゲイン調整を容易に行うことができる電荷検出回路を提供する。

【解決手段】電荷発生型センサ及び容量変化型センサの何れかで構成される物理量検出センサ1A,1Bの一端が差動アンプ3の負極入力端子に接続され、他端が前記差動アンプ3の正極入力端子に接続され、前記差動アンプ3の出力端子と前記負極入力端子との間にフィードバック抵抗Rf及びフィードバック容量Cfが並列に接続され、且つ前記差動アンプの正極入力端子と基準電圧との間にキャンセル抵抗Rc及びキャンセル容量Ccが並列に接続された差動型の電荷検出回路であって、前記差動アンプの負極入力端子及び正極入力端子の少なくとも一方に逆バイアス電源7,9によって逆バイアス電位が与えられた可変容量ダイオードD1,D2を接続してゲイン調整を可能とした。

(もっと読む)

出力回路及びデータドライバ及び表示装置

【課題】出力信号遅延を抑制し、消費電流の増大を抑制する出力回路の提供。

【解決手段】入力端子101と出力端子102の電圧を差動入力する差動入力段110からなる差動増幅回路と、第1及び第2の電源端子VDD、VSSに接続された第1及び第2のカレントミラー130、140と、前記第1及び第2のカレントミラーの入力間、出力間に接続される第1、第2の連絡回路150L、150Rと、第1導電型の第1のトランジスタ121と第2導電型の第2のトランジスタ122とからなる出力増幅回路と、前記第1、第2の電源端子VDD、VSSの電源電圧の間の電圧が供給される第3の電源端子VMLの電圧に応じたバイアス信号を受ける第1導電型の第3のトランジスタ161からなる制御回路160と、を備えている。

(もっと読む)

スイッチトキャパシタ型回路及びそれを用いたAD変換回路

【課題】消費電力を増大させることなく、高精度な基準電圧の下で動作するスイッチトキャパシタ型回路を提供する。

【解決手段】(1)第1のスイッチトキャパシタ(スイッチ11〜13及び帰還容量Cf)とサンプリング容量Csと増幅回路100とを含むスイッチトキャパシタ型増幅回路110aと、(2)スイッチトキャパシタ型増幅回路110aに基準電圧Vrefを供給する基準電圧回路110bとを備え、基準電圧回路110bは、基準電圧Vrefを出力するバッファ回路1と、バッファ回路1の出力端子111とスイッチトキャパシタ型増幅回路110aに基準電圧Vrefを供給するための基準電圧入力端子112との間に接続された第2のスイッチトキャパシタ(スイッチ10及び容量Cc)とを有する。

(もっと読む)

包絡線増幅器

【課題】回路構成を簡素化し、消費電流を削減する。

【解決手段】入力される包絡線信号の振幅に応じて第1の電流(Isense)を出力する第1の出力部(PMOS216、NMOS220が相当)と、第1の電流の電流値に比例し、第1の電流の電流値よりも絶対値が大きな電流値である第2の電流(Imain)を出力する第2の出力部(PMOS218、NMOS222が相当)と、を有する増幅器(206が相当)と、第1の電流の電流値を判断する比較部(208aが相当)と、比較部の判断結果に応じて断続される電流をインダクタ(228が相当)を介し第2の電流と加算して出力端から出力する出力部(210が相当)と、を備え、第1の電流を出力部に供給することなく終端するように構成する。

(もっと読む)

電力変換器のための制御装置

【課題】電力変換器のための制御装置を提供する。

【解決手段】電力変換器のための制御装置は、第1の増幅ステージと、第1の増幅ステージに連結される第2の増幅ステージとを備える。第1の増幅ステージは、電力変換器の出力信号に従ってエネルギー貯蔵素子の第1の端子における第1の増幅された信号を生成する。第2の増幅ステージは、エネルギー貯蔵素子の第2の端子における第2の増幅された信号を生成し、出力信号における変化に応答して、第2の増幅された信号を変化させる。第2の増幅ステージは、更に、第1の増幅された信号に基づいて、第2の増幅された信号の変化を減少させる。

(もっと読む)

差動増幅回路

【課題】電源電圧変動除去比を向上させつつ、回路内の消費電流の低減及び回路自体の小型化を図ることができる差動増幅回路を提供する。

【解決手段】電源電圧源に接続された電源ラインと、2つの差動入力素子からなる入力回路と、2つの差動入力素子にそれぞれが接続された2つのトランジスタからなる能動負荷とからなり、2つの差動入力素子のそれぞれに入力される入力信号に応じて差分信号を生成する入力部と、差分信号を増幅して出力電圧生成信号を生成する増幅部と、増幅部から供給される出力電圧生成信号と、電源電圧源から供給される電源電圧と、に基づいて出力電圧を生成する出力部と、2つのトランジスタのそれぞれの制御端と電源ラインとの間に接続され、電源電圧のノイズ成分のみを透過させるノイズ透過部と、を有することを特徴とする差動増幅回路。

(もっと読む)

141 - 160 / 1,173

[ Back to top ]