Fターム[5J500AK02]の内容

Fターム[5J500AK02]に分類される特許

81 - 100 / 1,173

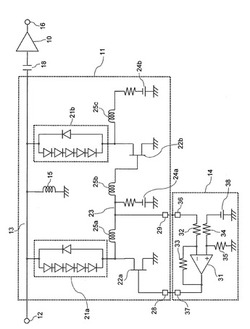

過入力保護回路及び過入力保護方法

【課題】高周波信号を受信するためのモノリシックマイクロ波集積回路で、過入力により保護回路が損傷しても、高周波特性を悪化させずに、回路を保護できるようにする。

【解決手段】過入力保護回路11は、複数段のアンチパラレルダイオード21a及び21bと、各段のFET22a及び22bとを有する。アンチパラレルダイオード21a及び21bは、過入力保護素子として動作する。FET22a及び22bは、各段のアンチパラレルダイオード21a及び21bを、高周波伝送ライン13と接地間に接続又は切り離すスイッチング素子として動作する。アンチパラレルダイオード21aが損傷すると、FET22aが高インピーダンス、FET22bが低インピーダンスの状態となり、初段のアンチパラレルダイオード21aに代わり、次段のアンチパラレルダイオード21bが過入力保護素子として機能する。

(もっと読む)

差動増幅回路及び集積回路装置

【課題】差動対を構成する2つのPMOSトランジスターにおけるNBTIの発生を可能な限り防ぐことにより出力オフセット電圧の発生を抑制可能な差動増幅回路及び集積回路装置を提供すること。

【解決手段】差動増幅回路1は、第1の信号が入力されるPMOSトランジスター10(第1のPMOSトランジスターの一例)と、第2の信号が入力されるPMOSトランジスター20(第2のPMOSトランジスターの一例)と、制御信号XSTBに基づいて、PMOSトランジスター10のゲートとバックゲートを同電位にするか否かを選択するPMOSトランジスター14(第1のスイッチ部の一例)と、制御信号XSTBに基づいて、PMOSトランジスター20のゲートとバックゲートを同電位にするか否かを選択するPMOSトランジスター24(第2のスイッチ部の一例)と、を含む。

(もっと読む)

信号送信回路

【課題】消費電流の増大を防止しながら、高調波の発生を抑制する。

【解決手段】

信号送信回路は、単一周波数の信号を出力する発振器と、発振器から出力された信号又は外部から伝送された信号を増幅する増幅部と、増幅部から出力された信号の出力電流を制御する可変電流器を有する出力バッファ部とからなる増幅回路と、増幅回路から出力された信号から、この信号の高調波成分を抽出し、抽出された高調波成分のパワーに基づき、可変電流器の電流を制御する電流制御電圧を出力する飽和レベル制御回路と、発振器及び飽和レベル制御回路の電源を制御する電源制御回路とを備える。

(もっと読む)

受信信号処理装置

【課題】回路規模が小さく消費電力が少ない受信信号処理装置を提供する。

【解決手段】受信信号処理装置は、高周波の受信信号に局部発振信号を合成して周波数変換するミキサ部と、多段に構成された複数の利得可変増幅器を含む増幅部と、増幅部により増幅されたアナログ信号をデジタル信号に変換する変換部と、各利得可変増幅器の後段に設けられたスイッチと、利得可変増幅器の出力が後段の利得可変増幅器を迂回して変換部に入力される経路の開閉を設定する迂回スイッチ部と、各利得可変増幅器の出力が後段の利得可変増幅器を介さずに変換部に入力するために、スイッチ及び迂回スイッチ部を制御するスイッチ制御部と、受信信号が補正対象の利得可変増幅器に入力されず、補正対象の利得可変増幅器の出力が後段の利得可変増幅器を介さずに変換部に入力される場合に、補正対象の利得可変増幅器に設定される利得に応じてDCオフセットの補正値を設定するDCオフセット制御部とを含む。

(もっと読む)

光センサおよび電子機器

【課題】出力信号の電圧低下を招くことなく、十分なゲインを確保できる光センサを提供する。

【解決手段】アノードが接地されたフォトダイオードPD1と、フォトダイオードPD1のカソードに一端が接続されたダイオード群DG1と、ダイオード群DG1の他端に一端が接続された電流源I1と、電流源I1の他端に一定電圧を印加する電源部と、フォトダイオードPD1のカソードにベースが接続され、電流源I1の一端にコレクタが接続されたエミッタ接地型のNPNトランジスタQOUT1とを備える。上記ダイオード群DG1は、フォトダイオードPD1側に順方向が向くように直列に接続されたn個(nは2以上の整数)のダイオードD1,D2,…,Dnであり、ダイオード群DG1と電流源I1との接続点から、フォトダイオードPD1に流れる光電流が電圧に変換されて光電変換信号として出力される。

(もっと読む)

信号変換装置及び信号変換方法

【課題】ADCのSNRを向上し、かつ、マイクロフォン用IC全体の歪み特性の劣化を最低限に抑えること。

【解決手段】本発明にかかる信号変換装置は、入力アナログ信号を増幅して出力するプリアンプ回路と、入力クロックのサイクルに応じて、プリアンプ回路からの出力に基づくアナログ信号をデジタル信号へ変換するAD変換器と、入力クロックの周波数に応じて、デジタル信号へ変換される前のアナログ信号である変換前アナログ信号の調整を制御する調整制御回路と、を備える。

(もっと読む)

フィルタ回路

【課題】 歪特性に優れるフィルタ回路を得る。

【解決手段】 直列に接続された複数のLPFを有するフィルタ回路において、複数のLPFはそれぞれ、スイッチトキャパシタ回路SC、および、SCの出力信号を増幅して出力する全差動型増幅器AMPを有する。1ビットDAC40の出力信号が入力されるLPF1が有するAMP10のコモンモードフィードバック回路は離散時間型であり、フィルタ回路としての出力信号を出力するLPF2が有するAMP20のコモンモードフィードバック回路は連続時間型である。

(もっと読む)

バッファ回路

【課題】入力信号の交流成分の歪み等の影響をなるべく受けることなく、本来のデューティー比(目標デューティー比)で出力信号を出力することのできるバッファ回路を提供する。

【解決手段】バッファ回路10は、デューティー比検出部16と直流成分生成部17とから構成される負帰還回路部によって、入力信号増幅部15の入出力間で出力信号SOのデューティー比に応じた直流成分の信号を帰還させている。つまり、バッファ回路10は、出力信号SOのデューティー比に応じて、入力信号SI´の直流成分をさらに小さくしたり、大きくしたりする。これにより、バッファ回路10は、出力信号SOのデューティー比を目的デューティー比に変更した上で、その出力信号SOを出力することができる。

(もっと読む)

利得可変差動増幅回路

【課題】広いダイナミックレンジを確保しつつ利得を変化させることが可能な利得可変差動増幅回路を提供すること。

【解決手段】この利得可変差動増幅回路12は、差動対トランジスタQ1,Q2,Q3,Q4とそれらのトランジスタのそれぞれのコレクタに接続された負荷抵抗14,15,18,19とそれらのトランジスタのエミッタに共通に接続された電流源16,20とをそれぞれ含む差動増幅回路17,21を有し、次段差動増幅回路21の出力を、帰還トランジスタQ5,Q6を介して初段差動増幅回路17に帰還させる利得可変差動増幅回路において、該初段差動対トランジスタQ1,Q2を流れるべき電流を分岐させる電流分岐回路部12Cと、差動対トランジスタQ1,Q2に電流を供給する電流供給回路部12Bとを備える。

(もっと読む)

カレントミラー回路およびそれを用いた半導体装置

【課題】プロセス変動があった場合でも広い出力電圧範囲が得られるカレントミラー回路を提供する。

【解決手段】この低電圧カスコードカレントミラー回路は、NチャネルMOSトランジスタQ1〜Q5と抵抗素子1を備える。トランジスタQ3のオーバードライブ電圧Vov_Q3は、トランジスタQ4,Q5のオーバードライブ電圧Vov_Q4,Vov_Q5の和に等しい。定電流Icと抵抗素子1の抵抗値R1との積は、トランジスタQ5の飽和マージンVdsm_Q5となる。したがって、プロセス変動があった場合でも、トランジスタQ5の飽和マージンVdsm_Q5は変化しない。

(もっと読む)

プリアンプ回路、及びマイクロフォン

【課題】低ノイズ特性を持つプリアンプ回路を提供すること

【解決手段】プリアンプ回路は、ソースフォロアとして機能するPMOSトランジスタM1A及びM1Bを備える。さらにプリアンプ回路は、差動増幅器として対となって機能するPMOSトランジスタM2A及びM2Bを備える。M1AのゲートとM2Bのゲートとが、可変容量C2を介して接続される。M1BのゲートとM2Aのゲートとが、可変容量C1を介して接続される。M1Aのソースと、M2Aのドレインと、が接続される。M1Bのソースと、M2Bのドレインと、が接続される。M2Aのソースと、M2Bのソースと、が接続される。

(もっと読む)

差動増幅装置

【課題】 差動増幅装置が出力するオフセット電圧を充分に抑制する。

【解決手段】 差動増幅器10は、キャパシタCを介して+IN端子に入力される信号と、−IN端子に入力される信号の差分を増幅する。スイッチS1は、+IN端子が、キャパシタCを介した信号を入力するか否かを切り替える。抵抗RINは、+IN端子と−IN端子の間に接続される。オフセット電圧補正回路20は、+IN端子がキャパシタCを介した信号を入力しないようにスイッチS1が制御された補正期間において、差動増幅器10の出力信号に基づき差動増幅器10のオフセット電圧を補正する。

(もっと読む)

オフセット補正回路

【課題】オフセットを迅速に検出しつつ、低域信号のカットを防止する。

【解決手段】オフセット検出回路(22a,22b,24,26)は、利得可変アンプ18の出力を所定の時定数で平滑して、直流成分であるオフセットを検出する。検出されたオフセットは加算回路28において利得可変アンプの入力に加算して、利得可変アンプ18の出力におけるオフセットを補正する。オフセット検出回路における時定数は、可変抵抗22a,22bの抵抗値により変更される。そして、時定数は、利得可変アンプ18の利得が変更されたときに、小さな時定数、その後大きな時定数に変更される。

(もっと読む)

フィルタ回路

【課題】フィルタ回路の遮断周波数精度を悪化させること無く、回路規模を低減することができるフィルタ回路を提供する。

【解決手段】駆動電流生成回路303は、容量C1に第1の基準電流を一定期間充電することにより生成される充電電圧を用いて、容量C1と第1の基準電流の比に比例した第1の駆動電流を生成する。OTA301は、正入力端子と負入力端子間の電位差に応じて、第1の駆動電流から、容量C1と第1の基準電流の比に逆比例した第2の駆動電流を生成して電圧に変換し、この電圧に応じて第2の基準電流を分配する。OTA301は、第2の基準電流を分配した電流と同量の電流を折り返して供給するカレントミラー回路を有し、正入力端子と負入力端子間の電位差に応じた電流をカレントミラー回路により折り返して負荷容量302に供給する。

(もっと読む)

ボルテージレギュレータ

【課題】出力電圧ごとにトリミングなどによる再調整を必要としないリップル除去率改善回路を有するボルテージレギュレータを提供する。

【解決手段】誤差増幅回路のカレント・ミラー部のMOSトランジスタ、もしくは入力段のMOSトランジスタのバックゲートに、リップル除去率改善回路の出力を接続する。こうすることで、電源端子もしくはグランド端子のリップルと出力端子のリップルが相殺されて、リップル除去率を改善することができる。

(もっと読む)

温度特性補正回路

【課題】コンパレータを使用せずに、調整電圧の傾きの切り替えを滑らかに行って温度特性の補正精度を向上させることのできる温度特性補正回路及びセンサ用増幅回路を提供すること。

【解決手段】所定の温度特性を備えた温度依存電圧Vtあるいはその温度依存電圧Vtを反転させた反転電圧XVtと、温度に関わらず一定電圧である基準電圧Vrefとに基づいて、第1及び第2補正電圧Vc1,Vc2をそれぞれ生成する補正用増幅器20,30を備えた。この補正用増幅器20,30の各出力端子をワイヤードオア接続した。

(もっと読む)

差動出力バッファ

【課題】送信状態とスタンバイ状態との間の遷移時間の増大を抑制しつつ、電流の変動を低減する。

【解決手段】メインドライバ1は、差動信号PREP、PRENのレベル変換を行い、バイパス回路2は、メインドライバ1の動作状態とスタンバイ状態との間の遷移時に高電源電位VDDから低電源電位VSSに流れる電流I5の変化量が一定の範囲内に収まるようにメインドライバ1に流れる電流I5をバイパスさせる。

(もっと読む)

演算増幅回路

【課題】セトリング速度を向上させる。

【解決手段】差動入力信号を増幅する差動対(M1、M2、M19)と、差動対の一方および他方の出力端にそれぞれ接続される一方および他方のカスコード増幅器対(M9、M10)と、カスコード増幅器対の一方および他方の出力端にそれぞれゲートを接続し、差動対の一方および他方の出力端にそれぞれドレインを接続するソース接地の第1のMOSトランジスタ対(M11a、M12a)と、を備える。カスコード増幅器対の一方および他方の出力端にそれぞれゲートを接続し、差動対の他方および一方の出力端にそれぞれドレインを接続する、第1のMOSトランジスタ対と同一の導電型であるソース接地の第2のMOSトランジスタ対(M3a、M4a)をさらに備える。

(もっと読む)

オーディオ信号増幅装置及びオーディオ信号増幅方法

【課題】歪みやノイズの発生箇所を問わず、Dクラスアンプの音質の劣化を改善することができるオーディオ信号増幅装置及びオーディオ信号増幅方法を提供する。

【解決手段】PWM変換回路11は、入力オーディオ信号をパルス幅変調し、PWM信号を生成する。出力段トランジスタ13は、生成されたPWM信号に基づいてスイッチングし、出力可変電源装置17から印加された電圧に基づいて、PWM信号を増幅する。出力フィルタ14は、増幅されたPWM信号を復調し、出力オーディオ信号を生成する。出力可変電源装置17は、出力オーディオ信号と入力オーディオ信号との差分に基づいて、出力段トランジスタ13に印加される電圧を制御する。

(もっと読む)

半導体集積回路およびその動作方法

【課題】DCオフセットキャンセル動作の動作期間を短縮する。

【解決手段】フィルタ処理と増幅機能を有するアクティブローフィルタ300の差動出力端子に2個の校正抵抗R22の一方の端子が接続され、2個の校正抵抗R22の他方の端子に電圧比較器CMPの2個の入力端子と切り換えスイッチSWIOの2個の端子が接続される。DCオフセット電圧低減のデジタル制御信号DACS、DAC2…DAC0を算出する算出期間で、デジタルアナログ変換器DAC0のアナログ電流による一方の校正抵抗R22の電圧降下に依存する校正電圧を電圧比較器CMPが検出する。DCオフセット電圧を低減する校正期間では、デジタル制御信号に応答したデジタルアナログ変換器の校正アナログ電流が切り換えスイッチSWIOを介してフィルタ300の入力側に流される。

(もっと読む)

81 - 100 / 1,173

[ Back to top ]