Fターム[5J500AK02]の内容

Fターム[5J500AK02]に分類される特許

21 - 40 / 1,173

演算増幅器

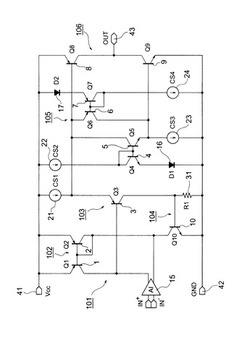

【課題】従来に比してより少ない追加素子数で、消費電流を増加させることなく、出力電流の最大値を、回路定数の調整によって、他の諸特性に影響を及ぼすことなく設定可能とする。

【解決手段】入力信号に対して差動増幅を行う差動増幅回路101と、差動増幅回路101の出力を電圧・電流変換して出力するプリドライバ回路103と、プリドライバ回路103の出力により駆動される出力段106とを有してなる演算増幅器であって、プリドライバ回路103を構成するプリドライバ用トランジスタ3のベース電流の増加を抑圧し、出力電流(出力ソース電流)の過電流保護を可能とした過電流保護回路104が設けられたものとなっている。

(もっと読む)

差動増幅器

【課題】出力電圧の出力精度に段差が発生していた。

【解決手段】電流源で駆動される第1、第2の差動対と、その電流源を駆動する第1の基準電流発生回路と、を備える第1の差動入力部と、電流源で駆動される第3、第4の差動対と、その電流源を駆動する第2の基準電流発生回路と、を備える第2の差動入力部と、前記第1、第2の差動入力部との出力に応じて、出力する出力部と、を有し、前記第1、第2の基準電流発生回路の第1、第2の電流経路上に接続される第1、第2のトランジスタを入力信号に応じて制御することで、前記第1、第2の差動入力部の出力を制御する差動増幅器。

(もっと読む)

定電圧バッファ回路

【課題】スタートアップ時などに、演算増幅回路の出力電圧が、駆動能力の高い側とは反対方向に大きくずれた場合においても、出力段の定電流源に制限されることなく、所定電圧へのセットリングを加速することが可能な定電圧バッファ回路を提供すること。

【解決手段】基準電圧(Vref)をバッファし、一定電圧の出力電圧(Vout)を供給する定電圧バッファ回路であって、出力電圧と基準電圧とを取得する差動増幅器(1)と、差動増幅器(1)の出力信号に応じて制御されるP型駆動の出力手段(2)と、出力電圧が基準電圧よりも大きいことを検出する検出手段(M11)と、検出手段(M11)において、出力電圧が基準電圧に対して大きいことが検出された場合には、出力ノードから電流を引き出すように電流を制御する電流制御手段(3)とを有する定電圧バッファ回路。

(もっと読む)

RF電力増幅器およびその動作方法

【課題】ランプアップまたはランプダウンにおいてスイッチングスペクトラムの劣化を軽減すること。

【解決手段】初段と最終段のバイアス回路81、83が、初段と最終段の増幅回路41、43のアイドリング電流を決定する。電力検出回路5、6は、最終段出力信号Poutの信号レベルに応答する電力検出信号VDETを生成する。誤差増幅器7に検出信号VDETと目標電力信号VRAMPが供給され、電力制御電圧VAPCが制御信号増強回路9の入力に供給され、出力から増強制御信号VENを生成する。制御信号増強回路9は、所定の非線型の入出力特性を有する。増強制御信号VENが初段と最終段のバイアス回路81、83とに供給され、初段と最終段の増幅回路41、43のアイドリング電流は増強制御信号VENによって制御され、RF電力増幅器の制御利得の低下が補償される。

(もっと読む)

駆動回路並びに関連するエラー検出回路及び方法

【課題】

発光装置のための低出力電圧駆動回路が、本発明の例示としての実施形態に従って提供される。

【解決手段】

また、オフセット電圧キャンセル及び/又はレベルシフタが、駆動電流の精度を高くするように駆動回路に組み込まれる。更に、エラー検出回路及び方法は、本発明の駆動回路の最小の出力電圧を検出して対応できるように、用いられる。

(もっと読む)

高周波電力増幅装置

【課題】出力電力を高効率で伝達可能な高周波電力増幅装置を提供する。

【解決手段】例えば、差動増幅器AD101,AD102と、その各出力インピーダンスを整合するトランスフォーマTR101を備え、AD101の差動出力ノード間にインダクタL101、スイッチS101、インダクタL102を直列に接続する。AD102が動作状態、AD101が非動作状態の場合には、S101がオンに制御される。この場合、AD101に含まれる差動対のトランジスタのオフ容量を踏まえて1次コイルLD111/LD112の両端から見たAD101側のインピーダンスが高インピーダンス状態(並列共振状態)となり、等価的に、AD102の動作に際してLD111/LD112は影響しなくなる。

(もっと読む)

可変調整精度を有する増幅器回路

【課題】 増幅器回路の可変精度の調整を実現するシステム及び方法を提供する。

【解決手段】 本開示の一態様によると、システムは、増幅器の利得を離散的な利得レベルに設定する複数の調整段を有する増幅器を有する。特定の実施形態では、調整段は直列に接続され、調整段の各々は、スイッチに並列に接続された抵抗器を有し、該スイッチはオフにされ、増幅器に利得を隣接する利得レベルに設定させる。特定の実施形態では、複数の利得レベルのうちの隣接する各々間の利得の差は、低い利得レベルより高い利得レベルにおいて大きい。

(もっと読む)

出力回路

【課題】2つの出力信号間のタイミングのずれを低減すること。

【解決手段】入力信号IN,XINはトランジスタM1,M2のゲートに供給される。トランジスタM1のドレインはトランジスタM3のドレインとトランジスタM4のゲートに接続され、トランジスタM2のドレインはトランジスタM3のゲートとトランジスタM4のドレインに接続される。また、トランジスタM1,M2のドレインは差動対のトランジスタM11,M12のゲートに接続される。トランジスタM3,M4のソースには、ゲートにバイアス電圧VBが供給されるトランジスタM5が接続される。トランジスタM11,M12のソースには、ゲートにバイアス電圧VBが供給されるトランジスタM13が接続される。

(もっと読む)

電力増幅器のバイアス回路および電力増幅器

【課題】コンプリメンタリSEPP回路において、出力抵抗を高くすることなくバイアス電流の安定したバイアス回路を提供する。

【解決手段】バイアス電流を検出する差動増幅器と、所定の電圧値と差動増幅器の出力電圧値との差分を増幅する演算増幅器と、演算増幅器の出力信号を絶縁伝達する絶縁伝達器と、絶縁伝達器の出力に応じたバイアス電圧を出力するバイアス電圧源とを備えたコンプリメンタリSEPP回路のバイアス回路。差動増幅器、演算増幅器、絶縁伝達器の動作により、バイアス電圧源は、バイアス電流が増加すると出力するバイアス電圧を低下させる。

(もっと読む)

車両用警報装置

【課題】BTL方式のパワーアンプにおいて、警報音発生の応答性を高めつつ、警報音停止時のポップ音の発生を抑えられる車両用警報装置の提供。

【解決手段】警報装置24は第1出力信号を出力する第1オペアンプ70と第2出力信号を出力する第2オペアンプ72とを有する。信号発生回路90は静電容量部94と静電容量部94の充電時と放電時とで抵抗値が変化する抵抗部92とを有しミュート作動信号及びミュート解除信号の入力により電圧信号をトランジスタTraに入力する。トランジスタTraはミュート解除時の電圧信号の入力で電圧信号の電圧変化時間に合わせて基準電圧を徐々に上昇させ、ミュート作動時の電圧信号の入力で電圧信号の電圧変化時間に合わせて基準電圧を徐々に下降させる。抵抗部92の抵抗値はミュート解除信号への切替り時の電圧信号の変化時間がミュート作動信号への切替り時の電圧信号の変化時間よりも長くなるように設定される。

(もっと読む)

全差動増幅器

【課題】初期動作を安定させるスタートアップ回路を備え、消費電力を低減すると共に、回路規模の増加を抑制した全差動増幅器を提供する。

【解決手段】図1に示す全差動増幅器は、入力信号を受け付ける差動対を含み、差動信号を出力する差動増幅器と、差動信号を増幅し、差動出力信号から出力コモンモード電圧を生成する出力コモンモード電圧生成回路と、出力コモンモード電圧と所定の基準電圧を比較することでコモンモードフィードバック信号を生成し、コモンモードフィードバック信号を差動増幅器にフィードバックすることで、出力コモンモード電圧と基準電圧を実質的に一致させるコモンモードフィードバック回路と、入力信号に基づいて、差動信号を略電源電圧にプルアップ又は略接地電圧にプルダウンするスタートアップ回路と、を備える。

(もっと読む)

信号処理装置

【課題】 抵抗及び小さな静電容量を用いた回路により、検出素子の出力信号を直流成分を除いて増幅する小型な信号処理装置を得る。

【解決手段】 入力信号が第1のインピーダンスを介して反転入力端子に入力される第1のオペアンプと、第1のオペアンプの反転入力端子と出力端子とに接続された第2のインピーダンスと、基準電圧が非反転入力端子に入力され、出力端子が第1のオペアンプの非反転入力端子に接続された第2のオペアンプと、第2のオペアンプの反転入力端子と出力端子とに接続された第1の静電容量と第1のスイッチと、第2のスイッチを介して第1のオペアンプの出力端子と前記第2のオペアンプの反転端子とに接続された第3の抵抗と、第3のスイッチを介して第1のオペアンプの出力端子と第2のオペアンプの反転端子とに接続された第4の抵抗とを備えた。

(もっと読む)

信号平均化回路

【課題】信号の平均化値のずれを抑制した信号平均化回路を提供する。

【解決手段】キャパシタCa1の正端子に接続され、キャパシタCa1への信号の入力を制御するスイッチング素子S9と、キャパシタCa2の正端子に接続され、キャパシタCa2への信号の入力を制御するスイッチング素子S10と、キャパシタCa1とキャパシタCa2の正端子同士とを接続する平均化スイッチ素子S13と、を備え、パワーオフ期間後にキャパシタCa1に信号を入力することにより充電を行うプリチャージ期間と、プリチャージ期間後に、キャパシタCa2に信号を入力することにより充電を行う第1サンプリング期間と、第1サンプリング期間後にキャパシタCa1に信号を入力することにより再充電を行う第2サンプリング期間と、前記第2サンプリング期間後にキャパシタCa1,Ca2の正端子同士を接続した状態とする平均化期間と、を設ける。

(もっと読む)

増幅器

【課題】増幅器の出力雑音電圧を抑制する。

【解決手段】正転入力電圧と反転入力電圧の差分を増幅する差動入力回路1と、差動入力回路1の出力信号を増幅して出力端子に出力する出力回路2と、差動入力回路1の電流源MP3と出力回路2の電流源MP4にバイアス電圧を出力するバイアス回路5を備えた増幅器である。差動入力回路1の正転入力電圧と反転入力電圧が共に接地電圧のときに出力端子に現れる出力雑音電圧を検出し、該雑音電圧のレベルが高いほど、バイアス回路5が、電流源MP3,MP4の電流を増大させるバイアス電圧を出力するようにした。

(もっと読む)

演算増幅器

【課題】入力オフセット電圧温度変動を悪化させることなく入力オフセット電圧のゼロ調整を可能とする。

【解決手段】差動対をなすように第1及び第2のPチャネルMOSトランジスタ1,2が差動接続されてなる差動増幅回路101を有すると共に、第1及び第2のPチャネルMOSトランジスタ1,2へテール電流を供給する第3の定電流源13に対して負の温度特性を有する電流を生成、出力する負温度特性電流生成回路103と、第1及び第2のPチャネルMOSトランジスタ1,2の各々へ入力オフセット電圧補正電流を供給する入力オフセット電圧補正電流生成回路102とを具備し、入力オフセット電圧補正電流生成回路102は、負温度特性電流生成回路103の出力電流を基に、入力オフセット電圧補正電流を出力調整可能に構成されたものとなっている。

(もっと読む)

増幅装置、増幅システムおよび電流電圧変換装置

【課題】適切にオフセット電圧をキャンセルすることが可能な増幅装置、増幅システムおよびこれを用いた電流電圧変換装置を提供する。

【解決手段】実施形態によれば、増幅装置は、メインアンプと、第1のサブアンプと、第2のサブアンプとを備える。前記メインアンプは、第1の入力電圧と第2の入力電圧との差を増幅した電圧を出力する。前記第1のサブアンプは、入力端子同士を短絡したときの出力電圧に基づいて自身のオフセットキャンセルを行い、前記第1の入力電圧および前記第2の入力電圧が入力されたときの出力電圧に基づいて前記メインアンプのオフセットキャンセルを行う。前記第2のサブアンプは、入力端子同士を短絡したときの出力電圧に基づいて自身のオフセットキャンセルを行い、前記第1の入力電圧および前記第2の入力電圧が入力されたときの出力電圧に基づいて前記メインアンプのオフセットキャンセルを行う。

(もっと読む)

演算増幅器

【課題】チップ面積の極端な増大を招くことなく、電源投入時の過渡期に出力端子を接地側に落とことを可能にすること。

【解決手段】正転入力電圧VIN_Pと反転入力電圧VIN_Nの差分を増幅する差動増幅回路10と、該差動増幅回路10の出力信号を入力し増幅してPMOSトランジスタM12とNMOSトランジスタM13の共通接続点から出力電圧VOUTを出力する出力回路20とを有する演算増幅器100である。トランジスタM13のゲートに一端が接続されたコンデンサCx1とトランジスタM12のゲートに一端が接続されたコンデンサCx2を備え、コンデンサCx1,Cx2の他端は抵抗Rx1を介して高電源端子1に接続されている。

(もっと読む)

増幅器、液晶表示用駆動回路、及び液晶表示装置

【課題】 入力段及び出力段の電源電位にかかわらず、増幅器の電力消費を抑えつつスルーレートを向上する。

【解決手段】 増幅器は、差動入力端子及び出力端子を有し、前記出力端子が前記差動入力端子の一方に帰還され、前記差動入力端子の他方に入力される入力信号を増幅し前記出力端子から出力するボルテージフォロア回路と、前記ボルテージフォロア回路に所定の電流を供給する第1電流源と、前記差動入力端子の他方と前記出力端子との間の電位差が所定値以上である場合に前記ボルテージフォロア回路に電流を供給する第2電流源と、を備える。

(もっと読む)

ボルテージフォロワ回路

【課題】動作電流を大きく増大させることなく、入力信号変化に対する出力追従性を向上させることのできるボルテージフォロワ回路を提供する。

【解決手段】実施形態のボルテージフォロワ回路は、P型差動対101と、N型差動対102と、折り返しカスコード型中間増幅段103と、出力段104とを備える演算増幅回路100を使用するボルテージフォロワ回路であって、出力変化加速部1が、P型差動対101に接続された定電流源I101からP型差動対101へ電流が流れないときに、出力段104へ加速電流I1を印加して出力段104の出力変化を加速し、出力変化加速部2が、N型差動対102に接続された定電流源I102からN型差動対102へ電流が流れないときに、出力段104へ加速電流I2を印加して出力段104の出力変化を加速する。

(もっと読む)

半導体装置

【課題】消費電流を削減する。

【解決手段】第1及び第2の入力端子に現れる電位差を第1及び第2の電源に基づいて増幅する差動アンプ(図2のMN1、MN2が相当)と、差動アンプを動作させるバイアス電流を制御するバイアストランジスタ(図2のMN3が相当)と、差動アンプの負荷となるカレントミラー回路(図2のMP1、MP2が相当)と、カレントミラー回路のダイオード接続側と其々の制御端が接続されると共に第1及び第2の電源間に直列に接続される、バイアストランジスタと逆導電型の第1及び第2のトランジスタ(図2のMP4、MP6が相当)を有し、第1及び第2のトランジスタの間の接続ノードをバイアストランジスタの制御端に接続するバイアス制御回路と、を備える。

(もっと読む)

21 - 40 / 1,173

[ Back to top ]