国際特許分類[H01L21/02]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体装置または固体装置またはそれらの部品の製造または処理に特に適用される方法または装置 (183,847) | 半導体装置またはその部品の製造または処理 (125,986)

国際特許分類[H01L21/02]の下位に属する分類

その後のフォトリソグラフィック工程のために半導体本体にマスクするもので,グループ21/18または21/34に分類されないもの (23,597)

少なくとも一つの電位障壁または表面障壁,例.PN接合,空乏層,キャリア集中層,を有する装置 (97,574)

電位障壁または表面障壁をもたない装置

国際特許分類[H01L21/02]に分類される特許

1,081 - 1,090 / 4,815

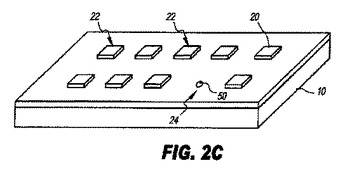

基板へのチップレットの付着

基板上にチップレット22を設ける方法であって、基板10を設けること、接着剤12の層を基板上に被覆すること、複数の第1のチップレット20を隔てられたチップレット位置22において接着剤層12上に配置することであって、第1のチップレットのうちの1つ又は複数は接着剤層に接着しなく、第1のチップレットが接着チップレット位置においては接着剤層に接着し、非接着チップレット位置24においては接着しないように、第1のチップレットを接着剤層に接着させること、非接着チップレット位置での接着剤層を局所的に処理することであって、非接着位置での接着剤層の状態を第2のチップレットを受けるように整えること、第2のチップレットを状態が整えられた非接着チップレット位置において接着剤層上に配置することであって、第2のチップレットを非接着位置において接着剤層に接着すること、及び接着剤を硬化させることを含む、方法。  (もっと読む)

(もっと読む)

半導体ウエハの製造方法及び半導体ウエハ

【課題】格子不整合系基板を使用しながら、高品質な単結晶窒化物半導体の結晶成長を実現する半導体ウエハの製造方法を提供する。

【解決手段】半導体基板101の表面にグラフェン層110を設ける工程と、グラフェン層110の炭素原子の配列を示すハニカム構造の中心に、単結晶半導体層の結晶を構成する一の元素を吸着させる工程と、この一の元素に前記結晶を構成する当該元素とは異なる他の元素を結合させ、前記結晶の第1層114を形成する工程と、前記第1層の表面にさらに所定の層数の前記結晶半導体層を結晶成長する工程を備える。

(もっと読む)

デバイスのシリアライゼーションを実行するためのシステムおよび方法

一意的なシリアル番号を生成し、チップ(または他の電子的オブジェクトまたはデバイス)に割り当て、追跡するためのセキュアな手段を提供するように資産管理システムを構成するためのシリアライゼーションサービスモジュールが提供される。このサービスを提供するために、コントローラは、製品モデルを定義し、各製品モデルに結び付けられる1つ以上のシリアライゼーションスキーマを定義するために用いられる。各シリアライゼーションスキーマは、特定の製品に対するシリアル番号の範囲を含む。シリアル番号スキーマは、セキュアな暗号化された接続を介して、製造者場所におけるアプライアンスに送信される。エージェントは、製品名によりシリアル番号値を要求し得る。シリアル番号は、アプライアンスにより生成され、測定され、エージェントに提供される。シリアル番号は、エージェントを用いてチップ製造過程において各ダイに連続注入される。  (もっと読む)

(もっと読む)

集積回路構造を形成する方法

【課題】 裏面相互接続構造と製造方法を提供する。

【解決手段】 集積回路構造を形成する方法であって、前記方法は、半導体ウエハの端から前記半導体ウエハの中に延びる第1ノッチを含む半導体ウエハを提供するステップ、及び前記半導体ウエハの上に、第2ノッチを含むキャリアウエハを設置するステップを含み、前記キャリアウエハを設置するステップは、前記第1ノッチの少なくとも一部を前記第2ノッチの少なくとも一部と重ねる方法である。

(もっと読む)

エピタキシャルシリコンウェーハの製造方法

【課題】エピタキシャルシリコンウェーハの外周部の表面平坦性が高まるエピタキシャルシリコンウェーハの製造方法を提供する。

【解決手段】シリコンウェーハの裏面デポジションのウェーハ周方向の平均値と、シリコンウェーハの外周部のSFQDのウェーハ周方向の平均値と、エピタキシャル膜のウェーハ周方向のロールオフの平均値とを合算した値が0となるように、エピタキシャル膜の成膜条件を決定し、エピタキシャル膜のロールオフを制御する。これにより、エピタキシャルシリコンウェーハの外周部の表面平坦性を高められる。その結果、平坦性適用領域が拡大し、デバイスの歩留まりが大きくなる。

(もっと読む)

薄膜装置、薄膜装置を備えた可撓性回路基板、及び薄膜装置の製造方法

【課題】剥離層、基板、又は設置面等の帯電による影響を受けない、回路動作が安定した薄膜装置を提供すること。

【解決手段】本発明の薄膜装置は、基板と、前記基板の上に形成された、導電性を有する電界遮蔽板と、前記電界遮蔽板の上に形成された、薄膜素子を含む能動層と、を備え、前記電界遮蔽板は、前記薄膜素子のいずれか電極の電位又は接地電位に接続されていることを特徴とする。

(もっと読む)

デバイス搭載ウェーハ、デバイスチップ、デバイスチップの製造方法

【課題】張り合わせウェーハであっても、その上に形成された各デバイスをオンウェーハ状態で確実に通電検査を行うことができるデバイス搭載ウェーハの提供、オンウェーハ状態での通電検査を確実に行うことができるデバイスチップ及びデバイスチップの製造方法の提供を課題とする。

【解決手段】支持基板用ウェーハ11に張り合わせ界面14を介して半導体層12を張り合わせた張り合わせウェーハを用い、スクライブライン10aで区分された複数のチップ領域10bにそれぞれ半導体デバイス13を構成してなるデバイス搭載ウェーハ10であって、前記スクライブライン10aに沿って前記張り合わせ界面14を越える深さの電気的隔離溝15を形成することで、前記各半導体デバイス13を電気的に分離独立させた状態に構成してある。

(もっと読む)

基板処理装置の制御方法及び記憶媒体

【課題】所定の処理室において、先に実行された処理作業単位によって作られた雰囲気を後に実行する処理作業単位において柔軟に利用することができる基板処理装置の制御方法を提供する。

【解決手段】PM12〜17を備える基板処理装置10の制御方法では、各ウエハに施される同一内容の処理からなる処理群に相当する作業単位であるプロセスジョブ(PJ)と、複数のPJからなる作業単位群であるコントロールジョブ(CJ)とが用いられ、先に実行されたPJが属するCJが、或るPMにおいて実行可能なPJを有さないときに、他のCJに属する当該PMにおいて実行可能なPJの実行が許可される。

(もっと読む)

シリコンウェーハの製造方法

【課題】半導体デバイス製造工程のみならず、その前段階のシリコンウェーハの製造工程でシリコンウェーハの割れの発生を抑制できるシリコンウェーハ製造方法の提供。

【解決手段】CZ法により育成されたシリコン単結晶のインゴット1からのシリコンウェーハの製造方法であって、インゴット1の外周を研削し、インゴット1を所定の中間直径に加工するとともに、このインゴット1の外周部に軸方向に沿って結晶方位の指標となるOF2aを形成する円筒研削工程と、インゴット1をスライスして素材ウェーハ2を切り出すスライス工程と、素材ウェーハ2の表面に、OF2aを基準にして、レーザーにより結晶方位の指標となる表記2bを施すレーザーマーキング工程と、素材ウェーハ2の外周を面取りし、OF2aを除去するとともに、所定の製品直径のシリコンウェーハ3に加工する面取り加工工程と、を含むことを特徴とするシリコンウェーハの製造方法である。

(もっと読む)

基板処理システム

本発明の実施形態は、再現可能かつ正確な基板処理を維持しながら、システム処理量を増大させ、システム稼働時間を改善し、かつデバイス歩留り性能を改善した処理システム内で基板を処理する装置および方法を提供する。システムは、システム制御装置によって制御される複数の平面の移動子を介して平面のモータを使用することによって横方向に位置決めできる複数の処理ネストを含むことができる。各処理ネストによって支持される基板は、回転アクチュエータによってその角度を決定できる。システムは、とりわけ、スクリーン印刷、インクジェット印刷、熱処理、デバイス試験、および材料除去プロセスに使用することができる。  (もっと読む)

(もっと読む)

1,081 - 1,090 / 4,815

[ Back to top ]