国際特許分類[H01L23/02]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体または他の固体装置の細部 (40,832) | 容器,封止 (4,129)

国際特許分類[H01L23/02]の下位に属する分類

形状に特徴のあるもの (756)

容器の材料またはその電気特性に特徴のあるもの (810)

部品間,例.容器の蓋と基台との間または容器のリードと壁との間,の封止の材料または配列に特徴のあるもの (308)

国際特許分類[H01L23/02]に分類される特許

2,211 - 2,220 / 2,255

微細構造および半導体デバイスのための新規なパッケージ方法

微細電気機械装置、半導体デバイス、発光素子、光変調装置、および、光検出装置を含む電子デバイス(例えば、電気信号を受信または送信する任意のデバイス)をパッケージする新規な方法が、ここに提供される。電子デバイスは、2つの基板の間に取り付けられ、それらの基板のうちの少なくとも1つの基板は、電子デバイスを保持するためのキャビティを有する。2つの基板は、シーリング媒体を用いて、接合されて密封される。基板に対するシーリング媒体の接着は、特に、2つの基板のうちの1つの基板がセラミックである場合に、メタライゼーション層を基板の表面に塗布することによって改善することができる。

(もっと読む)

(もっと読む)

空洞を形成する多層キャップを有する微細機械加工組立体

本発明は、多層高剛性キャップを有するシール空洞内に微細機械構造を製造するための方法を含む。キャップに用いられる高剛性材料は、パッケージングプロセスに内在する破壊的環境的影響力、及び環境的損傷から下にある微細構造体を保護する。  (もっと読む)

(もっと読む)

半導体装置、画像読取ユニット及び画像形成装置

【課題】光学機能素子の発熱による悪影響及び温度ムラによる悪影響を防止できる半導体装置を得る。

【解決手段】ライン型CCDチップ1が導電性放熱板に固定され、ライン型CCDチップ1と配電手段3とが電気的に接続された半導体装置に関する。ライン型CCDチップ1が固定される導電性放熱板2の固定面2aに対して反対側に位置する反対面2bの全面が外部に露出している。

(もっと読む)

半導体装置

【課題】電磁遮断性能を有し、機密性に優れた高信頼性の半導体装置を実現する。

【解決手段】フェライトを含むアルミナからなる絶縁性基板が積層された多層基板1の表面(第1主面)上に、半導体素子21と、チップ抵抗体22、チップコンデンサ23およびインダクタ24等からなる複数の受動素子が合金材25により電気的及び機械的に固着され、多層基板1の表面(第1主面)の両端部とフェライトを含むアルミナからなる絶縁性キャップ32は、接着剤31で固着され、これら搭載部品21、22、23、24、合金材5やボンデイングワイヤ27は、多層基板1と絶縁性キャップ32で気密封止されている。

(もっと読む)

高周波パッケージ

【課題】高周波特性を改善し、外部の高周波ノイズから保護し、外部への漏洩電力削減し、高出力素子の放熱を可能とした高周波パッケージを提供する。

【解決手段】誘電体材料からなる誘電体多層基板(251,296,301,306)と、蓋体(281)と、前記誘電体基板と前記蓋体により形成され高周波素子(381)を収納するためのキャビティ(271)と、前記誘電体基板内に設けられた接地導体(211,321)と、前記接地導体に導通し、前記誘電体基板を貫通するスル−ホール内に充填されたビア導体(221,231)とを具備した高周波パッケージとする。これにより、漏洩電力及び高周波ノイズの発生を防止でき、実装補助ガードエリヤが不要となり、パッケージの周辺にシールド板が不要となり、実装エリアが広がる。

(もっと読む)

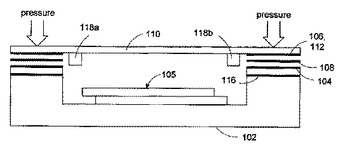

電気デバイスおよびその作製方法

【課題】製造コストを低減すると共に製造の歩留りを向上させることが可能な電気デバイスを提供する。

【解決手段】電気デバイス(100,502,602,702)は、複数の集積回路(106)を有しており、それらの集積回路の各々は、第2の基板(104)に結合された第1の基板(102)に製作される。ここで、第1の基板(102)は、ある変形条件を超える条件下では変形するが、その変形条件を下回る条件下では変形しない結合部(111)によって第2の基板(104)に結合されている。この変形条件は、第1の基板(102)と第2の基板(104)の対向する面からの所定の圧力とするか、または、温度と、第1の基板(102)と第2の基板(104)の対向する面からの圧力との所定の組み合わせとすることができる。

(もっと読む)

半導体装置

【課題】 半導体装置の小型化を図る。

【解決手段】 信号用表層配線4cとGND層4fとからなるマイクロストリップ線路4gを有するパッケージ基板4と、パッケージ基板4の主面4aにフリップチップ接続によって搭載された高周波の半導体チップ2と、信号用表層配線4cに芯線7aが電気的に接続された同軸ケーブル7と、半導体チップ2のフリップチップ接続部を保護するアンダーフィル樹脂6と、パッケージ基板4の裏面4b内に配置された複数のボール電極3と、パッケージ基板4に取り付けられたフレーム部材8に設けられた同軸コネクタ11とからなり、同軸ケーブル7からの高周波信号をパッケージ基板4の表層の全てマイクロストリップラインのみで伝達可能な構造を備えたものであり、複数のボール電極3がパッケージ基板4の裏面4bにアレイ状に配置されたことにより、パッケージの小型化を図れる。

(もっと読む)

高周波パッケージ

【課題】 パッケージ内に搭載される部品の実装性や他の基板への実装性が良く、しかも高密度実装が可能で放熱性に優れる高周波パッケージを得る。

【解決手段】 一方の面に入出力端子2を設け、他方の面に半導体チップ3を搭載したセラミック平板1と、前記他方の面に対向した一方の面に少なくとも1つのキャビティ部5を設けたセラミック多層キャップ4とで構成されるとともに、前記セラミック多層キャップ4のキャビティ部5の周縁部と、この周縁部に対向する前記セラミック平板1の他方の面とを電気的に接続する接続端子6を設けることで、キャビティ部5を設けた多層セラミックキャップ4をセラミック平板1に被装した。

(もっと読む)

高周波信号用の配線基板

【課題】準ミリ波帯及びミリ波帯の信号であっても隣接する信号線路系間のクロストークを低減する。

【解決手段】上部誘電体層1の上面に信号線路La1、La2、Lb1、Lb2が形成され、下部誘電体層2の上面に信号線路La3、Lb3が形成されている。信号線路La3は、上部誘電体層1を貫通する導電性ビアVHa1及びVHa2を介して信号線路La1とLa2とを電気的に接続し、信号線路Lb3は、上部誘電体層1を貫通する導電性ビアVHb1及びVHb2を介して信号線路Lb1とLb2とを電気的に接続する。上部及び下部誘電体層の上面、並びに下部誘電体層の下面には、グランド電極G1、G2、Gが形成され、各信号線路系はコプレーナ線路で形成される。入力端側及び出力端側の信号線路が、隣接する信号線路系で相互に異なる長さに形成されているので、電磁放射等による相互干渉を受けにくく、クロストークが低減される。

(もっと読む)

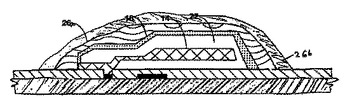

高周波機能モジュール及びその多層実装構造

【課題】従来の同一面上への部品搭載に代え、単機能モジュールを三次元的に実装して高周波機能モジュールの実装小型化、標準化、自動実装化、歩留まり向上、コスト低減をはかる。

【解決手段】単機能モジュールは、パッケージ1内に形成した有底のキャビティ2にMMIC(モノリシック・マイクロ波集積回路)3等の機能素子部品が搭載され、ボンディングワイヤ4により部品とパッケージ1間が電気的に接続される。パッケージ1上下面に設けた同軸構造のRFインターフェース5,6及び上下貫通したDCインターフェース7を通じ、パッケージ1内の接続回路8を介しMMIC3の信号が外部に出力する。キャップ9により気密封止構造を形成する。この単機能モジュールを縦方向に複数積層し、リフローによる半田溶融で各インターフェース間を接続し、多層の高周波機能モジュール構造とする。

(もっと読む)

2,211 - 2,220 / 2,255

[ Back to top ]