国際特許分類[H01L23/12]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体または他の固体装置の細部 (40,832) | マウント,例.分離できない絶縁基板 (9,861)

国際特許分類[H01L23/12]の下位に属する分類

形状に特徴のあるもの (436)

材料またはその電気特性に特徴のあるもの (925)

国際特許分類[H01L23/12]に分類される特許

111 - 120 / 8,500

半導体装置

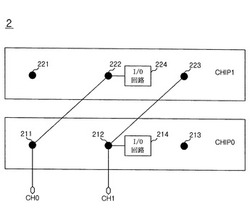

【課題】本発明は、積層されるチップに形成される貫通ビアの多様な連結構造を含む半導体装置を提供する。

【解決手段】半導体装置は、積層される第1および第2チップを備える。第1及び第2チップに垂直な同一線上に位置し、各々第1及び第2チップを貫通して形成される第1ないし第3貫通ビアと、第1チップの第2貫通ビアと連結される第1入出力回路及び第2チップの第2貫通ビアと連結される第2入出力回路とを備える。

(もっと読む)

半導体チップ搭載用基板及びその製造方法

【課題】微細配線を形成する場合であっても、ブリッジの発生を十分に低減でき、しかも優れたワイヤボンディング性を有する半導体チップ搭載用基板を製造可能な方法を提供すること。

【解決手段】本発明に係る半導体チップ搭載用基板製造方法は、基板の表面の導体回路の少なくとも一部を覆うように、電解ニッケルめっきによりニッケル層を形成する工程と、基板に対してデスミア処理を施す工程と、クエン酸を含む溶液に基板を浸漬する工程と、ニッケル層の少なくとも一部を覆うように、無電解めっきによりパラジウム層又は金層を形成する無電解めっき工程とをこの順序で備える。

(もっと読む)

プリント配線板

【課題】はんだクラック等の配線不良を防止しつつ、配線パターンの配線のレイアウトに自由度を持たせることができるプリント配線板の提供。

【解決手段】マトリクス状に配列された複数の電極パッド3と、電極パッド3から引き出された配線パターン4と、を有するプリント配線板1であって、複数の電極パッド3が配列された部品実装領域5の外側であって、該部品実装領域5の角部6の少なくとも一つに対応する位置において熱応力を緩和する孔部7を備え、孔部7の中心と部品実装領域5の中心とを結んだ直線Lの線状領域X内に位置する電極パッド3の配線パターン4は、該電極パッド3に対して該孔部7側に向かう方向以外の方向に引き出されているという構成を採用する。

(もっと読む)

リドライバIC、半導体装置、及びその製造方法

【課題】低損失で差動信号を伝送することができるリドライバIC、半導体装置、及びその製造方法を提供する。

【解決手段】本実施の形態に係る半導体装置は、差動信号が伝送される差動配線が形成された配線基板10と、配線基板10に搭載され、外部機器に対して差動信号を送受信するコネクタ11と、配線基板10に搭載され、コネクタ11から受信した差動信号を中継する受信系のリドライバIC21と、受信系のリドライバIC21と離間した位置において配線基板10に搭載され、コネクタ11に送信する差動信号を中継する送信系のリドライバIC20と、を備えるものである。

(もっと読む)

非接合的に格納される半導体デバイス

【課題】センサーパッケージにおいて、圧力測定精度において問題となる、機械的マウントおよび熱膨張等に起因して発生する、パッケージング応力を緩和するためのパッケージ構造を提供する。

【解決手段】非接合的に格納された半導体デバイスは、半導体ダイ(例えば、MEMS圧力センサーダイ)102を含む。前記半導体ダイ102は、周囲の格納体104の内部キャビティに接着されていない状態であるため、前記半導体ダイ102は前記格納体104に接着されず、これにより、前記格納体104と前記半導体ダイ102との間のパッケージング応力および歪みが緩和される。

(もっと読む)

半導体パッケージの製造方法及び半導体パッケージ

【課題】絶縁部材の充填不良を低減すること。

【解決手段】支持板44の突起部43が形成された面には、回路基板接続用パッド31と、実装用パッド16と、回路基板接続用パッド31及び実装用パッド16を接続する接続部(層間接続部32及び配線部33)がめっきにより形成される。支持板44は、半導体チップ14が実装された回路基板40に対向配置され、回路基板接続用パッド31がバンプ20を介して内部接続用パッド19に接続される。回路基板40と支持板44との間には、樹脂が充填され絶縁層15が形成される。支持板44は、エッチングにより除去される。

(もっと読む)

ビアを介して電力供給及び接地されるパッケージ

【課題】パッケージ化された集積回路を小型化する。

【解決手段】ワイヤボンド設計のパッケージ基板12は、その前面上にダイ-アタッチ-パッド20が配置され、該パッドは、電力供給用の表面28及び設置用の表面30を有する導電性表面を有している。パッケージ基板12は、ダイ-アタッチ-パッド20の外側に導電性ボンディングフィンガ24を有し、背面に電気接続40を有し、ボンディングフィンガ24及び導電性表面を、導電性トレース38により背面の電気接続40に接続している。ダイ-アタッチ-パッド20の上には集積回路を搭載した基板が配置され、該基板上の集積回路にボンディングフィンガ24及びワイヤを介して信号の伝達が行われ、導電性表面に設けられたビアを介して、集積回路に電力が印加される。

(もっと読む)

半導体素子搭載用配線板及びそれを用いた半導体装置

【課題】ヒートスプレッダや新たな部材の追加や、金型の変更、後加工の追加を行うことなく放熱特性が優れる半導体素子搭載用配線板とそれを用いた半導体装置を提供する。

【解決手段】配線板に搭載された少なくとも1つの半導体素子を有する半導体装置であって、配線板の内層と半導体素子との電気的な接続のために必要な部分8及び基板加工上必要な部分14を除き、半導体素子搭載面の配線パターン2を、半導体素子投影面から配線板端部まで設け、熱伝導路とした半導体素子搭載用配線板。前記半導体素子搭載用配線板に半導体素子を搭載した半導体装置。

(もっと読む)

半導体装置およびその製造方法、ならびに半導体装置用基板およびその製造方法

【課題】全体を薄くでき、安価で、かつ製造が容易な半導体装置およびその製造方法、ならびに半導体装置用基板およびその製造方法を提供する。

【解決手段】半導体装置10は、各々が内部端子面13bと外部端子面13aとを有する複数の端子部13と、ダイパッド12と、ダイパッド12上に搭載された半導体素子15とを備えている。ダイパッド12、端子部13、半導体素子15、および接続部17は、封止樹脂部11により封止されている。各端子部13の外部端子面13aおよびダイパッド12の外面12aは同一平面上に並び、各端子部13は、ニッケル層と、金層および銀層からなるボンディング用貴金属めっき層とを有している。該貴金属めっき層の合計厚みは、貴金属めっき層の表面がニッケル層の粗面を維持する程度の厚みとなっている。

(もっと読む)

半導体チップパッケージ

【課題】集積回路チップ内の電圧発生回路で発生されるパワーノイズを除去又は最小化できる半導体チップパッケージを提供する。

【解決手段】半導体チップパッケージは、外部電源電圧を受信して内部回路に使用される供給電圧を発生する電圧発生回路と、前記電圧発生回路の前記供給電圧の出力ノードに接続された接続ターミナルとを含む集積回路チップと、前記供給電圧に対するパワーノイズを減少させるために前記接続ターミナルに電気的に接続されたノイズ除去器と、半導体チップパッケージとして前記集積回路チップをパッケージングするために前記集積回路チップを搭載する搭載基板とを有する。

(もっと読む)

111 - 120 / 8,500

[ Back to top ]