国際特許分類[H01L27/10]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 1つの共通基板内または上に形成された複数の半導体構成部品または他の固体構成部品からなる装置 (52,733) | 整流,発振,増幅またはスイッチングに特に適用される半導体構成部品を含むものであり,少なくとも1つの電位障壁または表面障壁を有するもの;少なくとも1つの電位障壁または表面障壁を有する集積化された受動回路素子を含むもの (38,321) | 基板が半導体本体であるもの (36,153) | 複数の個々の構成部品を反復した形で含むもの (15,853)

国際特許分類[H01L27/10]の下位に属する分類

バイポーラ構成部品を含むもの (10)

電界効果構成部品を含むもの (11,969)

マスタースライス集積回路 (89)

国際特許分類[H01L27/10]に分類される特許

11 - 20 / 3,785

半導体装置及び半導体装置の作製方法

【課題】微細な構造であり、高い電気特性を有する半導体装置を歩留まりよく提供する。

【解決手段】酸化物半導体膜と、酸化物半導体膜上のゲート絶縁膜と、ゲート絶縁膜上のゲート電極と、ゲート電極上の導電膜と、酸化物半導体膜及びゲート絶縁膜の側面に接するソース電極及びドレイン電極と、を有し、ソース電極及びドレイン電極の上面の高さは、ゲート電極の上面の高さより低く、導電膜、ソース電極及びドレイン電極は、同一の金属元素を有する半導体装置である。また、ゲート電極の側面を覆う側壁絶縁膜を形成してもよい。

(もっと読む)

半導体装置

【課題】複数個のメモリチップが積層された構造を有する半導体装置の信頼性を向上させる。

【解決手段】半導体装置は、複数のビットラインと複数のワードラインとの交差点に複数個のメモリセルが配列される複数個のメモリチップが垂直方向に積層され、いずれか一つのメモリチップには複数個のメモリチップの各々に配列された複数のビットラインと連結されアクティブにされるメモリチップのビットラインをイネーブルさせるためのビットラインセンスアンプと、複数個のメモリチップの各々に配列された複数のワードラインと連結されアクティブされるメモリチップのワードラインをイネーブルさせるためのサブワードラインドライバを含み、ビットラインセンスアンプとサブワードラインドライバがいずれか一つのメモリチップに備わる。

(もっと読む)

FinFETを形成する方法およびFinFET構造

【課題】 ゲートの平面性が改善されたFinFETおよび形成方法を提供する。

【解決手段】 不要なフィンを除去する前にフィンのパターン上にゲートが配置される。リソグラフィ技法またはエッチング技法あるいはその両方の組み合わせを使用して、不要なフィンを除去することができる。残りのフィンの全部または一部を併合することができる。

(もっと読む)

半導体記憶装置

【課題】半導体記憶装置のスイッチング耐久性の向上を図る。

【解決手段】実施形態によれば、半導体記憶装置は、複数のセルアレイブロックと、制御回路とを備えている。制御回路は、選択ビット線を0ボルトにし、選択ワード線に0ボルトよりも高い第1の電位を与え、非選択ワード線に0ボルトよりも高く前記第1の電位よりも低い第2の電位を与え、選択セルアレイブロックに第1の方向で隣接し選択ビット線を選択セルアレイブロックと共有する隣接セルアレイブロックにおける、選択ビット線に隣接する非選択ビット線に0ボルト以上で前記第2の電位よりも低い第3の電位を与え、前記第3の電位が与えられた非選択ビット線以外の他の非選択ビット線に前記第2の電位を与えて、選択メモリセルの抵抗変化膜の抵抗状態を変化させる。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】製造の容易な不揮発性半導体記憶装置およびその製造方法を提供する。

【解決手段】不揮発性半導体記憶装置は、第1のメモリセルアレイ層と、第1のメモリセルアレイ層の上に形成された第1の絶縁層と、第2のメモリセルを具備する第2のNANDセルユニットを有する第2のメモリセルアレイ層と、第1の絶縁層を介して上下に位置する第1及び第2の浮遊ゲートの第1の方向の両側面にゲート間絶縁層を介して形成され、第1の方向と直交する第2の方向に延びる制御ゲートと、第1のNANDセルユニットの両端に位置し、第1の浮遊ゲートと同層に形成され、第1の半導体層と接続される下部コンタクトと、第2のNANDセルユニットの両端に位置し、第2の半導体層と下部コンタクトとを接続する上部コンタクトとを備える。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】制御性の高い不揮発性半導体記憶装置およびその製造方法を提供する。

【解決手段】不揮発性半導体記憶装置は、第1のメモリセルアレイ層と、第1のメモリセルアレイ層の上に形成された第1の絶縁層と、第1の絶縁層の上に形成された第2のメモリセルアレイ層と、第1の絶縁層を介して上下に位置する第1及び第2の浮遊ゲートの第1の方向の両側面にゲート間絶縁層を介して形成され、第1の方向と直交する第2の方向に延びる制御ゲートと、第1の絶縁層を介して上下に位置する第1及び第2の選択ゲートの第1の方向の両側面にゲート間絶縁層を介して形成され、第2の方向に延び、第1及び第2の半導体層並びに第1及び第2のゲート絶縁層と共に補助トランジスタを形成する補助ゲートとを備える。

(もっと読む)

半導体装置

【課題】メモリセルの動作を従来よりも高速化できる半導体装置を提供する。

【解決手段】フローティングゲートFGとコントロールゲートCG、第1導電型ソース13s及び第1導電型ドレイン13dを有する第1導電型MOSトランジスタ13と、前記フローティングゲートFGと前記コントロールゲートCG、第2導電型ソース14s及び第2導電型ドレイン14dを有する第2導電型MOSトランジスタ14と、前記第1導電型ドレイン13d及び前記第2導電型ドレイン14dに接続される第1のソース/ドレイン11bと、第2のソース/ドレイン11aと、ゲートを有する選択トランジスタ11と、前記第1導電型ソースに接続される第1電源線VpLと、前記第2導電型ソースに接続される第2電源線VnLと、前記選択トランジスタ11の第2のソース/ドレイン11aに接続されるビット線BLと、前記選択トランジスタ11のゲートに接続されるワード線WLと、を有する。

(もっと読む)

半導体メモリ装置およびその駆動方法

【課題】従来のDRAMでは微細化と共にデータの読み出しエラーが発生しやすくなる。

【解決手段】第1のビット線BL_1の微弱な電位の変動はNチャネル型トランジスタTNRとPチャネル型トランジスタTPRで構成される第1のインバータで反転され、第1のスイッチである第1の選択トランジスタST1を介して、第2のビット線BL_2に出力される。第2のビット線BL_2の電位は、第1のビット線BL_1の電位とは反転した電位であるため、第1のビット線BL_1と第2のビット線BL_2の電位差は拡大する。この拡大した電位差を公知のセンスアンプSA_1/2あるいは、第2のインバータ(Nチャネル型トランジスタTNLとPチャネル型トランジスタTPLで構成される)と第1のインバータで構成されるフリップフロップ回路等で増幅する。

(もっと読む)

半導体装置

【課題】作製工程が簡略化され、容量素子の面積が縮小化された昇圧回路を有する半導体

装置を提供することを課題とする。

【解決手段】直列に接続され、第1の入力端子部から出力端子部へ整流作用を示す複数の

整流素子と、第2の入力端子部に接続され、互いに反転する信号が入力される第1の配線

及び第2の配線と、それぞれ第1の電極、絶縁膜及び第2の電極を有し、昇圧された電位

を保持する複数の容量素子とから構成される昇圧回路を有し、複数の容量素子は、第1の

電極及び第2の電極が導電膜で設けられた容量素子と、少なくとも第2の電極が半導体膜

で設けられた容量素子とを有し、複数の容量素子において少なくとも1段目の容量素子を

第1の電極及び第2の電極が導電膜で設けられた容量素子とする。

(もっと読む)

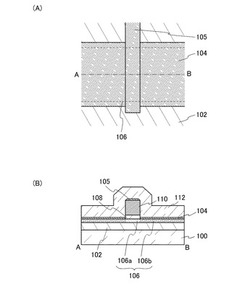

半導体装置および半導体装置の製造方法

【課題】ホールの微細化を図りつつ、ホールとスリットとを一括形成する。

【解決手段】4層分のワード線WL4〜WL1が順次積層されるとともに、ワード線WL4〜WL1にそれぞれ隣接するように4層分のワード線WL5〜WL8が順次積層され、ワード線WL5〜WL8が柱状体MP1にて貫かれるとともに、ワード線WL1〜WL4が柱状体MP2にて貫かれることで、NANDストリングNSが構成され、ワード線WL1〜WL8およびセレクトゲート電極SGD、SGSはロウ方向に沿って幅が周期的に変化されている。

(もっと読む)

11 - 20 / 3,785

[ Back to top ]