国際特許分類[H01P3/02]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 導波管;導波管型の共振器,線路または他の装置 (6,167) | 導波管;導波管型の伝送線路 (964) | 2本の長手方向導体をもつもの (693)

国際特許分類[H01P3/02]の下位に属する分類

レッヘル線対として構成された線路 (70)

同軸線路 (51)

マイクロストリップ;ストリップ線路 (425)

国際特許分類[H01P3/02]に分類される特許

21 - 30 / 147

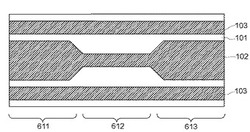

信号伝送路

【課題】 信号伝送路の変動を検出する回路などを追加することなく、コストアップを最小限に止めて、信号伝送路の特性インピーダンス補正を可能とする。

【解決手段】 誘電体の中に導体箔の信号線及びGND線が形成されて筐体に設置された場合に静電結合の影響を受ける信号伝送路において、導体箔を筐体に設置する場合は、信号伝送路の送信端と受信端の間で一定に構成した場合よりも、アイパターンにおける規定のマスクからのマージンが大きくなるように導体箔の形状を構成する。

(もっと読む)

伝送線路用熱可塑性液晶ポリマーフィルムおよび伝送線路

【課題】高周波帯域であっても伝送損失を低減することが可能である伝送線路を提供する。

【解決手段】伝送線路は、少なくとも1つの導体と、少なくとも1つの絶縁体とを含む伝送線路であって、前記絶縁体は、熱可塑性液晶ポリマーフィルムから形成され、この熱可塑性液晶ポリマーフィルムは、フィルムの機械軸方向(以下、MD方向と略す)とこれと直交する方向(以下、TD方向と略す)の1GHz以上の周波数における誘電正接の比(DTD/DMD)が1.02以下であり;前記熱可塑性液晶ポリマーフィルムのTD方向と、前記伝送線路の長手方向とが略同一方向に配設されている。

(もっと読む)

回路基板

【課題】信号伝送路の線幅を確保しつつ、メッシュ状導体部を用いることなく線路の特性インピーダンスの制御を十分に果たすことができる回路基板を提供すること。

【解決手段】絶縁体層2を挟んで、一方の面に信号伝送路3a,3bが形成され、他方の面にグランド層4が形成される。前記グランド層4には、さらに絶縁体層8を介してシールド層9が積層されると共に、前記グランド層4は、前記信号伝送路3a,3bに沿う位置において金属箔が敷設されない開口部4Bになされる。

この構成により、前記信号伝送路の特性インピーダンスは、信号伝送路と前記シールド層との間で形成される結合容量に依存されることになり、回路基板の薄型化に伴って発生する信号伝送路の特性インピーダンス制御の問題点を容易に解消することができる。

(もっと読む)

半導体集積回路部品

【課題】PCB基板に実装した時、および実装する前の高周波半導体集積回路部品単体において直流からミリ波帯までの広帯域にわたって、正確にデバイス特性の評価を可能とする。

【解決手段】プリント回路基板に表面実装される半導体集積回路部品であって、前記プリント回路基板に接して対向する面にコプレーナ線路構造を有し、前記コプレーナ線路の特性インピーダンスが50Ω+20%-0%以内に設定されている。

(もっと読む)

多帯域及び超広帯域用途のための、インピーダンスが最適化されたマイクロストリップ伝送線路のための方法、構造体、及び設計構造体

【課題】 多帯域及び超広帯域用途のための、インピーダンスが最適化されたマイクロストリップ伝送線路のための方法、構造体、及び設計構造体を提供すること。

【解決手段】 本方法は、信号線路に関連付けられた接地平面内に複数の開口部を形成すること、複数の開口部の中に複数のキャパシタンス・プレートを形成すること、及び、複数のキャパシタンス・プレートを、信号線路と複数のキャパシタンス・プレートとの間に延びる複数のポストによって信号線路に接続することを含む。

(もっと読む)

光制御高周波可変減衰器

【課題】マイクロ波信号の減衰量の変化幅を、より大きくすることができる光制御高周波可変減衰器を得る。

【解決手段】暗時に高抵抗値を示す半導体基板2と、半導体基板上に、コプレーナ線路構造を用いて形成された複数の共振器を有するフィルタ回路20と、フィルタ回路を覆うように、半導体基板上に配置される遮光性カバー30と、遮光性カバーの内部にフィルタ回路とともに配置され、制御信号に基づいて発光する光量を可変制御可能な光源10〜13とを備える。

(もっと読む)

コプレーナ線路

【課題】ミリ波帯域での基板への電磁波の漏れによる減衰が小さいコプレーナ線路を提供すること。

【解決手段】電気抵抗率が1kΩcm〜10kΩcmのシリコン基板12と、シリコン基板の第1主面12a側に形成される界面低抵抗層14と、界面低抵抗層上に形成される絶縁膜16と、絶縁膜の表面側に形成される信号線路18及び信号線路を平面的に挟む位置に設けられた1対の接地導体20a,20bとを備えていて、界面低抵抗層の電気抵抗率が、0.01Ωcmより大きい。

(もっと読む)

配線基板及び該配線基板を有する半導体装置、配線基板における端子配置方法

【課題】多数の差動ペア端子を有する半導体素子同士を配線基板に実装して差動伝送線路で接続する場合に、該伝送線路に伝播される信号の品質を良好に保つことができる配線基板及び半導体装置、配線基板の端子配置方法を提供する。

【解決手段】

配線基板は、二個の信号端子によって差動ペアを構成するペア信号端子対P30〜P33を有する半導体デバイス実装部を少なくとも二つと、これらのペア信号端子対同士を連結する差動伝送線路とを有し、一方に配置される第1のペア信号端子対と、他方に配置される第2のペア信号端子対とは、それぞれ信号配線の引き出し方向に沿う横並びに配置され、一方の外側列の端子4・6と、他方の内側列の端子9・11とが信号配線(S1)で接続され、一方の内側列の端子5・7と、他方の外側列の端子8・10とが信号配線(S1)で接続される。

(もっと読む)

スローウェーブ高性能結合コプレナ導波路

【課題】 結合コプレナ導波路構造を含む装置を提供する。

【解決手段】 1つ以上の信号線に近接し、前記信号線と互いに本質的に平行し、且つ第1方向に沿って実質的に向けられる1つ以上のアース線を備え、前記1つ以上の信号線のうちの少なくとも1つに含まれる周期的構造は交互セグメントを備え、前記交互セグメントのうちの少なくとも1つが第1方向を横断する第2方向に延長することを特徴とするコプレナ導波路構造。

(もっと読む)

配線基板及び半導体装置

【課題】少なくとも配線層数を最小限にでき、更には異なる信号間のクロストークを抑制する。

【解決手段】第一配線層7に半導体素子2が実装される。一列目の信号端子11と2列目の信号端子12、四列目の信号端子14と五列目の信号端子15とが差動ペアを構成している。三列目の信号端子13はグランド電極で、第四配線層10に形成されたグランド電極21と層間接続ビア20で接続されている。信号端子11に接続された信号配線16は第二配線層8に、信号端子12に接続された信号配線17は第三配線層9に形成され、差動伝送路を構成している。横方向に隣接した端子同士は独立した電位を有しており結合させる必要がないため、隣接した端子の直下のビアランド間に内側の端子に接続された別の信号配線を通すことができ、基板全体の配線層数を減らすことができる。

(もっと読む)

21 - 30 / 147

[ Back to top ]