不揮発性メモリ、圧電発振器

【課題】N回書き込み可能な不揮発性メモリ、及びこれを搭載した圧電発振器を提供する。

【解決手段】番地データ54が入力される第1ポート14を有し、番地をデコードして出力する第1トリミング回路12と、前記第1トリミング回路14に並列に複数接続され、書き込みデータ56が入力される第2ポート34と前記第2ポート34に接続される複数のメモリ回路42を有し、前記番地が入力され、前記番地が指定するメモリ回路42の出力電位をヒューズの切断制御により固定する第2トリミング回路30と、前記第1ポート14及び前記第2ポート34に接続され、前記番地データ54及び前記書き込みデータ56を有するシリアルデータ52を入力し、前記第1ポート14に前記番地データ54を出力し、前記第2ポート34に前記書き込みデータ56を出力するシフトレジスタ38と、を備えてなる。

【解決手段】番地データ54が入力される第1ポート14を有し、番地をデコードして出力する第1トリミング回路12と、前記第1トリミング回路14に並列に複数接続され、書き込みデータ56が入力される第2ポート34と前記第2ポート34に接続される複数のメモリ回路42を有し、前記番地が入力され、前記番地が指定するメモリ回路42の出力電位をヒューズの切断制御により固定する第2トリミング回路30と、前記第1ポート14及び前記第2ポート34に接続され、前記番地データ54及び前記書き込みデータ56を有するシリアルデータ52を入力し、前記第1ポート14に前記番地データ54を出力し、前記第2ポート34に前記書き込みデータ56を出力するシフトレジスタ38と、を備えてなる。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、圧電発振器の特性を補償するための不揮発性メモリについて、複数回書き込み可能とする技術に関する。

【背景技術】

【0002】

従来の小型圧電発振器は、特性を補償するための情報を格納する不揮発性メモリを有し、情報保持の方法としてはヒューズ形式を採用した不揮発性メモリを搭載している。例えば、このような小型圧電発振器の製造工程は、開口部に水晶振動片を搭載し気密封止を行った後、裏面開口部に不揮発性メモリを搭載した半導体素子をフェースダウンボンディングにより接合した後、接合部を樹脂で保護し、組み立てを完了する。ヒューズ切断によるデータ書き込み技術に関しては特許文献1及び特許文献2に開示されている。

【特許文献1】特開平4−68555号公報

【特許文献2】特開2007−189653号公報

【発明の開示】

【発明が解決しようとする課題】

【0003】

特許文献1及び特許文献2に開示されているように、従来のデータ書き込みは1度しかできない。そのため、圧電発振器等の温度補償及び機能調整時に1度決定したデータを変更することができず、量産時に調整後の修正が効かないため、歩留まりに影響が出る可能性があった。

そこで、本発明は上記問題点を解決するため、複数回書き込み可能な不揮発性メモリ、およびこれを搭載した圧電発振器を提供することを目的とする。

【課題を解決するための手段】

【0004】

本発明は、上述の課題を少なくとも一部を解決するためになされたものであり、以下の適用例として実現することが可能である。

【0005】

[適用例1]番地データが入力される第1ポートを有し、番地をデコードして出力する第1トリミング回路と、前記第1トリミング回路に並列に複数接続され、書き込みデータが入力される第2ポートと前記第2ポートに接続される複数のメモリ回路を有し、前記番地が入力され、前記番地が指定するメモリ回路の出力電位をヒューズの切断制御により固定する第2トリミング回路と、前記第1ポート及び前記第2ポートに接続され、前記番地データ及び前記書き込みデータを有するシリアルデータを入力し、前記第1ポートに前記番地データを出力し、前記第2ポートに前記書き込みデータを出力するシフトレジスタと、を有することを特徴とする不揮発性メモリ。

【0006】

上記構成により、第1トリミング回路が第2トリミング回路の書き込みデータの書き込む番地を指定し、複数の番地を有する複数の第2トリミング回路が指定された番地に書き込みデータを書き込むことになる。よって温度補償データ等の書き込みデータを、番地を変更することにより複数回書き込むことが可能な不揮発性メモリとなる。また素子数はわずかに増加する程度なので、IC面積の増加もある程度で抑えられる不揮発性メモリとなる。

【0007】

[適用例2]適用例1に係る不揮発性メモリを搭載したことを特徴とする圧電発振器。

上記構成により、温度補償データ等の補償データを複数回書き込み可能な圧電発振器となる。

【発明を実施するための最良の形態】

【0008】

以下、本発明を図に示した実施形態を用いて詳細に説明する。但し、この実施形態に記載される構成要素、種類、組み合わせ、形状、その相対配置などは特定的な記載がない限り、この発明の範囲をそれのみに限定する主旨ではなく単なる説明例に過ぎない。

【0009】

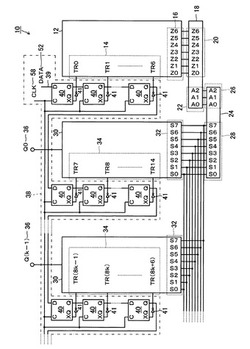

図1及び図2に第1実施形態に係る圧電発振器100、及び圧電発振器100を構成する不揮発性メモリ10を示す。図2に示すように、圧電発振器100は圧電振動子102、発振回路104、補償電圧発生回路106、自動周波数制御回路108、出力バッファ回路110、そして不揮発性メモリ10とから構成される。

不揮発性メモリ10は、シリアルで入力されるシリアルデータをパラレルデータに変換して出力するとともに、前記シリアルデータを内部に書き込むものである。

【0010】

図1に第1実施形態の不揮発性メモリ10の構成を示す。不揮発性メモリ10は、第1トリミング回路12、第2トリミング回路30、シフトレジスタ38、エンコーダ18、デコーダ24、により構成される。ここで後述のシリアルデータ52等の信号は、電位の高い方をH、低い方をLとする。

【0011】

本実施形態は、一例として温度補償データ等の書き込みデータ56が8回書き込み可能な構成について説明する。

第1トリミング回路12は後述の番地データ54を入力する第1ポート14(TR0〜TR6)とエンコーダへ出力する出力端子16(Z0〜Z6)を有する。

【0012】

エンコーダ18は第1トリミング回路12からの出力信号を3ビットのバイナリデータにエンコードするものであり、入力端子20(Z0〜Z6)及び出力端子22(A0〜A2)を有する。

【0013】

デコーダ24はエンコーダから出力される3ビットのバイナリデータをパラレルで入力してデコードし、デコードされた番地(計8個)を出力するものであり、入力端子26(A0〜A2)及び出力端子28(S0〜S7)を有する。

【0014】

第2トリミング回路30は、デコーダ24にn個並列に接続されている。(k−1)番目(k=1〜n)の第2トリミング回路30は番地を入力する端子である番地入力端子32(S0〜S7)と、書き込みデータを入力する第2ポート34(TR(8k−1)〜TR(8k+6))、書き込まれた書き込みデータ56を出力する外部出力端子36(Q(k−1))を有する。ここで個数nは温度補償データ等の書き込みデータのビット数と同数である。

【0015】

シフトレジスタ38は、Dフリップフロップ40を直列に接続することにより構成され、入力されるシリアルデータをパラレルで出力するものである。シフトレジスタ38は、前段のDフリップフロップ40の出力Qを次段のDフリップフロップ40の入力Dに接続させることによりDフリップフロップ40を直列接続させている。そして、Cから入力されるクロック58のネゲート(H→Lの立下り)をトリガとして初段のDフリップフロップ40からシリアルデータ52を1クロックずつ後段にシフトさせて最終段までストアさせ、各Dフリップフロップ40がストアするデータをパラレルで出力している。本実施形態においては、第1ポート14及び第2ポート34でトータルで(8n+7)個のDフリップフロップ40が用いられる。第0段(初段)から第6段(計7個)までの反転出力XQがインバータ41を介して第1トリミング回路12に接続され、(8k−1)段〜(8k+6)段(計8個)(k=1〜n)までの反転出力XQがそれぞれ、(k−1)番目の第2トリミング回路の第2ポート34(TR(8k−1)〜TR(8k+6))にインバータ41を介して接続される。

【0016】

図3に第1トリミング回路の回路図を示す。第1トリミング回路12は、それぞれ7つのヒューズ12a(f0〜f6)、Nchトランジスタ12b(Nch0〜Nch6)、抵抗R12c、及びインバータ12dから構成された回路である。ヒューズ12aは外部電源VDDに並列に接続されている。そして各ヒューズ12aの後段は、それぞれNchトランジスタ12bの各ドレイン端子と接続されている。また各ドレイン端子は、それぞれインバータ12dを介して出力端子16(Z0〜Z6)と接続され、さらに一端が接地された抵抗R12cともそれぞれ接続されている。Nchトランジスタ12bのゲート端子は対応する第1ポート14(TR0〜TR6)にそれぞれ接続され、ソース端子は接地されている。

【0017】

第1ポート14に一度も後述の番地データ54が来ていない場合、即ちNchトランジスタの各ゲート端子に番地データ54を構成する番地データ要素54a(図7参照)が信号Lとして一度も来ていない状態ではヒューズ12aは切断されていない。このとき外部電源VDDからの電流は、ヒューズ12aを通るが、抵抗R12cを経由して系外に流れるため、流れる電流は小さく、ヒューズ12cが切れることはない。そしてこのとき出力端子16(Z0〜Z6)の出力の電位はいずれもLである。しかし、例えばヒューズ12a(f0)後段に接続されたNchトランジスタ12b(Nch0)のゲート端子にHが入力されると、前記Nchトランジスタ12b(Nch0)導通するため、電流は抵抗Rを流れることはなく、ヒューズ12b(f0)を経由してNchトランジスタ12b(Nch0)側に一定時間(例えば100μs)大電流が流れることにより、前記ヒューズ12b(f0)は切断される。このとき、抵抗R12cの一端が接地されているため、ドレイン端子の電位はLとなり、出力端子16のうちZ0はHとなる。そして前記Z0が一度Hを出力すると、Lに戻ることはない。ここで、出力端子16はZ0〜Z6の7つあるため、全てLの状態からZ0からZ6まで順に電位をHとすることにより、トータルで8つの番地を包含したデータとなっている。

【0018】

図4にエンコーダの回路図と論理表を示す。エンコーダ18は図4(a)のように、インバータ18a、OR回路18b、AND回路18cを相互に組み合わせた回路である。エンコーダ18は出力端子16からの信号を入力する入力端子20(Z0〜Z6)と、エンコードして得られるバイナリデータを出力する出力端子22(A0〜A2)を有する。図4(b)の論理表に示すように、エンコーダ18は第1トリミング回路12からの出力端子16からの出力Z0〜Z6を3ビットのバイナリデータに変換することが可能である。バイナリデータにおいてA0が最下位ビット、A2が最上位ビットである。

【0019】

図5にデコーダの回路図と論理表を示す。デコーダ24は図5(a)のように、インバータ24a、NAND回路24bを相互に組み合わせた回路である。デコーダ24にはバイナリデータを入力する入力端子26(A0〜A2)と、デコードによって得られる番地を出力する出力端子28(S0〜S7)を有する。図5(b)の論理表に示すように、デコーダ24、は入力されたバイナリデータ(A0〜A2)をデコードして8つの番地に変換することが可能である。このように第1トリミング回路12から出力された番地を包含する信号を、エンコーダ18及びデコーダ24を介することにより、各番地に係る出力(S0〜S7)を個別に出力することができる。

【0020】

図6に第2トリミング回路の回路図を示す。(k−1)番目(k=1〜n−1)の第2トリミング回路30は8段のメモリ回路42(M(8k−1)〜M(8k+6))より構成されている。メモリ回路42はそれぞれ電源VDD及び外部出力Q(k−1)に並列に接続されている。メモリ回路42(M(8k−1)〜M(8k+6))は、ヒューズ44、Nchトランジスタ46、抵抗48、スイッチ付インバータ50とから構成される。ヒューズ44の一端は電源VDDに並列に接続され、他端はNchトランジスタ46のドレイン端子に接続されている。ドレイン端子は一端が接地された抵抗Rと接続されている。さらにドレイン端子はスイッチ付インバータ50側に接続されている。そしてNchトランジスタ46のゲート端子は、第2ポート34(Tr(8k−1)〜Tr(8k+6))に接続されている。

【0021】

スイッチ付インバータ50はPchトランジスタPch50a、Pch50b、及びNchトランジスタNch50c、Nch50dを組み合わせて構成され、電源VDDに並列に接続されている。ここでPch50a、Nch50dはインバータとして機能し、Pch50b、Nch50cはスイッチとして機能する。

【0022】

Pch50aのドレイン端子は電源VDDに接続され、ソース端子はPch50bのドレイン端子と接続されている。Pch50bのソース端子はNch50cのドレイン端子と接続され、この接続接点が出力端子50eとなる。そしてNch50cのソース端子はNch50dのドレイン端子と接続される。また、Pch50a及びNch50dのゲート端子は接続され、この接続接点が入力端子50fとなる。さらにPch50b及びNch50cのゲート端子はインバータ50gを介して接続され、この接続接点がスイッチ端子50hとなる。

【0023】

入力端子50fはそれぞれ、Nchトランジスタ46のドレイン端子に接続され、出力端子50eは外部出力端子36(Q(k−1))に接続され、スイッチ端子50hはそれぞれ、番地入力端子32(S0〜S7)に接続されている。Nchトランジスタ46のゲート端子は、それぞれ第2ポート34(Tr(8k−1)〜Tr(8k+6))に接続されている。そして、スイッチ端子50hにHが入力されると、Pch50b、及びNch50cが導通し、前記導通を条件に入力端子50fにH(L)が入力されると、出力端子50eと接続する外部出力端子36(Q(k−1))の出力はL(H)となる。なお、スイッチ端子50hの電位がLの場合、出力端子50eはPch50a、及びNch50dと電気的に接続しないため、外部出力端子36(Q(k−1))とスイッチ付インバータ50とは電気的に切断される。

【0024】

1回目の書き込みデータ56(図7参照)を書き込む際は、メモリ回路42(M(8k−1))に書き込みデータ56を書きこむ。このとき、スイッチ端子50hにHを入力するとともに、第2トリミング回路の第2ポート34(Tr(8k−1))から書き込みデータ56を構成する書き込みデータ要素56a(HまたはL)をNchトランジスタ46のゲート端子に入力する。前記書き込みデータ要素56aを書きこむ以前では電源VDDから流れる電流はヒューズ44及び抵抗48を経由している。このとき入力端子50fの電位はHである。そして書き込みデータ要素56aの電位がHの場合はNchトランジスタ46が導通し、ヒューズ44は、大電流が流れることにより切断される。すると抵抗48は一端が接地されているため、入力端子50fの電位はLとなるため、出力端子50eの電位はHとなり、外部出力端子36(Q(k−1))に電位がHの信号が出力される。また書き込みデータ要素56aの電位がLの場合はNchトランジスタ46は導通せず、ヒューズ44も切断されないので、入力端子50fの電位はHを維持し、出力端子50eの電位はLとなるため外部出力端子36(Q(k−1))に電位がLの信号が出力される。このように一の第2トリミング回路34から書き込みデータ要素56が出力されるため、n個の第2トリミング回路34の外部出力端子36(Q0〜Q(n−1))から結果的に書き込みデータ56がパラレルで出力されることになる。

【0025】

次に2回目の書き込みデータ56を書き込む際は、メモリ回路42(M(8k))に書きこみデータ56を書き込む。このとき、スイッチ端子50hに電位がHとなり、Nchトランジスタ46のゲート端子データが入力される。このとき、1回目の書き込みデータ56が書き込まれたメモリ回路42(M(8k−1))のスイッチ端子50fには電位がHの信号は入力されないので、メモリ回路42(M(8k−1))は外部出力端子36(Q(k−1))と電気的に切断される。そして1回目の書き込みと同様に、ヒューズ44、Nchトランジスタ46、スイッチ付インバータ50が動作し、外部出力端子36(Q(k−1))に2回目の書き込みデータ要素56aが出力され、全ての外部出力端子36を通じて書き込みデータ36がパラレルで出力される。本実施形態では8回まで同様の作業を行うことができ、8回目においてはメモリ回路42(M(8k+6))が動作する。

【0026】

図7にシリアルデータの構造を示す。図7(a)に示すように、シリアルデータ52はシフトレジスタ38のデータ入力端子39からクロック58のネゲートをトリガとし、パルス列として順次入力され、Dフリップフロップ40の反転出力XQが入力されたインバータ41の出力として保持されるデータである。本実施形態においては、8n+7番目のパルスから順次入力され、最後が0番目となる。そして図7(b)に示すように、0番目から6番目までのパルスが、第1トリミング回路にパラレルで入力される番地データ54が掛け合わされたパルスとなり、それ以外のパルスが、n個ある第2トリミング回路にパラレルで入力される書き込みデータ56が掛け合わされたパルスとなる。

【0027】

1回目の書き込みの際のシリアルデータ52のデータ構造は、第0番目から第6番目に番地データ54(番地データ要素54aはいずれもL)が、8k−1番目(k=1〜n)に書き込みデータ56を構成する書き込みデータ要素56a(D:電位HまたはL)が書き込まれる。よって、シリアルデータ52がシフトレジスタ38に全て入力された場合、第1トリミング回路において何ら変化は生じないが出力端子16(Z0〜Z6)の電位がいずれもLであるため、これがデコードされて番地(S0)となり、全ての第2トリミング回路30に入力される。一方、番地(S0)に係る(8k−1)番目のDフリップフロップ40の反転出力XQからは書き込みデータ要素56aの信号が出力され、これにインバータ41を介して接続される(k−1)番目の第2トリミング回路の第2ポート34(TR(8k−1))に書き込みデータ要素が入力される。そして所定時間(100μs)この状態を維持することにより第2トリミング回路30のヒューズ44は、前記書き込みデータ要素56aの電位がHの場合は切断され、これによりn個ある第2トリミング回路30に書き込みデータ56が不揮発的に書き込まれ、外部出力端子36(Q1〜Q(n−1))からパラレルで書き込みデータ56が出力されることとなる。

【0028】

2回目の書き込みの際のシリアルデータ52のデータ構造は、0番目に番地データ要素54a(電位H)が書き込まれ、8k番目に書き込みデータ要素が書き込まれる。よってシリアルデータ52が全て入力されると第0番目のDフリップフロップ40の反転出力XQに接続したインバータ41から番地データ要素54aの信号(L)が出力され、第1トリミング回路の第1ポート14(Tr0)に電位Hの信号が入力される。そして第1トリミング回路12のヒューズ12a(f0)が切断され、第1トリミング回路の出力端子12(Z0)の電位がHとなり、これがデコードされて得られた番地(S1)が全ての第2トリミング回路30に出力される。そして番地(S1)に係る8k番目のDフリップフロップの反転出力XQに接続したインバータ41から書き込みデータ要素56aが出力され、これに接続される(k−1)番目の第2トリミング回路の第2ポート34(TR(8k))に書き込みデータ要素56aが入力される。そして8回目の場合は、シリアルデータの6番目に番地データ要素54aが書き込まれ、8k+6番目に書き込みデータ要素56aが書き込まれる。

【0029】

本実施形態においては8回書き込み可能な構成を述べてきたが、これ以上の回数(N回)書きこみ可能な構成とするためには、第1トリミング回路12の第1ポート14を(N−1)個の端子で構成し、エンコーダ18は自然数Nをバイナリデータに変換できる構成とし、デコーダ24は前記のバイナリデータから解読されるN個の番地を個別に出力できるように構成し、n個(nは書き込みデータのビット数)の第2トリミング回路30の第2ポート34のN個の端子で構成し、シフトレジスタ38の個数を((N−1)+Nn)個とし、シリアルデータ52も((N−1)+Nn)個のパルス列として生成すればよい。

【0030】

圧電発振器100が書き込みデータを読み出す場合は、第1トリミング回路及び第2トリミング回路の電源VDDを投入するよう構成すればよい。このとき、第1トリミング回路12からの出力は最後に書き込まれた番地データに係るものであるので、外部出力端子36(Q1〜Q(n−1))から出力される書き込みデータ56は最後に書き込んだ書き込みデータ56のみが出力される。

【0031】

図8に第2実施形態に係る不揮発性メモリ60を示す。第2実施形態は、書き込み回数が2回の場合の不揮発性メモリである。第2実施形態の不揮発性メモリ60は基本的な構成は第1実施形態と同様であるが、第1実施形態におけるエンコーダ18及びデコーダ24を必要としない構成である。

【0032】

第1トリミング回路62は第1ポート64(Tr0)と出力端子66(Z0)を有する。n個(nは書き込みデータのビット数)の第2トリミング回路68は第1トリミング回路62に並列に接続されているが、(k−1)番目(k=1〜n)の第2トリミング回路68において、番地入力端子70(S0、S1)の個数は2つで、第2ポート72(TR(2k−1)、TR(2k))も2つである。そして第1トリミング回路62の出力端子66(Z0)は、(k−1)番目の第2トリミング回路68の番地入力端子70(S1)と、インバータ74を介して(k−1)番目の第2トリミング回路68の番地入力端子70(S1)と接続されている。このとき、出力Z0の出力がL(H)の場合はS0(S1)がHとなる。よって第1トリミング回路62の出力Z0は、この接続によりデコードされて第2トリミング回路68に入力されることとなる。

【0033】

なお、第2実施形態における第1トリミング回路62は、第1実施形態に係る第1トリミング回路12中の一の並列要素を取り出した態様のものである。また第2実施形態に係る第2トリミング回路68は、第1実施形態に係る第2トリミング回路30中の2つの連続するメモリ回路42を取り出した態様のものである。第1トリミング回路62及び第2トリミング回路68の動作は、書き込み回数が異なるだけで基本的動作は第1実施形態のものと同様であるので説明を省略する。また第2実施形態におけるシフトレジスタ76の基本的構成は第1実施形態のものと同様であり、シフトレジスタ76を構成するDフリップフロップ78の個数は(2n+1)個となる。よってシリアルデータ(不図示)のパルスも(2n+1)個あり、2n番目のパルスから順にシフトレジスタ80に入力され、シフトレジスタ76にシリアルデータ80が全て入力されたとき、最後に入力される第0番目のパルスには、番地データが入力され、それ以外の番号のパルスには書き込みデータが入力される。1回目の書き込みにおいて、シリアルデータは第0番目に番地データ(番地データ要素L)(不図示)を、(2k−1)番目(k=1〜n)に書き込みデータ(不図示)を構成すればよい。そして、2回目の場合は、第0番目に番地データ(番地データ要素H)(不図示)を、2k番目(k=1〜n)に書き込みデータ(不図示)を構成すればよい。

【0034】

以上述べてきたように、本実施形態に係る不揮発性メモリ10によれば、第1トリミング回路12が第2トリミング回路30の書き込みデータ56の書き込む番地を指定し、複数の番地を有する複数の第2トリミング回路30が指定された番地に書き込みデータ56を書き込むことになる。よって温度補償データ等の書き込みデータを、番地を変更することにより複数回(N回)書き込むことが可能な不揮発性メモリ10となる。また素子数はわずかに増加する程度なので、IC面積の増加もある程度で抑えられる不揮発性メモリ10となる。

また本実施形態にかかる圧電発振器100によれば、温度補償データ等の補償データを複数回書き込み可能な圧電発振器100となる。

【図面の簡単な説明】

【0035】

【図1】第1実施形態に係る不揮発性メモリの回路図である。

【図2】本実施形態に係る圧電発振器の模式図である。

【図3】第1実施形態に係る不揮発性メモリを構成する第1トリミング回路の回路図である。

【図4】第1実施形態に係る不揮発性メモリを構成するエンコーダの回路図と論理表を示す図である。

【図5】第1実施形態に係る不揮発性メモリを構成するデコーダの回路図と論理表を示す図である。

【図6】第1実施形態に係る不揮発性メモリを構成する第2トリミング回路の回路図である。

【図7】第1実施形態に係る不揮発性メモリを構成するシリアルデータの構造を示す図である。

【図8】第2実施形態に係る不揮発性メモリの回路図である。

【符号の説明】

【0036】

10………不揮発性メモリ、12………第1トリミング回路、14………第1ポート、16………出力端子、18………エンコーダ、20………入力端子、22………出力端子、24………デコーダ、26………入力端子、28………出力端子、30………第2トリミング回路、32………番地入力端子、34………第2ポート、36………外部出力、38………シフトレジスタ、39………データ入力端子、40………Dフリップフロップ、41………インバータ、42………メモリ回路、44………ヒューズ、46………Nchトランジスタ、48………抵抗、50………スイッチ付インバータ、52………シリアルデータ、54………番地データ、56………書き込みデータ、58………クロック、60………不揮発性メモリ、62………第1トリミング回路、64………第1ポート、66………出力端子、68………第2トリミング回路、70………番地入力端子、72………第2ポート、74………インバータ、76………シフトレジスタ、78………Dフリップフロップ、100………圧電発振器、102………圧電振動子、104………発振回路、106………補償電圧発生回路、108………自動周波数制御回路、110………出力バッファ回路。

【技術分野】

【0001】

本発明は、圧電発振器の特性を補償するための不揮発性メモリについて、複数回書き込み可能とする技術に関する。

【背景技術】

【0002】

従来の小型圧電発振器は、特性を補償するための情報を格納する不揮発性メモリを有し、情報保持の方法としてはヒューズ形式を採用した不揮発性メモリを搭載している。例えば、このような小型圧電発振器の製造工程は、開口部に水晶振動片を搭載し気密封止を行った後、裏面開口部に不揮発性メモリを搭載した半導体素子をフェースダウンボンディングにより接合した後、接合部を樹脂で保護し、組み立てを完了する。ヒューズ切断によるデータ書き込み技術に関しては特許文献1及び特許文献2に開示されている。

【特許文献1】特開平4−68555号公報

【特許文献2】特開2007−189653号公報

【発明の開示】

【発明が解決しようとする課題】

【0003】

特許文献1及び特許文献2に開示されているように、従来のデータ書き込みは1度しかできない。そのため、圧電発振器等の温度補償及び機能調整時に1度決定したデータを変更することができず、量産時に調整後の修正が効かないため、歩留まりに影響が出る可能性があった。

そこで、本発明は上記問題点を解決するため、複数回書き込み可能な不揮発性メモリ、およびこれを搭載した圧電発振器を提供することを目的とする。

【課題を解決するための手段】

【0004】

本発明は、上述の課題を少なくとも一部を解決するためになされたものであり、以下の適用例として実現することが可能である。

【0005】

[適用例1]番地データが入力される第1ポートを有し、番地をデコードして出力する第1トリミング回路と、前記第1トリミング回路に並列に複数接続され、書き込みデータが入力される第2ポートと前記第2ポートに接続される複数のメモリ回路を有し、前記番地が入力され、前記番地が指定するメモリ回路の出力電位をヒューズの切断制御により固定する第2トリミング回路と、前記第1ポート及び前記第2ポートに接続され、前記番地データ及び前記書き込みデータを有するシリアルデータを入力し、前記第1ポートに前記番地データを出力し、前記第2ポートに前記書き込みデータを出力するシフトレジスタと、を有することを特徴とする不揮発性メモリ。

【0006】

上記構成により、第1トリミング回路が第2トリミング回路の書き込みデータの書き込む番地を指定し、複数の番地を有する複数の第2トリミング回路が指定された番地に書き込みデータを書き込むことになる。よって温度補償データ等の書き込みデータを、番地を変更することにより複数回書き込むことが可能な不揮発性メモリとなる。また素子数はわずかに増加する程度なので、IC面積の増加もある程度で抑えられる不揮発性メモリとなる。

【0007】

[適用例2]適用例1に係る不揮発性メモリを搭載したことを特徴とする圧電発振器。

上記構成により、温度補償データ等の補償データを複数回書き込み可能な圧電発振器となる。

【発明を実施するための最良の形態】

【0008】

以下、本発明を図に示した実施形態を用いて詳細に説明する。但し、この実施形態に記載される構成要素、種類、組み合わせ、形状、その相対配置などは特定的な記載がない限り、この発明の範囲をそれのみに限定する主旨ではなく単なる説明例に過ぎない。

【0009】

図1及び図2に第1実施形態に係る圧電発振器100、及び圧電発振器100を構成する不揮発性メモリ10を示す。図2に示すように、圧電発振器100は圧電振動子102、発振回路104、補償電圧発生回路106、自動周波数制御回路108、出力バッファ回路110、そして不揮発性メモリ10とから構成される。

不揮発性メモリ10は、シリアルで入力されるシリアルデータをパラレルデータに変換して出力するとともに、前記シリアルデータを内部に書き込むものである。

【0010】

図1に第1実施形態の不揮発性メモリ10の構成を示す。不揮発性メモリ10は、第1トリミング回路12、第2トリミング回路30、シフトレジスタ38、エンコーダ18、デコーダ24、により構成される。ここで後述のシリアルデータ52等の信号は、電位の高い方をH、低い方をLとする。

【0011】

本実施形態は、一例として温度補償データ等の書き込みデータ56が8回書き込み可能な構成について説明する。

第1トリミング回路12は後述の番地データ54を入力する第1ポート14(TR0〜TR6)とエンコーダへ出力する出力端子16(Z0〜Z6)を有する。

【0012】

エンコーダ18は第1トリミング回路12からの出力信号を3ビットのバイナリデータにエンコードするものであり、入力端子20(Z0〜Z6)及び出力端子22(A0〜A2)を有する。

【0013】

デコーダ24はエンコーダから出力される3ビットのバイナリデータをパラレルで入力してデコードし、デコードされた番地(計8個)を出力するものであり、入力端子26(A0〜A2)及び出力端子28(S0〜S7)を有する。

【0014】

第2トリミング回路30は、デコーダ24にn個並列に接続されている。(k−1)番目(k=1〜n)の第2トリミング回路30は番地を入力する端子である番地入力端子32(S0〜S7)と、書き込みデータを入力する第2ポート34(TR(8k−1)〜TR(8k+6))、書き込まれた書き込みデータ56を出力する外部出力端子36(Q(k−1))を有する。ここで個数nは温度補償データ等の書き込みデータのビット数と同数である。

【0015】

シフトレジスタ38は、Dフリップフロップ40を直列に接続することにより構成され、入力されるシリアルデータをパラレルで出力するものである。シフトレジスタ38は、前段のDフリップフロップ40の出力Qを次段のDフリップフロップ40の入力Dに接続させることによりDフリップフロップ40を直列接続させている。そして、Cから入力されるクロック58のネゲート(H→Lの立下り)をトリガとして初段のDフリップフロップ40からシリアルデータ52を1クロックずつ後段にシフトさせて最終段までストアさせ、各Dフリップフロップ40がストアするデータをパラレルで出力している。本実施形態においては、第1ポート14及び第2ポート34でトータルで(8n+7)個のDフリップフロップ40が用いられる。第0段(初段)から第6段(計7個)までの反転出力XQがインバータ41を介して第1トリミング回路12に接続され、(8k−1)段〜(8k+6)段(計8個)(k=1〜n)までの反転出力XQがそれぞれ、(k−1)番目の第2トリミング回路の第2ポート34(TR(8k−1)〜TR(8k+6))にインバータ41を介して接続される。

【0016】

図3に第1トリミング回路の回路図を示す。第1トリミング回路12は、それぞれ7つのヒューズ12a(f0〜f6)、Nchトランジスタ12b(Nch0〜Nch6)、抵抗R12c、及びインバータ12dから構成された回路である。ヒューズ12aは外部電源VDDに並列に接続されている。そして各ヒューズ12aの後段は、それぞれNchトランジスタ12bの各ドレイン端子と接続されている。また各ドレイン端子は、それぞれインバータ12dを介して出力端子16(Z0〜Z6)と接続され、さらに一端が接地された抵抗R12cともそれぞれ接続されている。Nchトランジスタ12bのゲート端子は対応する第1ポート14(TR0〜TR6)にそれぞれ接続され、ソース端子は接地されている。

【0017】

第1ポート14に一度も後述の番地データ54が来ていない場合、即ちNchトランジスタの各ゲート端子に番地データ54を構成する番地データ要素54a(図7参照)が信号Lとして一度も来ていない状態ではヒューズ12aは切断されていない。このとき外部電源VDDからの電流は、ヒューズ12aを通るが、抵抗R12cを経由して系外に流れるため、流れる電流は小さく、ヒューズ12cが切れることはない。そしてこのとき出力端子16(Z0〜Z6)の出力の電位はいずれもLである。しかし、例えばヒューズ12a(f0)後段に接続されたNchトランジスタ12b(Nch0)のゲート端子にHが入力されると、前記Nchトランジスタ12b(Nch0)導通するため、電流は抵抗Rを流れることはなく、ヒューズ12b(f0)を経由してNchトランジスタ12b(Nch0)側に一定時間(例えば100μs)大電流が流れることにより、前記ヒューズ12b(f0)は切断される。このとき、抵抗R12cの一端が接地されているため、ドレイン端子の電位はLとなり、出力端子16のうちZ0はHとなる。そして前記Z0が一度Hを出力すると、Lに戻ることはない。ここで、出力端子16はZ0〜Z6の7つあるため、全てLの状態からZ0からZ6まで順に電位をHとすることにより、トータルで8つの番地を包含したデータとなっている。

【0018】

図4にエンコーダの回路図と論理表を示す。エンコーダ18は図4(a)のように、インバータ18a、OR回路18b、AND回路18cを相互に組み合わせた回路である。エンコーダ18は出力端子16からの信号を入力する入力端子20(Z0〜Z6)と、エンコードして得られるバイナリデータを出力する出力端子22(A0〜A2)を有する。図4(b)の論理表に示すように、エンコーダ18は第1トリミング回路12からの出力端子16からの出力Z0〜Z6を3ビットのバイナリデータに変換することが可能である。バイナリデータにおいてA0が最下位ビット、A2が最上位ビットである。

【0019】

図5にデコーダの回路図と論理表を示す。デコーダ24は図5(a)のように、インバータ24a、NAND回路24bを相互に組み合わせた回路である。デコーダ24にはバイナリデータを入力する入力端子26(A0〜A2)と、デコードによって得られる番地を出力する出力端子28(S0〜S7)を有する。図5(b)の論理表に示すように、デコーダ24、は入力されたバイナリデータ(A0〜A2)をデコードして8つの番地に変換することが可能である。このように第1トリミング回路12から出力された番地を包含する信号を、エンコーダ18及びデコーダ24を介することにより、各番地に係る出力(S0〜S7)を個別に出力することができる。

【0020】

図6に第2トリミング回路の回路図を示す。(k−1)番目(k=1〜n−1)の第2トリミング回路30は8段のメモリ回路42(M(8k−1)〜M(8k+6))より構成されている。メモリ回路42はそれぞれ電源VDD及び外部出力Q(k−1)に並列に接続されている。メモリ回路42(M(8k−1)〜M(8k+6))は、ヒューズ44、Nchトランジスタ46、抵抗48、スイッチ付インバータ50とから構成される。ヒューズ44の一端は電源VDDに並列に接続され、他端はNchトランジスタ46のドレイン端子に接続されている。ドレイン端子は一端が接地された抵抗Rと接続されている。さらにドレイン端子はスイッチ付インバータ50側に接続されている。そしてNchトランジスタ46のゲート端子は、第2ポート34(Tr(8k−1)〜Tr(8k+6))に接続されている。

【0021】

スイッチ付インバータ50はPchトランジスタPch50a、Pch50b、及びNchトランジスタNch50c、Nch50dを組み合わせて構成され、電源VDDに並列に接続されている。ここでPch50a、Nch50dはインバータとして機能し、Pch50b、Nch50cはスイッチとして機能する。

【0022】

Pch50aのドレイン端子は電源VDDに接続され、ソース端子はPch50bのドレイン端子と接続されている。Pch50bのソース端子はNch50cのドレイン端子と接続され、この接続接点が出力端子50eとなる。そしてNch50cのソース端子はNch50dのドレイン端子と接続される。また、Pch50a及びNch50dのゲート端子は接続され、この接続接点が入力端子50fとなる。さらにPch50b及びNch50cのゲート端子はインバータ50gを介して接続され、この接続接点がスイッチ端子50hとなる。

【0023】

入力端子50fはそれぞれ、Nchトランジスタ46のドレイン端子に接続され、出力端子50eは外部出力端子36(Q(k−1))に接続され、スイッチ端子50hはそれぞれ、番地入力端子32(S0〜S7)に接続されている。Nchトランジスタ46のゲート端子は、それぞれ第2ポート34(Tr(8k−1)〜Tr(8k+6))に接続されている。そして、スイッチ端子50hにHが入力されると、Pch50b、及びNch50cが導通し、前記導通を条件に入力端子50fにH(L)が入力されると、出力端子50eと接続する外部出力端子36(Q(k−1))の出力はL(H)となる。なお、スイッチ端子50hの電位がLの場合、出力端子50eはPch50a、及びNch50dと電気的に接続しないため、外部出力端子36(Q(k−1))とスイッチ付インバータ50とは電気的に切断される。

【0024】

1回目の書き込みデータ56(図7参照)を書き込む際は、メモリ回路42(M(8k−1))に書き込みデータ56を書きこむ。このとき、スイッチ端子50hにHを入力するとともに、第2トリミング回路の第2ポート34(Tr(8k−1))から書き込みデータ56を構成する書き込みデータ要素56a(HまたはL)をNchトランジスタ46のゲート端子に入力する。前記書き込みデータ要素56aを書きこむ以前では電源VDDから流れる電流はヒューズ44及び抵抗48を経由している。このとき入力端子50fの電位はHである。そして書き込みデータ要素56aの電位がHの場合はNchトランジスタ46が導通し、ヒューズ44は、大電流が流れることにより切断される。すると抵抗48は一端が接地されているため、入力端子50fの電位はLとなるため、出力端子50eの電位はHとなり、外部出力端子36(Q(k−1))に電位がHの信号が出力される。また書き込みデータ要素56aの電位がLの場合はNchトランジスタ46は導通せず、ヒューズ44も切断されないので、入力端子50fの電位はHを維持し、出力端子50eの電位はLとなるため外部出力端子36(Q(k−1))に電位がLの信号が出力される。このように一の第2トリミング回路34から書き込みデータ要素56が出力されるため、n個の第2トリミング回路34の外部出力端子36(Q0〜Q(n−1))から結果的に書き込みデータ56がパラレルで出力されることになる。

【0025】

次に2回目の書き込みデータ56を書き込む際は、メモリ回路42(M(8k))に書きこみデータ56を書き込む。このとき、スイッチ端子50hに電位がHとなり、Nchトランジスタ46のゲート端子データが入力される。このとき、1回目の書き込みデータ56が書き込まれたメモリ回路42(M(8k−1))のスイッチ端子50fには電位がHの信号は入力されないので、メモリ回路42(M(8k−1))は外部出力端子36(Q(k−1))と電気的に切断される。そして1回目の書き込みと同様に、ヒューズ44、Nchトランジスタ46、スイッチ付インバータ50が動作し、外部出力端子36(Q(k−1))に2回目の書き込みデータ要素56aが出力され、全ての外部出力端子36を通じて書き込みデータ36がパラレルで出力される。本実施形態では8回まで同様の作業を行うことができ、8回目においてはメモリ回路42(M(8k+6))が動作する。

【0026】

図7にシリアルデータの構造を示す。図7(a)に示すように、シリアルデータ52はシフトレジスタ38のデータ入力端子39からクロック58のネゲートをトリガとし、パルス列として順次入力され、Dフリップフロップ40の反転出力XQが入力されたインバータ41の出力として保持されるデータである。本実施形態においては、8n+7番目のパルスから順次入力され、最後が0番目となる。そして図7(b)に示すように、0番目から6番目までのパルスが、第1トリミング回路にパラレルで入力される番地データ54が掛け合わされたパルスとなり、それ以外のパルスが、n個ある第2トリミング回路にパラレルで入力される書き込みデータ56が掛け合わされたパルスとなる。

【0027】

1回目の書き込みの際のシリアルデータ52のデータ構造は、第0番目から第6番目に番地データ54(番地データ要素54aはいずれもL)が、8k−1番目(k=1〜n)に書き込みデータ56を構成する書き込みデータ要素56a(D:電位HまたはL)が書き込まれる。よって、シリアルデータ52がシフトレジスタ38に全て入力された場合、第1トリミング回路において何ら変化は生じないが出力端子16(Z0〜Z6)の電位がいずれもLであるため、これがデコードされて番地(S0)となり、全ての第2トリミング回路30に入力される。一方、番地(S0)に係る(8k−1)番目のDフリップフロップ40の反転出力XQからは書き込みデータ要素56aの信号が出力され、これにインバータ41を介して接続される(k−1)番目の第2トリミング回路の第2ポート34(TR(8k−1))に書き込みデータ要素が入力される。そして所定時間(100μs)この状態を維持することにより第2トリミング回路30のヒューズ44は、前記書き込みデータ要素56aの電位がHの場合は切断され、これによりn個ある第2トリミング回路30に書き込みデータ56が不揮発的に書き込まれ、外部出力端子36(Q1〜Q(n−1))からパラレルで書き込みデータ56が出力されることとなる。

【0028】

2回目の書き込みの際のシリアルデータ52のデータ構造は、0番目に番地データ要素54a(電位H)が書き込まれ、8k番目に書き込みデータ要素が書き込まれる。よってシリアルデータ52が全て入力されると第0番目のDフリップフロップ40の反転出力XQに接続したインバータ41から番地データ要素54aの信号(L)が出力され、第1トリミング回路の第1ポート14(Tr0)に電位Hの信号が入力される。そして第1トリミング回路12のヒューズ12a(f0)が切断され、第1トリミング回路の出力端子12(Z0)の電位がHとなり、これがデコードされて得られた番地(S1)が全ての第2トリミング回路30に出力される。そして番地(S1)に係る8k番目のDフリップフロップの反転出力XQに接続したインバータ41から書き込みデータ要素56aが出力され、これに接続される(k−1)番目の第2トリミング回路の第2ポート34(TR(8k))に書き込みデータ要素56aが入力される。そして8回目の場合は、シリアルデータの6番目に番地データ要素54aが書き込まれ、8k+6番目に書き込みデータ要素56aが書き込まれる。

【0029】

本実施形態においては8回書き込み可能な構成を述べてきたが、これ以上の回数(N回)書きこみ可能な構成とするためには、第1トリミング回路12の第1ポート14を(N−1)個の端子で構成し、エンコーダ18は自然数Nをバイナリデータに変換できる構成とし、デコーダ24は前記のバイナリデータから解読されるN個の番地を個別に出力できるように構成し、n個(nは書き込みデータのビット数)の第2トリミング回路30の第2ポート34のN個の端子で構成し、シフトレジスタ38の個数を((N−1)+Nn)個とし、シリアルデータ52も((N−1)+Nn)個のパルス列として生成すればよい。

【0030】

圧電発振器100が書き込みデータを読み出す場合は、第1トリミング回路及び第2トリミング回路の電源VDDを投入するよう構成すればよい。このとき、第1トリミング回路12からの出力は最後に書き込まれた番地データに係るものであるので、外部出力端子36(Q1〜Q(n−1))から出力される書き込みデータ56は最後に書き込んだ書き込みデータ56のみが出力される。

【0031】

図8に第2実施形態に係る不揮発性メモリ60を示す。第2実施形態は、書き込み回数が2回の場合の不揮発性メモリである。第2実施形態の不揮発性メモリ60は基本的な構成は第1実施形態と同様であるが、第1実施形態におけるエンコーダ18及びデコーダ24を必要としない構成である。

【0032】

第1トリミング回路62は第1ポート64(Tr0)と出力端子66(Z0)を有する。n個(nは書き込みデータのビット数)の第2トリミング回路68は第1トリミング回路62に並列に接続されているが、(k−1)番目(k=1〜n)の第2トリミング回路68において、番地入力端子70(S0、S1)の個数は2つで、第2ポート72(TR(2k−1)、TR(2k))も2つである。そして第1トリミング回路62の出力端子66(Z0)は、(k−1)番目の第2トリミング回路68の番地入力端子70(S1)と、インバータ74を介して(k−1)番目の第2トリミング回路68の番地入力端子70(S1)と接続されている。このとき、出力Z0の出力がL(H)の場合はS0(S1)がHとなる。よって第1トリミング回路62の出力Z0は、この接続によりデコードされて第2トリミング回路68に入力されることとなる。

【0033】

なお、第2実施形態における第1トリミング回路62は、第1実施形態に係る第1トリミング回路12中の一の並列要素を取り出した態様のものである。また第2実施形態に係る第2トリミング回路68は、第1実施形態に係る第2トリミング回路30中の2つの連続するメモリ回路42を取り出した態様のものである。第1トリミング回路62及び第2トリミング回路68の動作は、書き込み回数が異なるだけで基本的動作は第1実施形態のものと同様であるので説明を省略する。また第2実施形態におけるシフトレジスタ76の基本的構成は第1実施形態のものと同様であり、シフトレジスタ76を構成するDフリップフロップ78の個数は(2n+1)個となる。よってシリアルデータ(不図示)のパルスも(2n+1)個あり、2n番目のパルスから順にシフトレジスタ80に入力され、シフトレジスタ76にシリアルデータ80が全て入力されたとき、最後に入力される第0番目のパルスには、番地データが入力され、それ以外の番号のパルスには書き込みデータが入力される。1回目の書き込みにおいて、シリアルデータは第0番目に番地データ(番地データ要素L)(不図示)を、(2k−1)番目(k=1〜n)に書き込みデータ(不図示)を構成すればよい。そして、2回目の場合は、第0番目に番地データ(番地データ要素H)(不図示)を、2k番目(k=1〜n)に書き込みデータ(不図示)を構成すればよい。

【0034】

以上述べてきたように、本実施形態に係る不揮発性メモリ10によれば、第1トリミング回路12が第2トリミング回路30の書き込みデータ56の書き込む番地を指定し、複数の番地を有する複数の第2トリミング回路30が指定された番地に書き込みデータ56を書き込むことになる。よって温度補償データ等の書き込みデータを、番地を変更することにより複数回(N回)書き込むことが可能な不揮発性メモリ10となる。また素子数はわずかに増加する程度なので、IC面積の増加もある程度で抑えられる不揮発性メモリ10となる。

また本実施形態にかかる圧電発振器100によれば、温度補償データ等の補償データを複数回書き込み可能な圧電発振器100となる。

【図面の簡単な説明】

【0035】

【図1】第1実施形態に係る不揮発性メモリの回路図である。

【図2】本実施形態に係る圧電発振器の模式図である。

【図3】第1実施形態に係る不揮発性メモリを構成する第1トリミング回路の回路図である。

【図4】第1実施形態に係る不揮発性メモリを構成するエンコーダの回路図と論理表を示す図である。

【図5】第1実施形態に係る不揮発性メモリを構成するデコーダの回路図と論理表を示す図である。

【図6】第1実施形態に係る不揮発性メモリを構成する第2トリミング回路の回路図である。

【図7】第1実施形態に係る不揮発性メモリを構成するシリアルデータの構造を示す図である。

【図8】第2実施形態に係る不揮発性メモリの回路図である。

【符号の説明】

【0036】

10………不揮発性メモリ、12………第1トリミング回路、14………第1ポート、16………出力端子、18………エンコーダ、20………入力端子、22………出力端子、24………デコーダ、26………入力端子、28………出力端子、30………第2トリミング回路、32………番地入力端子、34………第2ポート、36………外部出力、38………シフトレジスタ、39………データ入力端子、40………Dフリップフロップ、41………インバータ、42………メモリ回路、44………ヒューズ、46………Nchトランジスタ、48………抵抗、50………スイッチ付インバータ、52………シリアルデータ、54………番地データ、56………書き込みデータ、58………クロック、60………不揮発性メモリ、62………第1トリミング回路、64………第1ポート、66………出力端子、68………第2トリミング回路、70………番地入力端子、72………第2ポート、74………インバータ、76………シフトレジスタ、78………Dフリップフロップ、100………圧電発振器、102………圧電振動子、104………発振回路、106………補償電圧発生回路、108………自動周波数制御回路、110………出力バッファ回路。

【特許請求の範囲】

【請求項1】

番地データが入力される第1ポートを有し、番地をデコードして出力する第1トリミング回路と、

前記第1トリミング回路に並列に複数接続され、書き込みデータが入力される第2ポートと前記第2ポートに接続される複数のメモリ回路を有し、前記番地が入力され、前記番地が指定するメモリ回路の出力電位をヒューズの切断制御により固定する第2トリミング回路と、

前記第1ポート及び前記第2ポートに接続され、前記番地データ及び前記書き込みデータを有するシリアルデータを入力し、前記第1ポートに前記番地データを出力し、前記第2ポートに前記書き込みデータを出力するシフトレジスタと、を備えることを特徴とする不揮発性メモリ。

【請求項2】

請求項1に係る不揮発性メモリを搭載したことを特徴とする圧電発振器。

【請求項1】

番地データが入力される第1ポートを有し、番地をデコードして出力する第1トリミング回路と、

前記第1トリミング回路に並列に複数接続され、書き込みデータが入力される第2ポートと前記第2ポートに接続される複数のメモリ回路を有し、前記番地が入力され、前記番地が指定するメモリ回路の出力電位をヒューズの切断制御により固定する第2トリミング回路と、

前記第1ポート及び前記第2ポートに接続され、前記番地データ及び前記書き込みデータを有するシリアルデータを入力し、前記第1ポートに前記番地データを出力し、前記第2ポートに前記書き込みデータを出力するシフトレジスタと、を備えることを特徴とする不揮発性メモリ。

【請求項2】

請求項1に係る不揮発性メモリを搭載したことを特徴とする圧電発振器。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【公開番号】特開2009−266267(P2009−266267A)

【公開日】平成21年11月12日(2009.11.12)

【国際特許分類】

【出願番号】特願2008−111419(P2008−111419)

【出願日】平成20年4月22日(2008.4.22)

【出願人】(000003104)エプソントヨコム株式会社 (1,528)

【Fターム(参考)】

【公開日】平成21年11月12日(2009.11.12)

【国際特許分類】

【出願日】平成20年4月22日(2008.4.22)

【出願人】(000003104)エプソントヨコム株式会社 (1,528)

【Fターム(参考)】

[ Back to top ]