半導体装置およびその製造方法

【課題】 優れたトランジスタ特性を有するDRAMが高い集積度で形成された半導体装置を提供する。

【解決手段】 半導体基板(1)に設けられたトレンチと、前記トレンチの内壁下側に設けられたキャパシタ絶縁膜と、前記トレンチの内壁上側に設けられたカラー絶縁膜(9)と前記トレンチ内に埋め込まれたストレージ電極(10)とを有するトレンチキャパシタ、半導体基板に設けられたMOSトランジスタ、および、前記MOSトランジスタのソース/ドレイン拡散領域(18)の一方と前記トレンチキャパシタの前記ストレージ電極とを接続するシリサイド膜(16)を有する半導体装置である。前記カラー絶縁膜は上部に導電膜(20)を有し、前記導電膜は、隔離絶縁膜(19)によって前記半導体基板、前記ストレージ電極、および前記カラー絶縁膜から隔離されていることを特徴とする。

【解決手段】 半導体基板(1)に設けられたトレンチと、前記トレンチの内壁下側に設けられたキャパシタ絶縁膜と、前記トレンチの内壁上側に設けられたカラー絶縁膜(9)と前記トレンチ内に埋め込まれたストレージ電極(10)とを有するトレンチキャパシタ、半導体基板に設けられたMOSトランジスタ、および、前記MOSトランジスタのソース/ドレイン拡散領域(18)の一方と前記トレンチキャパシタの前記ストレージ電極とを接続するシリサイド膜(16)を有する半導体装置である。前記カラー絶縁膜は上部に導電膜(20)を有し、前記導電膜は、隔離絶縁膜(19)によって前記半導体基板、前記ストレージ電極、および前記カラー絶縁膜から隔離されていることを特徴とする。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置およびその製造方法に係り、特に、ダイナミックランダムアクセス(DRAM)メモリのトレンチキャパシタおよびその製造方法に関する。

【背景技術】

【0002】

DRAMのメモリセルは、キャパシタとトランスファゲート用のMOSトランジスタから構成されている。DRAMの集積度を上げるためには、より小さな面積でより大きな容量のキャパシタを形成することが望ましい。その一つの手段として、シリコン基板に設けたトレンチを用いてキャパシタを形成するトレンチキャパシタが挙げられる。

【0003】

トレンチキャパシタを有するDRAMセルにおいて、トランジスタのソース/ドレイン拡散領域と蓄積キャパシタのストレージ電極とを、シリサイド等の導電膜により接続することが提案されている(例えば、特許文献1参照)。

【0004】

深いトレンチ(Deep Trench:DT)にキャパシタを形成したDRAMを形成する場合、一般に、DTを形成後にDT内の上部領域を除く領域には、膜厚の薄いキャパシタ絶縁膜が形成され、上部領域には比較的膜厚の厚いカラー絶縁膜が形成される。これらの絶縁膜を介して、ストレージ電極がDT内に埋め込み形成される。蓄積キャパシタのストレージ電極としては、不純物がドープされたポリシリコン膜が一般的に用いられ、こうしたストレージ電極とトランジスタのソース/ドレイン拡散領域とを接続するシリサイド膜等の導電膜は、カラー絶縁膜の上に形成されることとなる。

【0005】

シリサイド膜等の導電膜は、ストレージ電極とソース/ドレイン拡散領域とを確実に接続することが求められる。また、トランジスタの性能の劣化を避けるためには、このトランジスタが形成された半導体基板中にストレージ電極中の不純物が拡散することは、極力避けることが望まれる。

【特許文献1】特開昭62−213273号公報

【発明の開示】

【発明が解決しようとする課題】

【0006】

本発明は、優れたトランジスタ特性を有するDRAMが高い集積度で形成された半導体装置、およびその製造方法を提供することを目的とする。

【課題を解決するための手段】

【0007】

本発明の一態様にかかる半導体装置は、半導体基板に設けられたトレンチと、前記トレンチの内壁下側に設けられたキャパシタ絶縁膜と、前記トレンチの内壁上側に設けられたカラー絶縁膜と前記トレンチ内に埋め込まれたストレージ電極とを有するトレンチキャパシタ、

半導体基板に設けられたMOSトランジスタ、および

前記MOSトランジスタのソース/ドレイン拡散領域の一方と前記トレンチキャパシタの前記ストレージ電極とを接続するシリサイド膜を有する半導体装置であって、

前記カラー絶縁膜は上部に導電膜を有し、

前記導電膜は、隔離絶縁膜によって前記半導体基板、前記ストレージ電極、および前記カラー絶縁膜から隔離されていることを特徴。

【0008】

本発明の一態様にかかる半導体装置の製造方法は、半導体基板にトレンチを形成する工程と、

前記トレンチ側面の所定の高さまでキャパシタ絶縁膜を形成する工程と、

前記キャパシタ絶縁膜より上のトレンチ側面にカラー絶縁膜を形成する工程と、

前記トレンチ内および前記半導体基板の上に、不純物を含有したポリシリコン膜を形成する工程と、

前記ポリシリコン膜をエッチング除去して前記トレンチ内に残置し、ストレージ電極を形成する工程と、

前記カラー絶縁膜の上部を除去して、前記半導体基板および前記ストレージ電極を側面に露出することにより凹部を形成する工程と、

全面に隔離絶縁膜を介して導電膜を形成する工程と、

前記導電膜、前記隔離絶縁膜、および前記ストレージ電極をエッチングして、前記凹部内に前記隔離絶縁膜を介して前記導電膜を残置する工程と、

前記ストレージ電極上に素子分離層を形成する工程と、

前記半導体基板上にゲート電極配線および側壁酸化膜を含むゲート部を形成する工程と、

前記ゲート部を挟んで前記半導体基板上にソース/ドレイン拡散領域を形成する工程と、

前記ソース/ドレイン拡散領域の一方と前記ストレージ電極とを接続するシリサイド膜を形成する工程とを具備することを特徴とする。

【発明の効果】

【0009】

本発明の一態様によれば、優れたトランジスタ特性を有するDRAMが高い集積度で形成された半導体装置、およびその製造方法が提供される。

【発明を実施するための最良の形態】

【0010】

本発明者らは、トレンチキャパシタを有するDRAMセルにおいて、トランジスタのソース/ドレイン拡散領域と蓄積キャパシタのストレージ電極とを、シリサイド膜により接続した従来の半導体装置について鋭意検討した結果、次のような知見を得た。

【0011】

すなわち、こうした構造の半導体装置においては、トランジスタのソース/ドレイン拡散領域と蓄積キャパシタのストレージ電極とを接続するシリサイド膜は、カラー絶縁膜の上に形成されることから、このカラー絶縁膜の膜厚が半導体装置の特性に影響を及ぼす。具体的には、カラー絶縁膜の膜厚が厚い場合には、図1に示されるようにストレージ電極22とソース/ドレイン拡散領域18との距離が長くなって、シリサイド膜16で確実に接続することができない。

【0012】

なお、図1は従来の構造を示しており、半導体基板1に設けられたトレンチ内には、カラー絶縁膜9を介して、不純物がドープされたポリシリコン膜10およびポリシリコン膜11が埋め込まれ、これらポリシリコン膜がストレージ電極22を構成する。ストレージ電極22およびカラー絶縁膜9は部分的に除去されて素子分離層13が設けられ、この上にはゲート電極配線14が形成される。ゲート電極配線14の側面には酸化膜15が設けられ、上面にはシリサイド膜16が形成される。半導体基板1にはMOSトランジスタが形成され、このトランジスタのソース/ドレイン拡散領域18は、シリサイド膜16によって、ストレージ電極22に接続されなければならない。

【0013】

カラー絶縁膜9の膜厚を薄くすれば、シリサイド膜16が不連続になるといった問題を回避することができる。しかしながら、カラー絶縁膜9が存在しない場合には、図2に示すようにポリシリコン膜11から不純物が半導体基板1に拡散して、不純物拡散領域17が形成される。この不純物拡散領域17とトランジスタのソース拡散領域18とのSub Vthが低下して、電荷保持特性の低下につながる。

【0014】

トランジスタのソース/ドレイン拡散領域は、シリサイド膜によってストレージ電極に確実に接続されなければならず、しかも、ストレージ電極中の不純物が半導体基板へ拡散するのは極力回避すべきである。本発明の実施形態は、これを可能としたものである。

【0015】

図3乃至図11に、本発明の実施形態にかかる半導体装置の製造方法を表わす断面図を示す。

【0016】

まず、図3に示すように、半導体基板1上に2nm程度の酸化膜(図示せず)を形成し、220nm程度のシリコン窒化膜3、および1600nm程度の酸化膜4を順次堆積する。続いて、光学的パターニング法および反応性イオンエッチング法を用いて、酸化膜4、シリコン窒化膜3、および酸化膜をパターンニングする。さらに、酸化膜4をマスクとして用いて半導体基板を6μm程度の深さまでエッチングすることにより、トレンチパターンを形成する。

【0017】

ウェットエッチング法を用いて酸化膜4を除去した後、全面に5nm程度の膜厚のシリコン窒化膜(図示せず)を形成する。このシリコン窒化膜上には、10nm程度のシリコン酸化膜6を形成し、続いて砒素を含有したポリシリコン膜7を200nm程度の膜厚で形成する。次に、反応性イオンエッチング法を用いて、このポリシリコン膜7を半導体基板1表面から1μm程度の深さまでエッチングする。その後、露出しているトレンチ側壁のシリコン酸化膜6およびシリコン窒化膜を、ウェットエッチング法により順次除去して、図4に示す構造を得る。ポリシリコン膜7と半導体基板1との間に設けられたシリコン酸化膜6は、キャパシタ絶縁膜に相当する。

【0018】

露出したトレンチの側壁およびポリシリコン膜7表面を含む全面に、8nm程度の膜厚で酸化膜(図示せず)を形成し、さらに50nm程度のシリコン酸化膜を形成する。酸化膜を1000℃の窒素雰囲気中で20分程度凝縮した後、反応性イオンエッチング法を用いて、これを選択的に除去する。その結果、図5に示すように、トレンチ内面には、シリコン窒化膜3およびポリシリコン膜7が部分的に露出される。トレンチの側面に形成された酸化膜は、カラー絶縁膜9として機能する。

【0019】

次に、砒素を含有したポリシリコン膜10を200nm程度の膜厚で全面に形成する。得られたポリシリコン膜10を、反応性イオンエッチング法を用いて、図6に示すように半導体基板1の表面から高さ約30nmまでエッチングする。このポリシリコン膜10によって、トレンチキャパシタのストレージ電極が構成される。ストレージ電極は、燐を含有するポリシリコン膜10により構成してもよい。

【0020】

エッチング後のポリシリコン膜10の表面は、半導体基板1の表面よりも上方に位置することが望まれる。これは、後の工程でポリシリコン膜10上に形成されるシリコン窒化膜19を除去可能とするためである。半導体基板1の表面からの高さは、0〜100nm程度が好ましく、0〜30nm程度がより好ましい。

【0021】

続いて、ウェットエッチング法にてカラー絶縁膜9の上部を除去して、トレンチ側面の半導体基板1を露出する。露出される半導体基板1の深さ、すなわち半導体基板1の表面からエッチング後のカラー絶縁膜9の表面までの距離は、50〜100nm程度であることが好ましく、例えば60nm程度とすることができる。このエッチングの結果、半導体基板1、カラー絶縁膜9、およびポリシリコン膜10により画定された凹部が形成される。この凹部内には、ストレージ電極からの半導体基板への不純物の拡散を防止するとともに、シリサイド膜の形成を確実にするための積層膜が設けられる。露出された半導体基板1の側面の距離が50nm未満の場合には、後のリセス工程で凹部が除去されてしまう。一方、100nmを越えると、トランジスタを構成するために半導体基板に形成されるソース/ドレイン拡散領域より深くなってしまう。この場合には、ストレージノード側の接合面積が広くなることによって接合リークが増加し、電荷保持時間が短くなる。さらに、ストレージ電極から拡散する不純物がAsの場合には、接合が急峻になって接合リークが増加し、電荷保持時間が短くなるといった不都合が生じるおそれがある。

【0022】

次に、図7に示すように、3nm程度のシリコン窒化膜19および200nm程度のポリシリコン膜20を順次形成する。シリコン窒化膜19は、ストレージ電極中の不純物が半導体基板1中に拡散するのを防止する。このため、不純物の種類や濃度等に応じて、その拡散を十分に防止できる膜厚で形成すればよい。例えば、3nm程度以上の膜厚であれば、不純物がストレージ電極から半導体基板1へ拡散するのを実質的に防止することができる。しかしながら、シリコン窒化膜19の膜厚が厚すぎる場合には、後の工程でその上にシリサイド膜を形成して、ストレージ電極とトランジスタとを電気的に接続するのが困難となる。これらを考慮して、シリコン窒化膜19の厚さを決定することが望まれる。少なくとも1nm程度の膜厚が確保できれば、トランジスタの性能に影響を及ぼさない程度まで、ポリシリコン膜10からの不純物の拡散を低減することができる。シリコン窒化膜19は、同程度の膜厚のシリコン酸化膜に置き換えることが可能である。また、シリコン窒化膜19の不純物拡散防止の機能を損なわない程度であれば、ポリシリコン膜20には、砒素、燐等の不純物がドープされていてもよい。

【0023】

その後、反応性イオンエッチング法を用いて、シリコン窒化膜19およびポリシリコン膜20を、半導体基板1表面から30nm程度の深さまでエッチングする。このエッチングによって、図8に示すように、カラー絶縁膜9上に、シリコン窒化膜19を介してポリシリコン膜20が設けられた構造が得られる。すなわち、半導体基板1、カラー絶縁膜9およびポリシリコン膜10によって画定された凹部内には、シリコン窒化膜19とポリシリコン膜20との積層膜が設けられる。シリコン窒化膜19は、ポリシリコン膜20と半導体基板1とを隔離するとともに、ポリシリコン膜20とストレージ電極としてのポリシリコン膜10とを隔離する。したがって、このシリコン窒化膜19は、隔離絶縁膜と呼ぶことができる。一方、ポリシリコン膜20は、シリサイド膜の形成を確実にするといった作用を有する。こうした2つの膜の効果を十分に発揮させるため、シリコン窒化膜19を介して凹部内にポリシリコン膜20が残置されるように、エッチングが行なわれる。このエッチング深さは、通常、半導体基板1の表面から15〜45nm程度の範囲内である。

【0024】

エッチング後には、250nm程度のシリコン酸化膜12を全面に堆積する。さらに、光学的パターニング法および反応性イオンエッチング法を用いて、図9に示すように半導体基板1表面から深さ約300nmの素子分離溝を形成する。

【0025】

ウェットエッチング法によりシリコン酸化膜12を除去した後、400nm程度膜厚で酸化膜を堆積する。シリコン窒化膜3上の酸化膜を平坦化法により除去し、さらに、ウェットエッチング法を用いて、半導体基板表面から高さ約30nmまで酸化膜をエッチバックする。その後、ウェットエッチング法によりシリコン窒化膜3を除去して、図10に示すように素子分離層13を形成する。

【0026】

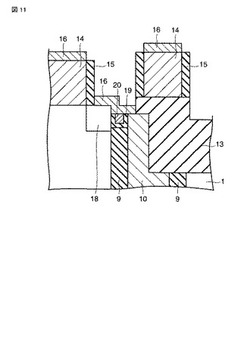

半導体基板1上および素子分離層13上には、常法によりゲート電極配線14および酸化膜15を形成する。酸化膜15および素子分離層13を反応性イオンエッチング法によりエッチングして、ポリシリコン膜10、ポリシリコン膜20および半導体基板1を露出する。半導体基板1には、ゲート電極配線14および側壁酸化膜15からなるゲート部を設け、常法により不純物をドープしてソース/ドレイン拡散領域18を形成する。ソース/ドレイン拡散領域18が形成された半導体基板1上から、ポリシリコン膜20上を経由してポリシリコン膜10上にわたってシリサイド膜16を形成して、トレンチ内部に形成されたストレージ電極となるポリシリコン膜10とトランジスタのソース/ドレイン拡散領域18とを電気的に接続する。図示するように、シリサイド膜16は、ゲート電極配線14上にも形成される。

【0027】

図11に示されるように、本発明の実施形態にかかる半導体装置においては、トレンチキャパシタのカラー絶縁膜9の上部には、シリコン酸化膜19により半導体基板1およびストレージ電極から隔離されて、ポリシリコン膜20が設けられている。トレンチキャパシタのストレージ電極としてのポリシリコン膜10と、トランジスタのソース/ドレイン拡散領域18との間に存在する絶縁膜部分の面積は減少し、その代わりに導電膜であるポリシリコン膜20が設けられたということができる。その結果、ストレージ電極とソース/ドレイン拡散領域とを電気的に接続するためのシリサイド膜を形成できなくなるといった問題は回避される。

【0028】

シリコン窒化膜19は、ストレージ電極としてのポリシリコン膜10とポリシリコン膜20との間を隔離し、さらに、ポリシリコン膜20と半導体基板1との間も隔離する。このように、ストレージ電極としてのポリシリコン膜10と半導体基板1との間には、シリコン窒化膜19が二重に形成されることとなる。これによって、ストレージ電極から砒素が拡散して半導体基板内に不純物拡散層が発生することは、極力低減することができる。その結果、不純物拡散層とトランジスタのソース/ドレイン拡散領域とのSub Vthが低下することはなく、電荷保持特性の劣化を防ぐことが可能となる。

【0029】

同様の構成の半導体装置を従来の方法により製造する場合には、ストレージ電極とトランジスタのソース/ドレイン拡散領域との距離を制御することができないため、図1または図2に示したような不都合が生じる。

図12乃至図16を参照して、従来の半導体装置の製造方法の一例を説明する。

上述と同様の手法により図5に示す構造を得た後、砒素を含有したポリシリコン膜10を200nm程度の膜厚で全面に形成する。このポリシリコン膜12は、反応性イオンエッチング法により、図12に示すように半導体基板1表面から約60nmの深さまでエッチングされる。

【0030】

トレンチの側面のカラー絶縁膜9は、ウェットエッチング法により20nm程度エッチングして、膜厚を減少させる。図13に示すように、半導体基板1表面から60nm程度の深さまで、このカラー絶縁膜9の膜厚を10nm程度まで薄膜化する。

砒素を含有したポリシリコン膜11を200nm程度の膜厚で全面に形成し、反応性イオンエッチング法を用いて、図14に示すように、このポリシリコン膜11を半導体基板1表面から30nm程度エッチングする。

【0031】

エッチング後には、250nm程度の膜厚でシリコン酸化膜12を全面に堆積する。さらに、光学的パターニング法および反応性イオンエッチング法を用いて、図15に示すように半導体基板表面から深さ約300nmの素子分離溝を形成する。この素子分離溝内には、上述と同様の手法によりシリコン酸化膜13を埋め込んで、図16に示すように素子分離層13を形成する。

【0032】

その後は、上述と同様にしてゲート電極配線および絶縁膜が形成され、半導体基板にはソース/ドレイン拡散領域が設けられる。さらに、同様の加工を行なって、ソース/ドレイン拡散領域18が形成された半導体基板1上、ポリシリコン膜20上、およびポリシリコン膜10上には、シリサイド膜16を形成し、ゲート電極配線14上にもシリサイド膜16を形成する。

【0033】

従来の手法では、カラー絶縁膜9を、ウェットエッチング法を用いて半導体基板表面から60nm程度の深さまで薄膜化する際に、エッチング量を制御して所望の膜厚を確保することが難しい。エッチング量が少ない場合には、図1に示したようにトレンチ上部のカラー絶縁膜9が厚くなる。その結果、ポリシリコン膜11と半導体基板1間距離が長くなってコンタクトが取れず、電気的に接続することができない。一方、エッチング量が多い場合には、図2に示したようにトレンチ上部のカラー絶縁膜9が完全に除去されてしまい、ポリシリコン膜11から砒素が拡散して不純物拡散領域17が形成される。この不純物拡散領域とトランジスタのソース/ドレイン拡散領域18とのSub Vthが低下して、電荷保持時間が短くなる。

【0034】

本発明の実施形態にかかる半導体装置は、こうした不都合を回避することが可能となった。

【図面の簡単な説明】

【0035】

【図1】従来の半導体装置を表わす断面図。

【図2】従来の半導体装置を表わす断面図。

【図3】本発明の一実施形態にかかる半導体装置の製造方法を表わす工程断面図。

【図4】図3に続く工程を表わす断面図。

【図5】図4に続く工程を表わす断面図。

【図6】図5に続く工程を表わす断面図。

【図7】図6に続く工程を表わす断面図。

【図8】図7に続く工程を表わす断面図。

【図9】図8に続く工程を表わす断面図。

【図10】図9に続く工程を表わす断面図。

【図11】図10に続く工程を表わす断面図。

【図12】従来の半導体装置の製造方法を表わす工程断面図。

【図13】図12に続く工程を表わす断面図。

【図14】図13に続く工程を表わす断面図。

【図15】図14に続く工程を表わす断面図。

【図16】図15に続く工程を表わす断面図。

【符号の説明】

【0036】

1…半導体基板; 3,15,19…シリコン窒化膜

4,6,12,13…シリコン酸化膜

7,10,11…砒素を含有するポリシリコン膜; 9…カラー絶縁膜

14…ゲート電極配線; 16…シリサイド膜; 17…不純物拡散領域

18…ソース/ドレイン拡散領域; 20…ポリシリコン膜。

【技術分野】

【0001】

本発明は、半導体装置およびその製造方法に係り、特に、ダイナミックランダムアクセス(DRAM)メモリのトレンチキャパシタおよびその製造方法に関する。

【背景技術】

【0002】

DRAMのメモリセルは、キャパシタとトランスファゲート用のMOSトランジスタから構成されている。DRAMの集積度を上げるためには、より小さな面積でより大きな容量のキャパシタを形成することが望ましい。その一つの手段として、シリコン基板に設けたトレンチを用いてキャパシタを形成するトレンチキャパシタが挙げられる。

【0003】

トレンチキャパシタを有するDRAMセルにおいて、トランジスタのソース/ドレイン拡散領域と蓄積キャパシタのストレージ電極とを、シリサイド等の導電膜により接続することが提案されている(例えば、特許文献1参照)。

【0004】

深いトレンチ(Deep Trench:DT)にキャパシタを形成したDRAMを形成する場合、一般に、DTを形成後にDT内の上部領域を除く領域には、膜厚の薄いキャパシタ絶縁膜が形成され、上部領域には比較的膜厚の厚いカラー絶縁膜が形成される。これらの絶縁膜を介して、ストレージ電極がDT内に埋め込み形成される。蓄積キャパシタのストレージ電極としては、不純物がドープされたポリシリコン膜が一般的に用いられ、こうしたストレージ電極とトランジスタのソース/ドレイン拡散領域とを接続するシリサイド膜等の導電膜は、カラー絶縁膜の上に形成されることとなる。

【0005】

シリサイド膜等の導電膜は、ストレージ電極とソース/ドレイン拡散領域とを確実に接続することが求められる。また、トランジスタの性能の劣化を避けるためには、このトランジスタが形成された半導体基板中にストレージ電極中の不純物が拡散することは、極力避けることが望まれる。

【特許文献1】特開昭62−213273号公報

【発明の開示】

【発明が解決しようとする課題】

【0006】

本発明は、優れたトランジスタ特性を有するDRAMが高い集積度で形成された半導体装置、およびその製造方法を提供することを目的とする。

【課題を解決するための手段】

【0007】

本発明の一態様にかかる半導体装置は、半導体基板に設けられたトレンチと、前記トレンチの内壁下側に設けられたキャパシタ絶縁膜と、前記トレンチの内壁上側に設けられたカラー絶縁膜と前記トレンチ内に埋め込まれたストレージ電極とを有するトレンチキャパシタ、

半導体基板に設けられたMOSトランジスタ、および

前記MOSトランジスタのソース/ドレイン拡散領域の一方と前記トレンチキャパシタの前記ストレージ電極とを接続するシリサイド膜を有する半導体装置であって、

前記カラー絶縁膜は上部に導電膜を有し、

前記導電膜は、隔離絶縁膜によって前記半導体基板、前記ストレージ電極、および前記カラー絶縁膜から隔離されていることを特徴。

【0008】

本発明の一態様にかかる半導体装置の製造方法は、半導体基板にトレンチを形成する工程と、

前記トレンチ側面の所定の高さまでキャパシタ絶縁膜を形成する工程と、

前記キャパシタ絶縁膜より上のトレンチ側面にカラー絶縁膜を形成する工程と、

前記トレンチ内および前記半導体基板の上に、不純物を含有したポリシリコン膜を形成する工程と、

前記ポリシリコン膜をエッチング除去して前記トレンチ内に残置し、ストレージ電極を形成する工程と、

前記カラー絶縁膜の上部を除去して、前記半導体基板および前記ストレージ電極を側面に露出することにより凹部を形成する工程と、

全面に隔離絶縁膜を介して導電膜を形成する工程と、

前記導電膜、前記隔離絶縁膜、および前記ストレージ電極をエッチングして、前記凹部内に前記隔離絶縁膜を介して前記導電膜を残置する工程と、

前記ストレージ電極上に素子分離層を形成する工程と、

前記半導体基板上にゲート電極配線および側壁酸化膜を含むゲート部を形成する工程と、

前記ゲート部を挟んで前記半導体基板上にソース/ドレイン拡散領域を形成する工程と、

前記ソース/ドレイン拡散領域の一方と前記ストレージ電極とを接続するシリサイド膜を形成する工程とを具備することを特徴とする。

【発明の効果】

【0009】

本発明の一態様によれば、優れたトランジスタ特性を有するDRAMが高い集積度で形成された半導体装置、およびその製造方法が提供される。

【発明を実施するための最良の形態】

【0010】

本発明者らは、トレンチキャパシタを有するDRAMセルにおいて、トランジスタのソース/ドレイン拡散領域と蓄積キャパシタのストレージ電極とを、シリサイド膜により接続した従来の半導体装置について鋭意検討した結果、次のような知見を得た。

【0011】

すなわち、こうした構造の半導体装置においては、トランジスタのソース/ドレイン拡散領域と蓄積キャパシタのストレージ電極とを接続するシリサイド膜は、カラー絶縁膜の上に形成されることから、このカラー絶縁膜の膜厚が半導体装置の特性に影響を及ぼす。具体的には、カラー絶縁膜の膜厚が厚い場合には、図1に示されるようにストレージ電極22とソース/ドレイン拡散領域18との距離が長くなって、シリサイド膜16で確実に接続することができない。

【0012】

なお、図1は従来の構造を示しており、半導体基板1に設けられたトレンチ内には、カラー絶縁膜9を介して、不純物がドープされたポリシリコン膜10およびポリシリコン膜11が埋め込まれ、これらポリシリコン膜がストレージ電極22を構成する。ストレージ電極22およびカラー絶縁膜9は部分的に除去されて素子分離層13が設けられ、この上にはゲート電極配線14が形成される。ゲート電極配線14の側面には酸化膜15が設けられ、上面にはシリサイド膜16が形成される。半導体基板1にはMOSトランジスタが形成され、このトランジスタのソース/ドレイン拡散領域18は、シリサイド膜16によって、ストレージ電極22に接続されなければならない。

【0013】

カラー絶縁膜9の膜厚を薄くすれば、シリサイド膜16が不連続になるといった問題を回避することができる。しかしながら、カラー絶縁膜9が存在しない場合には、図2に示すようにポリシリコン膜11から不純物が半導体基板1に拡散して、不純物拡散領域17が形成される。この不純物拡散領域17とトランジスタのソース拡散領域18とのSub Vthが低下して、電荷保持特性の低下につながる。

【0014】

トランジスタのソース/ドレイン拡散領域は、シリサイド膜によってストレージ電極に確実に接続されなければならず、しかも、ストレージ電極中の不純物が半導体基板へ拡散するのは極力回避すべきである。本発明の実施形態は、これを可能としたものである。

【0015】

図3乃至図11に、本発明の実施形態にかかる半導体装置の製造方法を表わす断面図を示す。

【0016】

まず、図3に示すように、半導体基板1上に2nm程度の酸化膜(図示せず)を形成し、220nm程度のシリコン窒化膜3、および1600nm程度の酸化膜4を順次堆積する。続いて、光学的パターニング法および反応性イオンエッチング法を用いて、酸化膜4、シリコン窒化膜3、および酸化膜をパターンニングする。さらに、酸化膜4をマスクとして用いて半導体基板を6μm程度の深さまでエッチングすることにより、トレンチパターンを形成する。

【0017】

ウェットエッチング法を用いて酸化膜4を除去した後、全面に5nm程度の膜厚のシリコン窒化膜(図示せず)を形成する。このシリコン窒化膜上には、10nm程度のシリコン酸化膜6を形成し、続いて砒素を含有したポリシリコン膜7を200nm程度の膜厚で形成する。次に、反応性イオンエッチング法を用いて、このポリシリコン膜7を半導体基板1表面から1μm程度の深さまでエッチングする。その後、露出しているトレンチ側壁のシリコン酸化膜6およびシリコン窒化膜を、ウェットエッチング法により順次除去して、図4に示す構造を得る。ポリシリコン膜7と半導体基板1との間に設けられたシリコン酸化膜6は、キャパシタ絶縁膜に相当する。

【0018】

露出したトレンチの側壁およびポリシリコン膜7表面を含む全面に、8nm程度の膜厚で酸化膜(図示せず)を形成し、さらに50nm程度のシリコン酸化膜を形成する。酸化膜を1000℃の窒素雰囲気中で20分程度凝縮した後、反応性イオンエッチング法を用いて、これを選択的に除去する。その結果、図5に示すように、トレンチ内面には、シリコン窒化膜3およびポリシリコン膜7が部分的に露出される。トレンチの側面に形成された酸化膜は、カラー絶縁膜9として機能する。

【0019】

次に、砒素を含有したポリシリコン膜10を200nm程度の膜厚で全面に形成する。得られたポリシリコン膜10を、反応性イオンエッチング法を用いて、図6に示すように半導体基板1の表面から高さ約30nmまでエッチングする。このポリシリコン膜10によって、トレンチキャパシタのストレージ電極が構成される。ストレージ電極は、燐を含有するポリシリコン膜10により構成してもよい。

【0020】

エッチング後のポリシリコン膜10の表面は、半導体基板1の表面よりも上方に位置することが望まれる。これは、後の工程でポリシリコン膜10上に形成されるシリコン窒化膜19を除去可能とするためである。半導体基板1の表面からの高さは、0〜100nm程度が好ましく、0〜30nm程度がより好ましい。

【0021】

続いて、ウェットエッチング法にてカラー絶縁膜9の上部を除去して、トレンチ側面の半導体基板1を露出する。露出される半導体基板1の深さ、すなわち半導体基板1の表面からエッチング後のカラー絶縁膜9の表面までの距離は、50〜100nm程度であることが好ましく、例えば60nm程度とすることができる。このエッチングの結果、半導体基板1、カラー絶縁膜9、およびポリシリコン膜10により画定された凹部が形成される。この凹部内には、ストレージ電極からの半導体基板への不純物の拡散を防止するとともに、シリサイド膜の形成を確実にするための積層膜が設けられる。露出された半導体基板1の側面の距離が50nm未満の場合には、後のリセス工程で凹部が除去されてしまう。一方、100nmを越えると、トランジスタを構成するために半導体基板に形成されるソース/ドレイン拡散領域より深くなってしまう。この場合には、ストレージノード側の接合面積が広くなることによって接合リークが増加し、電荷保持時間が短くなる。さらに、ストレージ電極から拡散する不純物がAsの場合には、接合が急峻になって接合リークが増加し、電荷保持時間が短くなるといった不都合が生じるおそれがある。

【0022】

次に、図7に示すように、3nm程度のシリコン窒化膜19および200nm程度のポリシリコン膜20を順次形成する。シリコン窒化膜19は、ストレージ電極中の不純物が半導体基板1中に拡散するのを防止する。このため、不純物の種類や濃度等に応じて、その拡散を十分に防止できる膜厚で形成すればよい。例えば、3nm程度以上の膜厚であれば、不純物がストレージ電極から半導体基板1へ拡散するのを実質的に防止することができる。しかしながら、シリコン窒化膜19の膜厚が厚すぎる場合には、後の工程でその上にシリサイド膜を形成して、ストレージ電極とトランジスタとを電気的に接続するのが困難となる。これらを考慮して、シリコン窒化膜19の厚さを決定することが望まれる。少なくとも1nm程度の膜厚が確保できれば、トランジスタの性能に影響を及ぼさない程度まで、ポリシリコン膜10からの不純物の拡散を低減することができる。シリコン窒化膜19は、同程度の膜厚のシリコン酸化膜に置き換えることが可能である。また、シリコン窒化膜19の不純物拡散防止の機能を損なわない程度であれば、ポリシリコン膜20には、砒素、燐等の不純物がドープされていてもよい。

【0023】

その後、反応性イオンエッチング法を用いて、シリコン窒化膜19およびポリシリコン膜20を、半導体基板1表面から30nm程度の深さまでエッチングする。このエッチングによって、図8に示すように、カラー絶縁膜9上に、シリコン窒化膜19を介してポリシリコン膜20が設けられた構造が得られる。すなわち、半導体基板1、カラー絶縁膜9およびポリシリコン膜10によって画定された凹部内には、シリコン窒化膜19とポリシリコン膜20との積層膜が設けられる。シリコン窒化膜19は、ポリシリコン膜20と半導体基板1とを隔離するとともに、ポリシリコン膜20とストレージ電極としてのポリシリコン膜10とを隔離する。したがって、このシリコン窒化膜19は、隔離絶縁膜と呼ぶことができる。一方、ポリシリコン膜20は、シリサイド膜の形成を確実にするといった作用を有する。こうした2つの膜の効果を十分に発揮させるため、シリコン窒化膜19を介して凹部内にポリシリコン膜20が残置されるように、エッチングが行なわれる。このエッチング深さは、通常、半導体基板1の表面から15〜45nm程度の範囲内である。

【0024】

エッチング後には、250nm程度のシリコン酸化膜12を全面に堆積する。さらに、光学的パターニング法および反応性イオンエッチング法を用いて、図9に示すように半導体基板1表面から深さ約300nmの素子分離溝を形成する。

【0025】

ウェットエッチング法によりシリコン酸化膜12を除去した後、400nm程度膜厚で酸化膜を堆積する。シリコン窒化膜3上の酸化膜を平坦化法により除去し、さらに、ウェットエッチング法を用いて、半導体基板表面から高さ約30nmまで酸化膜をエッチバックする。その後、ウェットエッチング法によりシリコン窒化膜3を除去して、図10に示すように素子分離層13を形成する。

【0026】

半導体基板1上および素子分離層13上には、常法によりゲート電極配線14および酸化膜15を形成する。酸化膜15および素子分離層13を反応性イオンエッチング法によりエッチングして、ポリシリコン膜10、ポリシリコン膜20および半導体基板1を露出する。半導体基板1には、ゲート電極配線14および側壁酸化膜15からなるゲート部を設け、常法により不純物をドープしてソース/ドレイン拡散領域18を形成する。ソース/ドレイン拡散領域18が形成された半導体基板1上から、ポリシリコン膜20上を経由してポリシリコン膜10上にわたってシリサイド膜16を形成して、トレンチ内部に形成されたストレージ電極となるポリシリコン膜10とトランジスタのソース/ドレイン拡散領域18とを電気的に接続する。図示するように、シリサイド膜16は、ゲート電極配線14上にも形成される。

【0027】

図11に示されるように、本発明の実施形態にかかる半導体装置においては、トレンチキャパシタのカラー絶縁膜9の上部には、シリコン酸化膜19により半導体基板1およびストレージ電極から隔離されて、ポリシリコン膜20が設けられている。トレンチキャパシタのストレージ電極としてのポリシリコン膜10と、トランジスタのソース/ドレイン拡散領域18との間に存在する絶縁膜部分の面積は減少し、その代わりに導電膜であるポリシリコン膜20が設けられたということができる。その結果、ストレージ電極とソース/ドレイン拡散領域とを電気的に接続するためのシリサイド膜を形成できなくなるといった問題は回避される。

【0028】

シリコン窒化膜19は、ストレージ電極としてのポリシリコン膜10とポリシリコン膜20との間を隔離し、さらに、ポリシリコン膜20と半導体基板1との間も隔離する。このように、ストレージ電極としてのポリシリコン膜10と半導体基板1との間には、シリコン窒化膜19が二重に形成されることとなる。これによって、ストレージ電極から砒素が拡散して半導体基板内に不純物拡散層が発生することは、極力低減することができる。その結果、不純物拡散層とトランジスタのソース/ドレイン拡散領域とのSub Vthが低下することはなく、電荷保持特性の劣化を防ぐことが可能となる。

【0029】

同様の構成の半導体装置を従来の方法により製造する場合には、ストレージ電極とトランジスタのソース/ドレイン拡散領域との距離を制御することができないため、図1または図2に示したような不都合が生じる。

図12乃至図16を参照して、従来の半導体装置の製造方法の一例を説明する。

上述と同様の手法により図5に示す構造を得た後、砒素を含有したポリシリコン膜10を200nm程度の膜厚で全面に形成する。このポリシリコン膜12は、反応性イオンエッチング法により、図12に示すように半導体基板1表面から約60nmの深さまでエッチングされる。

【0030】

トレンチの側面のカラー絶縁膜9は、ウェットエッチング法により20nm程度エッチングして、膜厚を減少させる。図13に示すように、半導体基板1表面から60nm程度の深さまで、このカラー絶縁膜9の膜厚を10nm程度まで薄膜化する。

砒素を含有したポリシリコン膜11を200nm程度の膜厚で全面に形成し、反応性イオンエッチング法を用いて、図14に示すように、このポリシリコン膜11を半導体基板1表面から30nm程度エッチングする。

【0031】

エッチング後には、250nm程度の膜厚でシリコン酸化膜12を全面に堆積する。さらに、光学的パターニング法および反応性イオンエッチング法を用いて、図15に示すように半導体基板表面から深さ約300nmの素子分離溝を形成する。この素子分離溝内には、上述と同様の手法によりシリコン酸化膜13を埋め込んで、図16に示すように素子分離層13を形成する。

【0032】

その後は、上述と同様にしてゲート電極配線および絶縁膜が形成され、半導体基板にはソース/ドレイン拡散領域が設けられる。さらに、同様の加工を行なって、ソース/ドレイン拡散領域18が形成された半導体基板1上、ポリシリコン膜20上、およびポリシリコン膜10上には、シリサイド膜16を形成し、ゲート電極配線14上にもシリサイド膜16を形成する。

【0033】

従来の手法では、カラー絶縁膜9を、ウェットエッチング法を用いて半導体基板表面から60nm程度の深さまで薄膜化する際に、エッチング量を制御して所望の膜厚を確保することが難しい。エッチング量が少ない場合には、図1に示したようにトレンチ上部のカラー絶縁膜9が厚くなる。その結果、ポリシリコン膜11と半導体基板1間距離が長くなってコンタクトが取れず、電気的に接続することができない。一方、エッチング量が多い場合には、図2に示したようにトレンチ上部のカラー絶縁膜9が完全に除去されてしまい、ポリシリコン膜11から砒素が拡散して不純物拡散領域17が形成される。この不純物拡散領域とトランジスタのソース/ドレイン拡散領域18とのSub Vthが低下して、電荷保持時間が短くなる。

【0034】

本発明の実施形態にかかる半導体装置は、こうした不都合を回避することが可能となった。

【図面の簡単な説明】

【0035】

【図1】従来の半導体装置を表わす断面図。

【図2】従来の半導体装置を表わす断面図。

【図3】本発明の一実施形態にかかる半導体装置の製造方法を表わす工程断面図。

【図4】図3に続く工程を表わす断面図。

【図5】図4に続く工程を表わす断面図。

【図6】図5に続く工程を表わす断面図。

【図7】図6に続く工程を表わす断面図。

【図8】図7に続く工程を表わす断面図。

【図9】図8に続く工程を表わす断面図。

【図10】図9に続く工程を表わす断面図。

【図11】図10に続く工程を表わす断面図。

【図12】従来の半導体装置の製造方法を表わす工程断面図。

【図13】図12に続く工程を表わす断面図。

【図14】図13に続く工程を表わす断面図。

【図15】図14に続く工程を表わす断面図。

【図16】図15に続く工程を表わす断面図。

【符号の説明】

【0036】

1…半導体基板; 3,15,19…シリコン窒化膜

4,6,12,13…シリコン酸化膜

7,10,11…砒素を含有するポリシリコン膜; 9…カラー絶縁膜

14…ゲート電極配線; 16…シリサイド膜; 17…不純物拡散領域

18…ソース/ドレイン拡散領域; 20…ポリシリコン膜。

【特許請求の範囲】

【請求項1】

半導体基板に設けられたトレンチと、前記トレンチの内壁下側に設けられたキャパシタ絶縁膜と、前記トレンチの内壁上側に設けられたカラー絶縁膜と前記トレンチ内に埋め込まれたストレージ電極とを有するトレンチキャパシタ、

半導体基板に設けられたMOSトランジスタ、および

前記MOSトランジスタのソース/ドレイン拡散領域の一方と前記トレンチキャパシタの前記ストレージ電極とを接続するシリサイド膜を有する半導体装置であって、

前記カラー絶縁膜は上部に導電膜を有し、

前記導電膜は、隔離絶縁膜によって前記半導体基板、前記ストレージ電極、および前記カラー絶縁膜から隔離されていることを特徴とする半導体装置。

【請求項2】

前記ストレージ電極は、砒素または燐を含有するポリシリコン膜からなることを特徴とする請求項1に記載の半導体装置。

【請求項3】

前記隔離絶縁膜は、シリコン窒化膜またはシリコン酸化膜からなることを特徴とする請求項1または2に記載する半導体装置。

【請求項4】

前記導電膜は、砒素または燐を含有するポリシリコン膜、または不純物を含有しないポリシリコン膜からなることを特徴とする請求項1乃至3のいずれか1項に記載の半導体装置。

【請求項5】

半導体基板にトレンチを形成する工程と、

前記トレンチ側面の所定の高さまでキャパシタ絶縁膜を形成する工程と、

前記キャパシタ絶縁膜より上のトレンチ側面にカラー絶縁膜を形成する工程と、

前記トレンチ内および前記半導体基板の上に、不純物を含有したポリシリコン膜を形成する工程と、

前記ポリシリコン膜をエッチング除去して前記トレンチ内に残置し、ストレージ電極を形成する工程と、

前記カラー絶縁膜の上部を除去して、前記半導体基板および前記ストレージ電極を側面に露出することにより凹部を形成する工程と、

全面に隔離絶縁膜を介して導電膜を形成する工程と、

前記導電膜、前記隔離絶縁膜、および前記ストレージ電極をエッチングして、前記凹部内に前記隔離絶縁膜を介して前記導電膜を残置する工程と、

前記ストレージ電極上に素子分離層を形成する工程と、

前記半導体基板上にゲート電極配線および側壁酸化膜を含むゲート部を形成する工程と、

前記ゲート部を挟んで前記半導体基板上にソース/ドレイン拡散領域を形成する工程と、

前記ソース/ドレイン拡散領域の一方と前記ストレージ電極とを接続するシリサイド膜を形成する工程と

を具備することを特徴とする半導体装置の製造方法。

【請求項1】

半導体基板に設けられたトレンチと、前記トレンチの内壁下側に設けられたキャパシタ絶縁膜と、前記トレンチの内壁上側に設けられたカラー絶縁膜と前記トレンチ内に埋め込まれたストレージ電極とを有するトレンチキャパシタ、

半導体基板に設けられたMOSトランジスタ、および

前記MOSトランジスタのソース/ドレイン拡散領域の一方と前記トレンチキャパシタの前記ストレージ電極とを接続するシリサイド膜を有する半導体装置であって、

前記カラー絶縁膜は上部に導電膜を有し、

前記導電膜は、隔離絶縁膜によって前記半導体基板、前記ストレージ電極、および前記カラー絶縁膜から隔離されていることを特徴とする半導体装置。

【請求項2】

前記ストレージ電極は、砒素または燐を含有するポリシリコン膜からなることを特徴とする請求項1に記載の半導体装置。

【請求項3】

前記隔離絶縁膜は、シリコン窒化膜またはシリコン酸化膜からなることを特徴とする請求項1または2に記載する半導体装置。

【請求項4】

前記導電膜は、砒素または燐を含有するポリシリコン膜、または不純物を含有しないポリシリコン膜からなることを特徴とする請求項1乃至3のいずれか1項に記載の半導体装置。

【請求項5】

半導体基板にトレンチを形成する工程と、

前記トレンチ側面の所定の高さまでキャパシタ絶縁膜を形成する工程と、

前記キャパシタ絶縁膜より上のトレンチ側面にカラー絶縁膜を形成する工程と、

前記トレンチ内および前記半導体基板の上に、不純物を含有したポリシリコン膜を形成する工程と、

前記ポリシリコン膜をエッチング除去して前記トレンチ内に残置し、ストレージ電極を形成する工程と、

前記カラー絶縁膜の上部を除去して、前記半導体基板および前記ストレージ電極を側面に露出することにより凹部を形成する工程と、

全面に隔離絶縁膜を介して導電膜を形成する工程と、

前記導電膜、前記隔離絶縁膜、および前記ストレージ電極をエッチングして、前記凹部内に前記隔離絶縁膜を介して前記導電膜を残置する工程と、

前記ストレージ電極上に素子分離層を形成する工程と、

前記半導体基板上にゲート電極配線および側壁酸化膜を含むゲート部を形成する工程と、

前記ゲート部を挟んで前記半導体基板上にソース/ドレイン拡散領域を形成する工程と、

前記ソース/ドレイン拡散領域の一方と前記ストレージ電極とを接続するシリサイド膜を形成する工程と

を具備することを特徴とする半導体装置の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【公開番号】特開2007−36028(P2007−36028A)

【公開日】平成19年2月8日(2007.2.8)

【国際特許分類】

【出願番号】特願2005−219024(P2005−219024)

【出願日】平成17年7月28日(2005.7.28)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

【公開日】平成19年2月8日(2007.2.8)

【国際特許分類】

【出願日】平成17年7月28日(2005.7.28)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

[ Back to top ]