画像表示装置

【課題】互いに異なる電源電位を供給する2つの電源線のうち一方に生じる電源供給能力不足を抑制すること。

【解決手段】画像表示装置は、複数のデータ線と、それぞれ前記各データ線と交差する複数のスイッチ制御線と、2本の電源線およびそれぞれが前記複数のスイッチ制御線のうち1つに電位を出力する複数のスイッチ制御信号供給回路を含む垂直走査回路と、を含む。2本の電源線は互いに異なる2種類の電源電位を供給する。前記各スイッチ制御信号供給回路は、データ信号が前記複数のデータ線に供給されるタイミングにおいて、前記2種類の電源電位のどちらか一方に対応する電位を選択的に出力する。前記2種類の電源電位のうち、前記タイミングでより多くの前記スイッチ制御信号供給回路が出力する電位に対応する電源電位を供給する電源線の幅が、他方の電源電位を供給する電源線の幅より太い。

【解決手段】画像表示装置は、複数のデータ線と、それぞれ前記各データ線と交差する複数のスイッチ制御線と、2本の電源線およびそれぞれが前記複数のスイッチ制御線のうち1つに電位を出力する複数のスイッチ制御信号供給回路を含む垂直走査回路と、を含む。2本の電源線は互いに異なる2種類の電源電位を供給する。前記各スイッチ制御信号供給回路は、データ信号が前記複数のデータ線に供給されるタイミングにおいて、前記2種類の電源電位のどちらか一方に対応する電位を選択的に出力する。前記2種類の電源電位のうち、前記タイミングでより多くの前記スイッチ制御信号供給回路が出力する電位に対応する電源電位を供給する電源線の幅が、他方の電源電位を供給する電源線の幅より太い。

【発明の詳細な説明】

【技術分野】

【0001】

本発明はアクティブマトリクス方式を用いた画像表示装置、特にその画像表示装置に含まれる垂直走査回路に関する。

【背景技術】

【0002】

近年、液晶表示装置や有機EL表示装置などのアクティブマトリクス方式を用いた表示装置において、垂直走査回路をアレイ基板上に設けたものが開発されている。アレイ基板上には表示領域と垂直走査回路とが設けられ、垂直走査回路は表示領域とアレイ基板の端との間にある額縁領域に形成される。表示領域にはマトリクス状に配置された画素回路と、画素回路の列に対応して並ぶデータ線と、データ線に交差する複数のスイッチ制御線と、画素回路向け電源配線とが設けられている。

【0003】

図14は従来の有機EL表示装置の概要の一例を示す回路図である。図14には、垂直方向に並び、それぞれ画素回路の各行への電源供給を制御する有機EL表示装置が示されている。この有機EL表示装置には、電源線駆動回路PDVと、垂直走査回路YDVと、図中上下方向に延びるデータ線DATと、マトリクス状に配置された画素回路PCと、画素回路PCの行に対応して設けられる複数の画素回路駆動電源線PWRおよび複数のスイッチ制御線SCLと、を備えている。電源線駆動回路PDVは、図中上下方向(垂直方向)に延びる駆動用接地線PLと、垂直方向に延びる駆動用電源供給線PHと、駆動用接地線PLと駆動用電源供給線PHとの間に並んで配置されるバッファアンプBFPと、を含む。バッファアンプBFPには駆動用接地線PLと駆動用電源供給線PHとから電源電位が供給される。バッファアンプBFPの出力は、垂直方向に並ぶ画素回路駆動電源線PWRを経て画素回路PCに入力される。

【0004】

垂直走査回路YDVは、垂直方向に延びる低電源電位供給線VSSと、垂直方向に延びる高電源電位供給線VDDと、低電源電位供給線VSSと高電源電位供給線VDDとの間に並んで配置されるバッファアンプBF1と、を含む。バッファアンプBF1には低電源電位供給線VSSおよび高電源電位供給線VDDから電源が供給される。バッファアンプBF1の出力は、スイッチ制御線SCLを経てスイッチ制御信号として画素回路PCに入力される。各画素回路PCは、画素回路駆動電源線PWRに接続される駆動トランジスタDTRと、駆動トランジスタDTRを介して供給された電流により発光する発光素子ILと、データ線DATに基づく電位と画素回路駆動電源線PWRの電位との電位差によって駆動トランジスタDTRを制御する記憶容量CPPと、スイッチ制御線SCLにゲート電極が接続され、スイッチ制御信号により画素回路PCを選択する選択スイッチSTRと、を含む。選択スイッチSTRは薄膜トランジスタである。

【0005】

この有機EL表示装置では、走査された行の画素回路に対して電源を供給する画素回路駆動電源線PWRに対してのみ駆動用接地線PLからの電位が供給される。他の画素回路駆動電源線PWRには駆動用電源供給線PHからの電位が供給される。駆動用電源供給線PHから電位が供給されると、発光素子ILに向かって駆動用電源供給線PHに電流が流れる。結局、駆動用電源供給線PHには駆動用接地線PLより多くの電流が流れるため、それに応じて駆動用電源供給線PHは駆動用接地線PLより太くなっている。このような駆動用電源供給線PHが駆動用接地線PLより太い構成は、特許文献1に開示されている。

【0006】

一方、垂直走査回路YDVでは、スイッチ制御線SCLは選択スイッチSTRのゲート電極に接続されるため、電位が供給されてもスイッチ制御線SCLには定常的な電流はほとんど流れない。スイッチ制御線SCLに流れる電流は、主に電位が切り替わる際に寄生容量との間で充放電を行う際に生じるものと考えられている。表示装置では一定期間にスイッチ制御線SCLに供給する電位を高電位から低電位に切替する回数と低電位から高電位に切替する回数とは等しい。よって低電源電位供給線VSSと高電源電位供給線VDDとに流れる電流は同程度であり、それらの太さは同じとしていた。

【先行技術文献】

【特許文献】

【0007】

【特許文献1】特開2009−14796号公報

【発明の概要】

【発明が解決しようとする課題】

【0008】

近年、例えば表示装置を構成するアレイ基板の額縁領域を狭くするために、垂直走査回路内で電源電位を供給する線の幅が狭くなってきている。すると低電源電位供給線VSSと高電源電位供給線VDDとのうち一方の電源供給能力が不足し、例えば横スメアの発生のような表示品質の劣化が生じることがあった。

【0009】

本発明は上記課題を鑑みてなされたものであって、その目的は、スイッチ制御線に電位を供給する回路に互いに異なる電源電位を供給する2つの電源線のうち一方に生じる電源供給能力不足を抑制する画像表示装置を提供することにある。

【課題を解決するための手段】

【0010】

本出願において開示される発明のうち、代表的なものの概要を簡単に説明すれば、以下の通りである。

【0011】

(1)表示領域内に並んで設けられる複数のデータ線と、前記表示領域内に並んで設けられるとともにそれぞれ前記各データ線と交差する複数のスイッチ制御線と、2本の電源線および複数のスイッチ制御信号供給回路を含む垂直走査回路と、を含み、前記2本の電源線のうち一方は第1電源電位を供給し、前記2本の電源線のうち他方は第2電源電位を供給し、前記各スイッチ制御信号供給回路は、それぞれ前記複数のスイッチ制御線のうちの1つに対応して設けられ、データ信号が前記複数のデータ線に供給されるタイミングにおいて、前記第1電源電位に対応する電位、および、前記第2電源電位に対応する電位のいずれか一方を選択的に対応するスイッチ制御線に対して出力し、前記第1電源電位および前記第2電源電位のうち、前記タイミングでより多くの前記スイッチ制御信号供給回路が出力する電位に対応する電源電位を供給する電源線の幅が、他方の電源電位を供給する電源線の幅より太い、ことを特徴とする画像表示装置。

【0012】

(2)(1)において、前記第1電源電位および前記第2電源電位のうち、前記タイミングでより多くの前記スイッチ制御信号供給回路が出力する電位に対応する電源電位を供給する電源線の幅が、他方の電源電位を供給する電源線の幅の1.5倍以上である、ことを特徴とする画像表示装置。

【0013】

(3)(1)または(2)において、前記垂直走査回路の外に設けられ、前記第1電源電位を前記2つの電源線の一方に供給する外部電源線と、前記垂直走査回路の外に設けられ、前記第2電源電位を前記2つの電源線の他方に供給する外部電源線と、をさらに含み、前記第1電源電位および前記第2電源電位のうち、前記タイミングでより多くの前記スイッチ制御信号供給回路が出力する電位に対応する電源電位を供給する外部電源線の幅は、他方の電源電位を供給する外部電源線の幅より太い、ことを特徴とする画像表示装置。

【発明の効果】

【0014】

本発明によれば、スイッチ制御線に電位を供給する回路に互いに異なる電源電位を供給する2つの電源線のうち一方に生じる電源供給能力不足を抑制しつつ額縁領域に占める電源線領域を効率よく小さくすることができる。

【図面の簡単な説明】

【0015】

【図1】本発明の実施形態に係る有機EL表示装置の部品配置の一例を示す図である。

【図2】本発明の実施形態に係る有機EL表示装置の回路構成の一例を示す回路図である。

【図3】各画素回路の構成の一例を示す回路図である。

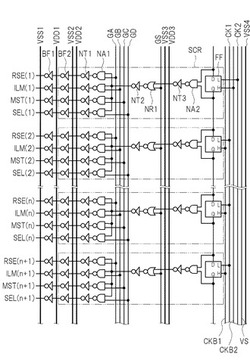

【図4】垂直走査回路の構成の一例を示す回路図である。

【図5】バッファアンプの回路構成を示す回路図である。

【図6】ある画素行において一水平期間に画素回路やRGB切替制御線に向けて供給される理想的な信号の電位と、スイッチ制御線やデータ線の電位とを示す波形図である。

【図7】第1の電源線と第2の電源線の太さを同じにした有機EL表示装置で起きる画質劣化の例を示す図である。

【図8】ある画素に発生する寄生容量と抵抗とを説明する図である。

【図9】データ信号印加タイミングにおけるスイッチ制御線に印加される電位を示す図である。

【図10】第1の電源線および第2の電源線に関する寄生容量と抵抗を示す図である。

【図11】図10に示す第1の電源線に関する寄生容量と抵抗の計算用モデルを示す図である。

【図12】各画素回路の他の構成を示す回路図である。

【図13】図12に示す画素回路を含む有機EL表示装置においてデータ信号印加タイミングにスイッチ制御線に印加される電位を示す図である。

【図14】従来の有機EL表示装置の概要の一例を示す回路図である。

【発明を実施するための形態】

【0016】

以下では、本発明の実施形態について図面に基づいて説明する。出現する構成要素のうち同一機能を有するものには同じ符号を付し、その説明を省略する。なお以下では、アクティブマトリクス方式を用いた画像表示装置の一種である有機EL表示装置に本発明を適用した場合について説明する。

【0017】

図1は、本発明の実施形態に係る有機EL表示装置の部品配置の一例を示す図である。有機EL表示装置は、物理的には、アレイ基板SUBと、フレキシブルプリント基板FPCと、ドライバ集積回路DICとを含む。アレイ基板SUB上には、画像を表示する表示領域DAが配置される。ここでアレイ基板SUB上の領域で、表示領域DA以外の領域を額縁領域という。垂直走査回路YDVは額縁領域のうち表示領域DAの右側に配置される。垂直走査回路YDVとドライバ集積回路DICとの間には、図示しない制御信号線が設けられている。フレキシブルプリント基板FPCからアレイ基板SUBに、高い方の電源電位と低い方の電源電位とが供給されている。高い方の電源電位は高電源電位入力線VDDWを介して、低い方の電源電位は低電源電位入力線VSSWを介して、垂直走査回路YDVに供給される。なお、低電源電位入力線VSSWおよび高電源電位入力線VDDWはアレイ基板SUBの外部からFPCと接触する端子を介して供給される電源を垂直走査回路YDVに供給する。これらをまとめて外部電源線と呼ぶ。

【0018】

図2は、本発明の第1の実施形態に係る有機EL表示装置の回路構成の一例を示す回路図である。有機EL表示装置は、回路構成として、表示領域DA内にマトリクス状に配置された画素回路PCと、画素回路PCの列に対応して設けられたデータ線DATと、画素回路PCの行(以下画素行Prowと記す)に対応して設けられたリセットスイッチ制御線RES、点灯スイッチ制御線ILM、検査スイッチ制御線MST、および選択スイッチ制御線SELと、画素回路駆動電源線PWRと、データ線DATに対応して設けられたRGB切替スイッチDSR,DSG,DSBと、統合データ線DATIと、データ線駆動回路XDVと、垂直走査回路YDVと、を含む。

【0019】

1つの画素回路PCは、赤、緑、青のうちいずれかの色を表示する。赤を表示する画素回路PC、緑を表示する画素回路PC、および青を表示する画素回路PCが1つずつ組合せられて1つの画素PXとなる。表示領域にはM列×N行の画素が配置されている。なお、m列目n行目の画素を表示する赤の画素回路PCをPCR(m,n)、緑の画素回路PCをPCG(m,n)、青の画素回路PCをPCB(m,n)と記す。また表示領域DA内には(3×M)列×N行の画素回路PCが並んでおり、同じ列に並んでいる画素回路PCは同じ色を表示する。

【0020】

画素回路PCの列に対応して、複数のデータ線DATが表示領域DA内をその列内を画素回路PCが並ぶ方向(垂直方向)に延びている。データ線DATは対応する画素回路PCに接続されている。同じデータ線DATに接続される画素回路PCは同じ色を表示する。以下では、m列の画素の列を構成する赤の画素回路PCの列に対応するデータ線DATをDATR(m)と、緑の画素回路PCの列に対応するデータ線DATをDATG(m)と、青の画素回路PCの列に対応するデータ線DATをDATB(m)と記す。また、表示領域DA内において垂直方向に並ぶN行の画素行Prowのそれぞれに対応して、N本のリセットスイッチ制御線RESと、N本の点灯スイッチ制御線ILMと、N本の検査スイッチ制御線MSTと、N本の選択スイッチ制御線SELとが画素回路PCの列が並ぶ方向に延びている。それぞれの画素行Prowは画素の行に対応する画素回路PCから構成される。ここで、n行目の画素行ProwをProw(n)と記し、Prow(n)に対応するリセットスイッチ制御線をRES(n)、点灯スイッチ制御線をILM(n)、検査スイッチ制御線MSTをMST(n)、選択スイッチ制御線SELをSEL(n)と記す。また、リセットスイッチ制御線RESと、点灯スイッチ制御線ILMと、検査スイッチ制御線MSTと、選択スイッチ制御線SELとは画素回路PC内のスイッチを制御する点で同じ機能を有しているため、以下では総称してスイッチ制御線と記す。表示領域DA内には(N×4)本のスイッチ制御線が並んでおり、スイッチ制御線はそれぞれ、各データ線DATと平面的に交差している。スイッチ制御線は垂直走査回路YDVに接続され、対応する画素行Prowに含まれる画素回路PCにスイッチを制御する信号(スイッチ制御信号)を供給する。また表示領域DA内には、各画素回路PCに電源を供給する画素回路駆動電源線PWRが設けられている。

【0021】

RGB切替スイッチDSR,DSG,DSBは薄膜トランジスタであって、画素の列に対応してそれぞれm個設けられている。RGB切替スイッチDSRのゲート電極にはRGB切替制御線CLAが接続され、RGB切替スイッチDSRのゲート電極にはRGB切替制御線CLBが接続され、RGB切替スイッチDSRのゲート電極にはRGB切替制御線CLCが接続される。

【0022】

画素のm列目に対応するデータ線DATのうち赤の画素回路PCに対応するデータ線DATR(m)の下端には、RGB切替スイッチDSRの一端が接続されている。RGB切替スイッチDSRの他端は、画素列に対応してM本設けられた統合データ線DATIのうちm列目の画素PXに対応する統合データ線DATIの一端と接続されている。同様に、データ線DATG(m)の下端はRGB切替スイッチDSGを介して対応する統合データ線DATIの一端と接続されており、データ線DATB(m)の下端はRGB切替スイッチDSBを介して対応する統合データ線DATIの一端と接続されている。統合データ線DATIの他端は、データ線駆動回路XDVに接続されている。

【0023】

なお、RGB切替スイッチDSR,DSG,DSBのドレイン電極は統合データ線DATIに接続され、ソース電極は対応するデータ線DATに接続されている。なお、薄膜トランジスタのソース電極とドレイン電極とは、その薄膜トランジスタを流れる電流の向きとトランジスタがnチャネル型かpチャネル型かとによって定まるものであり、薄膜トランジスタそのものに極性があるわけではない。よってソース電極の接続先とドレイン電極の接続先とが反対になっていてもよい。

【0024】

図3は各画素回路PCの構成の一例を示す回路図である。各画素回路PCは、発光素子ILと、発光素子ILに流れる電流を制御する駆動トランジスタDTRと、発光素子ILの発光タイミングを制御する点灯制御スイッチITRと、駆動トランジスタDTRが流す電流量を制御する記憶容量MCPと、記憶容量MCPに貯まった電荷をリセットするリセットスイッチRTRと、検査スイッチMTRと、データ信号を入力する対象となる画素回路を選択する選択スイッチSTRと、を含む。駆動トランジスタDTRはpチャネル型の薄膜トランジスタであり、点灯制御スイッチITR、リセットスイッチRTR、検査スイッチMTR、および選択スイッチSTRはnチャネル型の薄膜トランジスタである。発光素子ILは電流に応じて輝度が変化する自発光素子の一種である有機EL素子である。有機EL素子は一般的にダイオードの性質を示すため、OLED(Organic light-emitting diode)とも呼ばれる。

【0025】

発光素子ILのアノードは点灯制御スイッチITRを介して駆動トランジスタDTRのドレイン電極に接続され、カソードは基準電位を供給する配線に接続される。駆動トランジスタDTRのドレイン電極とゲート電極の間に、リセットスイッチRTRが設けられる。記憶容量MCPの一端が選択スイッチSTRを介して駆動トランジスタDTRのゲート電極と接続され、他端がこの画素回路PCに対応するデータ線DATと接続される。また、検査スイッチMTRの一端は発光素子ILのアノードに接続されている。

【0026】

リセットスイッチRTRのゲート電極はその画素回路PCを含む画素行Prowに対応するリセットスイッチ制御線RESに接続される。また、点灯制御スイッチITRのゲート電極はその画素行Prowに対応する点灯スイッチ制御線ILMに接続され、検査スイッチMTRのゲート電極はその画素行Prowに対応する検査スイッチ制御線MSTに接続され、選択スイッチSTRのゲート電極はその画素行Prowに対応する選択スイッチ制御線SELに接続される。これからわかるように、スイッチ制御線は複数の薄膜トランジスタのゲート電極に接続されている。

【0027】

図4は、垂直走査回路YDVの構成の一例を示す回路図である。垂直走査回路YDVは、スイッチ制御線に対応して設けられる複数の第1のバッファアンプBF1と、画素行Prowに対応して設けられる複数のスイッチ制御信号制御回路SCRと、第1から第4の低電源電位供給線VSS1〜VSS4と、第1から第3の高電源電位供給線VDD1〜VDD3と、タイミング制御線GA,GB,GC,GDと、同時選択制御線GSと、クロック線CKB1,CK1,CKB2,CK2と、垂直スタート信号線VSと、を含む。

【0028】

第1の低電源電位供給線VSS1と、第1の高電源電位供給線VDD1と、第2の低電源電位供給線VSS2と、第2の高電源電位供給線VDD2と、タイミング制御線GA,GB,GC,GDと、同時選択制御線GSと、第3の低電源電位供給線VSS3と、第3の高電源電位供給線VDD3と、クロック線CKB1,CK1,CKB2,CK2と、垂直スタート信号線VSと、第4の低電源電位供給線VSS4とは、それぞれ垂直方向に延びており、順に垂直方向に直交する方向(水平方向)に並んで配置されている。第1から第4の低電源電位供給線VSS1〜VSS4は低い方の電源電位(第1電源電位)を供給する。第1から第3の高電源電位供給線VDD1〜VDD3は高い方の電源電位(第2電源電位)を供給する。

【0029】

1つの画素行Prowに4本のスイッチ制御線があることに対応し、第1のバッファアンプBF1の数は(N×4)である。スイッチ制御信号制御回路SCRの数はNである。以下では画素行Prow(n)に対応するスイッチ制御信号制御回路SCRをSCR(n)と記す。ここで、ある画素行Prowに対応するスイッチ制御線と、第1のバッファアンプBF1と、スイッチ制御信号制御回路SCRとは、その画素行Prowに属する画素回路PCを制御する機能を有することから、これらをまとめて画素行制御回路と呼ぶ。垂直走査回路YDVには、N個の画素行制御回路が垂直方向に並んで配置されている。また第1のバッファアンプBF1はスイッチ制御線に、そのスイッチ制御線に接続されるスイッチを制御する信号(スイッチ制御信号)を供給することから、以下ではスイッチ制御信号供給回路とも呼ぶ。

【0030】

スイッチ制御信号制御回路SCRは、画素行制御回路内のスイッチ制御線のそれぞれに対応するスイッチ制御信号供給回路を制御する供給制御信号を供給する。各スイッチ制御信号制御回路SCRは第2のバッファアンプBF2、第1のNOT回路NT1、第1のNAND回路NA1、第2のNOT回路NT2、NOR回路NR1、第3のNOT回路NT3、第2のNAND回路NA2、およびフリップフロップ回路FFを有する。第2のバッファアンプBF2、第1のNOT回路NT1、第1のNAND回路NA1はスイッチ制御線のそれぞれに対応して設けられており、その数はスイッチ制御信号制御回路SCRごとにそれぞれ4つである。第2のNOT回路NT2、NOR回路NR1、第3のNOT回路NT3、第2のNAND回路NA2、およびフリップフロップ回路FFはスイッチ制御信号制御回路SCRごとに1つずつ含まれている。

【0031】

フリップフロップ回路FFのL端子はクロック線CK1またはクロック線CK2と接続され、フリップフロップ回路FFのH端子はクロック線CKB1またはCKB2と接続される。フリップフロップ回路FFのQ端子は次段のスイッチ制御信号制御回路SCRに含まれるフリップフロップ回路FFのD端子に接続される。また、フリップフロップ回路FFのD端子とQ端子とはそれぞれ第2のNAND回路NA2の入力に接続され、その出力は第3のNOT回路NT3に入力される。つまり、フリップフロップ回路FFのD端子とQ端子との論理積が第3のNOT回路NT3から出力される。これにより、第3のNOT回路NT3、第2のNAND回路NA2、およびフリップフロップ回路FFはいわゆるシフトレジスタ回路として動作する。第1のNAND回路NA1、第2のNAND回路NA2、第1のNOR回路NR1にはそれぞれ2つの入力があり、1つの出力がある。

【0032】

NOR回路NR1の入力の一方は、第3のNOT回路NT3の出力と接続され、入力のもう一方は同時選択制御線GSと接続されている。NOR回路NR1の出力は、第2のNOT回路NT2の入力と接続される。これにより、第2のNOT回路NT2およびNOR回路NR1は、シフトレジスタ回路からの出力と同時選択制御線GSとの論理和を出力するOR回路として機能する。これにより同時選択制御線GSからハイレベルの電位が供給される場合には、シフトレジスタ回路の出力にかかわらず各画素行Prowがスイッチ制御信号の供給対象となり、各画素回路PCが一斉に駆動される。なおこの例では1フレーム期間は、データ書込みを行うデータ書込み期間と各画素を構成する発光素子ILを発光させる発光期間と発光素子ILの検査を行う検査期間とに分かれている。この例では同時選択制御線GSは主に発光期間に各画素回路PCに含まれる発光素子ILを一斉に点灯させるために設けられている。

【0033】

第1のNOT回路NT1および第1のNAND回路NA1は、あわせてAND回路として機能する。そのAND回路は、第2のNOT回路NT2およびNOR回路NR1により選択された画素行Prowにおいて、各スイッチ制御線へスイッチ制御信号を供給するタイミングを制御する。具体的には第1のNAND回路NA1のうちリセットスイッチ制御線RESに対応するもの、点灯スイッチ制御線ILMに対応するもの、検査スイッチ制御線MSTに対応するもの、選択スイッチ制御線SELに対応するもの、の入力の一方にはそれぞれタイミング制御線GA、タイミング制御線GB、タイミング制御線GC、タイミング制御線GD、が接続される。また、それらの入力の他方には第2のNOT回路NT2の出力が接続される。タイミング制御線GA,GB,GC,GDのそれぞれには水平期間内でのスイッチ制御信号のオンオフを示す信号が送られる。これにより、スイッチ制御線の種類ごとに適切なタイミングでスイッチ制御信号が送られる。

【0034】

第2のバッファアンプBF2は、第1のNOT回路NT1の出力に接続され、第1のNOT回路NT1および第1のNAND回路NA1からの信号を受取り、その信号を増幅して、供給制御信号として第1のバッファアンプBF1に出力する。

【0035】

第1のバッファアンプBF1は、第2のバッファアンプBF2から送信される供給制御信号に応じて、第1電源電位と第2電源電位とのうち1つに対応する電位を選択的に対応するスイッチ制御線に出力する。第1のバッファアンプBF1から選択的に出力される電位がスイッチ制御信号である。図5は第1のバッファアンプBF1の回路構成を示す回路図である。本実施形態において第1のバッファアンプBF1は、CMOSインバータ回路と等価である。第1のバッファアンプBF1は、nチャネル型のトランジスタTRNと、pチャネル型のトランジスタTRPとを含む。トランジスタTRNのドレイン電極は対応するスイッチ制御線に接続され、そのソース電極は第1の低電源電位供給線VSS1に接続される。トランジスタTRPのドレイン電極は対応するスイッチ制御線に接続され、そのソース電極は第1の高電源電位供給線VDD1に接続される。トランジスタTRN,TRPのゲート電極は第1のバッファアンプBF1の入力として第2のバッファアンプBF2の出力と接続される。第1の低電源電位供給線VSS1のうち1つの画素行に対応する部分の抵抗がRVSSUであり、第1の高電源電位供給線VDD1のうち1つの画素行に対応する部分の抵抗をRVDDUである。この抵抗は後述の計算で使用する。なお、トランジスタTRN,TRPのチャネル幅Wは150μmであり、チャネル長Lは4μmである。

【0036】

第1のバッファアンプBF1は、入力される信号に応じて第1の低電源電位供給線VSS1もしくは第1の高電源電位供給線VDD1からの電流をスイッチ制御線に流す。なお第1のバッファアンプBF1が第1電源電位に対応する電位(第1スイッチ電位)をスイッチ制御線に供給する場合に、その電位は第1電源電位からその第1のバッファアンプBF1に含まれるトランジスタTRN等により生じる電圧降下分を除いた電位となる。また第1のバッファアンプBF1が第2電源電位に対応する電位(第2スイッチ電位)をスイッチ制御線に供給する場合に、その電位は第2電源電位からその第1のバッファアンプBF1に含まれるトランジスタTRP等により生じる電圧降下分を除いた電位となる。第1スイッチ電位と第2スイッチ電位とのうち一方が薄膜トランジスタをオンする電位、他方がオフする電位となる。本実施形態の例ではスイッチ制御線に接続された薄膜トランジスタがnチャネル型であるため、その薄膜トランジスタは第1スイッチ電位でオフになり、第2スイッチ電位でオンになる。もし薄膜トランジスタがpチャネル型となる場合はスイッチ電位とオンおよびオフとの関係が反対になる。

【0037】

第2のバッファアンプBF2の回路構成も、電源や入出力の接続先が異なる点を除けば、他の回路構成は同様である。ただし電源供給能力やインピーダンスを考慮し、トランジスタのチャネル幅は第1のNOT回路NT1より大きく、第1のバッファアンプBF1より小さくなっている。

【0038】

第2のバッファアンプBF2には、第1の高電源電位供給線VDD1と第2の低電源電位供給線VSS2とが接続され、それらから電源が供給される。第1のNOT回路NT1、第1のNAND回路NA1、第2のNOT回路NT2、およびNOR回路NR1には第2の高電源電位供給線VDD2および第3の低電源電位供給線VSS3が接続され、それらから電源が供給される。シフトレジスタ回路には第3の高電源電位供給線VDD3と第4の低電源電位供給線VSS4とが接続され、それらから電源が供給される。

【0039】

これまでに説明した有機EL表示装置の動作について従来のものと比較しながら説明する。この有機EL表示装置の例では、1フレーム期間がデータ書込み期間と発光期間と検査期間とに分かれており、データ書込み期間には画素行Prowごとにその画素行Prowを構成する各画素回路PCに含まれる記憶容量MCPにデータ信号に応じた電位差が書込まれる。データ信号は各画素回路PCが表示する階調を示す信号である。発光期間には有機EL表示装置は全ての画素行Prowに含まれる画素回路PCを一斉に発光させる。1つの画素行Prowを構成する画素回路PCに含まれる記憶容量MCPにデータ書込みの操作を行う期間を一水平期間(1H)と呼ぶ。また、RGB切替スイッチDSR,DSG,DSBを用い、赤のデータ線DATRと緑のデータ線DATGと青のデータ線DATBとに順にデータ信号が供給される。

【0040】

図6は、ある画素行Prowにおいて一水平期間に画素回路PC、RGB切替制御線CLA,CLB,CLCおよびデータ線DATに向けて供給される理想的な信号の電位と、スイッチ制御線やデータ線DATの実際の電位とを示す波形図である。図6は上から順にRGB切替制御線CLAの電位、RGB切替制御線CLBの電位、RGB切替制御線CLCの電位、垂直走査回路YDVが点灯スイッチ制御線ILMに供給する理想的な電位ViI、垂直走査回路YDVがリセットスイッチ制御線RESに供給する理想的な電位ViR、垂直走査回路YDVが検査スイッチ制御線MSTに供給する理想的な電位ViM、垂直走査回路YDVが選択スイッチ制御線SELに供給する理想的な電位ViS、データ線駆動回路XDVからk列目の青のデータ線DATB(k)に供給する理想的な電位ViDB(k)、そして、点灯スイッチ制御線ILMの実際の電位、リセットスイッチ制御線RESの実際の電位、検査スイッチ制御線MSTの実際の電位、選択スイッチ制御線SELの実際の電位、k列目の青のデータ線DATB(k)の実際の電位、k列目と異なるx列目の青のデータ線DATB(x)の実際の電位を示す。

【0041】

一水平期間の間ずっと、データ信号の書込み対象となる画素行に対応する選択スイッチ制御線SELにハイレベルの電位が供給され、選択スイッチSTRはその間オンとなる。選択スイッチ制御線SELの電位がハイレベルとなった後に、RGB切替制御線CLAにハイレベルの電位が供給され、データ線駆動回路XDVから統合データ線DATIを介して赤のデータ線DATRにデータ信号が供給され、その電位はデータ線DATRの寄生容量に充電されると同時に、赤の画素回路PCに含まれるすべての記憶容量MCPの一端にデータ信号の電位が印加される。次にRGB切替制御線CLBにハイレベルの電位が供給されて緑のデータ線DATGにデータ信号が供給され、緑の画素回路PCに含まれるすべての記憶容量MCPの一端にデータ信号の電位が印加される。次にRGB切替制御線CLCにハイレベルの電位が供給されて青のデータ線DATBにデータ信号が供給され、青の画素回路PCに含まれるすべての記憶容量MCPの一端にデータ信号の電位が印加される。各データ線に書き込まれた電位は各データ線の寄生容量により保持され、各RGB切替制御線がオフレベルとなった後もデータ電位を保持する。このようにデータ信号がデータ線DATR,DATG,DATBに順に供給されるタイミング(データ信号印加タイミング)には、データ信号の変化に伴いスイッチ制御線の電位が変化する。これについては後述する。

【0042】

その後点灯スイッチ制御線ILMとリセットスイッチ制御線RESの電位がハイレベルになり、点灯制御スイッチITRとリセットスイッチRTRがオンとなる。すると記憶容量MCPに充電されていた電荷がリセットされる。その後すぐに点灯スイッチ制御線ILMがローレベルになり点灯制御スイッチITRがオフになり、ゲート−ソース間の電位差が閾値電圧に相当するまで駆動トランジスタDTRに電流が流れる。この操作により駆動トランジスタの閾値電圧のばらつきをリセットすることができる。

【0043】

その後リセットスイッチ制御線RESの電位がハイレベルからローレベルに変わると、記憶容量MCPの駆動トランジスタDTRのゲート側の電荷が閉じ込められ、各記憶容量の両端に生じた電位差が次の発光期間まで記憶される。なお、書込み期間では検査スイッチ制御線MSTの電位はローレベルである。

【0044】

ここで、表示領域DA内では各データ線DATは複数のスイッチ制御線と交差しており、その交差している箇所では寄生容量が生じている。それにより、データ信号印加タイミングにはあるデータ線DATの電位の変化によりスイッチ制御線の電位が変動し、そのスイッチ制御線の電位の変動により、他のデータ線DATの電位も変動する現象が生じる。図6ではデータ信号印加タイミングのうちRGB切替スイッチDSBがオンとなるタイミングには、DATB(k)に白を表示するための高い電位が供給される。すると寄生容量によりリセットスイッチ制御線RES、点灯スイッチ制御線ILMおよび検査スイッチ制御線MSTの電位も一時的に高くなり、その後、各スイッチ制御線から電荷の供給を受けて一定の時間をかけて本来の電位に戻っていく。この電位の戻りが遅いと、データ線DATB(k)にデータ信号の供給が停止する時点で本来の電位との差Vdlが生じる。この時点ではデータ線DATBには外部から電位が供給されないため、スイッチ制御線の電位が本来の電位に戻る際にデータ線DATBの電位は寄生容量による影響を受けて電位差Vdkだけ低下してしまう。その後リセットスイッチ制御線RESの電位をローレベルにし、リセットスイッチRTRをオフにする際に理想的な電位に対して電位差Vdkの分だけ記憶容量MCPに記憶される電位がずれ、表示される輝度がその分変化する。また、他のデータ線DATB(x)についても同様の理由で理想的な電位に対して電位差Vdnの分だけ記憶容量MCPに記憶される電位がずれ、表示される輝度がその分変化する。電位差Vdnの大きさは電位差Vdkと概ね等しくなる。

【0045】

ここで、図4に示す第1から第4の低電源電位供給線VSS1〜VSS4、第1から第3の高電源電位供給線VDD1〜VDD3の幅について説明する。第1の低電源電位供給線VSS1の太さは48μm、第1の高電源電位供給線VDD1の太さは52μm、第2から第4の低電源電位供給線VSS2〜VSS4の太さは20μm、第2および第3の高電源電位供給線VDD2,VDD3の太さは20μmである。第1のバッファアンプBF1(スイッチ制御信号供給回路)への電源供給に着目すると、第1の低電源電位供給線VSS1からスイッチ制御信号供給回路に第1の電源電位が供給されている。第1の低電源電位供給線VSS1を以下ではスイッチ制御信号回路に第1の電位を供給する第1の電源線と呼ぶ。次に、第1の高電源電位供給線VDD1からスイッチ制御信号供給回路に第2の電源電位が供給されている。ここで第1の高電源電位供給線VDD1は第2のバッファアンプBF2にも電源を供給している。第1の高電源電位供給線VDD1は、スイッチ制御信号回路に第2の電源電位を供給する線(第2の電源線)と、第2のバッファアンプBF2に電源を供給する電源線とが統合されて設けられたものである。第1の高電源電位供給線VDD1のうち後者の電源線に相当する部分の太さは、第2の低電源電位供給線VSS2の太さと同じと考えられる。第2のバッファアンプBF2の回路構成も他の回路構成(例えば、図5に記載の回路構成)と同様であり、第2のバッファアンプBF2の構成から第1電源電位、第2電源電位ともに流れる電流の量は同じ程度と考えられるためである。よって、第1の高電源電位供給線VDD1のうち第2の電源線に相当する部分の太さは、52−20=32μmとなる。また、図1に示す低電源電位入力線VSSW(第3の電源線)および高電源電位入力線VDDW(第4の電源線)の太さは150μmである。これらからわかるように、第1の電源線は第2の電源線より太く、また、第1の電源線は第2の電源線の1.5倍の太さである。

【0046】

ここで、図6に示すVdnにより記憶容量MCPに記憶される電位差が変化するため、それが大きくなれば表示階調の変化が生じ、表示品質が劣化する。図7は、第1の電源線と第2の電源線の太さを同じにした有機EL表示装置で起きる画質劣化の例を示す図である。表示領域DAには、矩形の白領域BAとその周辺のグレー領域WAとを表示するようにデータ線信号が供給されている。データ線DATB(k)は表示領域DAにおいて白領域BAを貫くように上下方向に延びており、データ線DATB(x)は、表示領域DAにおいて白領域BAを貫かないように上下に延びている。従来の有機EL表示装置では、白領域BAの上端部分から左右方向に周辺より輝度の低い横スメア線SL1が、白領域BAの下端部分から左右方向に周辺より輝度の高い横スメア線SL2が表示される。

【0047】

以下では、この第1の電源線および第2の電源線の幅と表示品質の関係について、モデル化した構成を元に計算して説明する。なお以下では、本実施形態にかかる有機EL表示装置の画素の解像度は640列×480行として計算している。

【0048】

図8は、ある画素に発生する寄生容量と抵抗とを説明する図である。データ線DATとスイッチ制御線との間には、1画素回路PCあたり寄生容量Cpxyが発生している。さらに各スイッチ制御線には1画素PXあたりRpxの大きさの抵抗がある。また、図示しないがスイッチ制御線にはデータ線DAT以外の配線等との間に寄生容量Cpxoが、データ線DATにはスイッチ制御線以外の配線との間にも寄生容量Cpyoが発生する。本実施形態の例では寄生容量Cpxyが1画素回路あたり1fF、寄生容量Cpxoが1画素回路あたり17fF、寄生容量Cpyoは1画素回路あたり14fFである。各スイッチ制御線に発生する1画素回路あたりの寄生容量Cpxは寄生容量Cpxyに寄生容量Cpxoを足した18fFである。各データ線DATに発生する1画素回路あたりの寄生容量Cpyは寄生容量Cpxyに寄生容量Cpyoを足した15fFとなる。

【0049】

図9は、データ信号印加タイミングにおけるスイッチ制御線に印加される電位を示す図である。本図の表にはデータ信号印加タイミングにおける、選択された画素行の各スイッチ制御線の電位Lselと、選択されていない画素行の各スイッチ制御線の電位Lnslとが示されている。本図に示すように、選択された画素行でハイレベルの電位が供給されるのは選択スイッチ制御線SELのみであり、他のスイッチ制御線にはローレベルの電位が供給される。選択されていない画素行ではどのスイッチ制御線にもローレベルの電位が供給される。

【0050】

よって、データ信号印加タイミングにおいてハイレベルの電位が供給されるスイッチ制御線の数は1本、一方ローレベルの電位が供給されるスイッチ制御線の数Lは、選択されている画素行で該当するスイッチ制御線の数に、選択されていない画素行のスイッチ制御線の本数を足した1919(3+479×4)本である。

【0051】

図10は、第1の電源線および第2の電源線に関する寄生容量と抵抗を示す図である。データ信号印加タイミングでは、ローレベルの電位が供給される各スイッチ制御線の一端が、第1のバッファアンプBF1に含まれるトランジスタTRNのオン抵抗RONNを介して第1の電源線に接続される。ハイレベルの電位が供給されるスイッチ制御線の一端は、第1のバッファアンプBF1に含まれるトランジスタTRPのオン抵抗RONPを介して第2の電源線に接続される。第1の電源線には、画素行に対応する部分ごとに抵抗RVSSUが生じる。第2の電源線には、画素行に対応する部分ごとに抵抗RVDDUが生じる。第1の電源線に第1の電源電位を供給する低電源電位入力線VSSWには、抵抗RVSSWが生じる。第2の電源線に第2の電源電位を供給する高電源電位入力線VDDWには、抵抗RVDDWが生じる。各スイッチ制御線には、画素回路PCごとに寄生容量Cpxが生じ、画素PXごとに抵抗Rpxが生じる。

【0052】

図11は、図10に示す第1の電源線に関する寄生容量と抵抗の計算用モデルを示す図である。本図では全ての寄生容量が表示領域の中心に発生するとして図10の構成をモデル化している。ここで行数をN、列数をMとすると、第1の電源電位が低電源電位入力線VSSWに入力されてから寄生容量までの抵抗の大きさRtは、以下の示す式で計算される。

【0053】

Rt=RVSSW+RVSSU×(N/2)+RONN/L+Rpx×(M/2)/L

【0054】

ここで、実際のRVSSUおよびRVDDWは3.5Ω、RONNおよびRONPは6kΩ、RVSSUは0.138Ω、Rpxが28.4Ωである。これらを代入して計算すると、抵抗Rtは44.5Ωとなる。次に寄生容量Ctは以下に示す式で計算される。

【0055】

Ct=Cpx×M×L×3

【0056】

ここで、3を掛けているのは、1画素がRGBの3つの画素回路で構成されているからであり、Cpxyを用いずにCpxとしているのは一度変化してしまったスイッチ制御線をもとの電位に戻すことを考慮しているからである。実際の値を代入すると、寄生容量Ctは66.3nFとなる。ここで、図11に示すモデルからわかるように、第1の電源線と、それに接続されるスイッチ制御線はRC回路を構成している。このRC回路の時定数τは、抵抗Rtと寄生容量Ctを掛けた値である2.95μsとなる。

【0057】

次に、画質の劣化を起こさないように許容される時定数τについて検討する。データ線DATに印加される電位に電位変化ΔVdが与えられた時のスイッチ制御線の電位変化ΔVlは、ΔVd×Cpxy/Cpxで計算でき、電位変化ΔVdが5Vであれば、ΔVlは0.27Vとなる。一方、スイッチ制御線の電位変化ΔVlによる他のデータ線の電位変化ΔVrは、ΔVl×Cpxy/Cpyで計算できる。ΔVrの許容できる電位差は、256階調のうちの1階調の半分程度とすると、5V/256/2で約0.01V以下であるから、ΔVlの許容できる電位差は0.01×15で0.15V以下となる。当初の電位変動が0.27Vで許容できる電位差が0.15Vであることから、減衰率は0.15/0.27=0.55となり時定数τの時間が経過した際の減衰率(0.36)よりも大きいことから、時定数τがデータ線DATにデータ信号が供給される期間Tより小さければ画質の劣化は許容できると考えられる。ここで、本実施形態の例ではデータ信号が供給される期間Tは3μsであり、時定数τは期間Tより小さいので、画質の劣化は許容範囲に抑えられている。

【0058】

一方、第1の電源線と第2の電源線の太さが等しく、全体の幅を太くできない場合には、第1の電源線と第2の電源線の和が本実施形態の場合の第1の電源線と第2の電源線の和と同じになるため、第1の電源線および第2の電源線の幅は40μmとなる。これを代入して計算すると、抵抗Rtは51.0Ωとなり、時定数τは3.38μsとなる。これは期間Tより大きくなるため、許容範囲を外れているといえる。

【0059】

こうすることにより、データ信号印加タイミングにおいて第1の電源線と第2の電源線との間で流れる電流に偏りが生じる場合に、多くの電流が流れる電源線の電源供給能力不足による問題を軽減することができる。また、第1の電源線および第2の電源線のうち太い方の幅が細い方の幅の1.5倍以上もあれば、電位変化が抑制されていることは十分に認識可能である。

【0060】

なお、上述の実施形態では低電源電位入力線VSSWの幅と高電源電位入力線VDDWの幅とが同じとしているが、データ信号印加タイミングに流れる電流量に合わせて異ならせてもよい。より具体的には、第1電源電位および第2電源電位のうち、データ信号印加タイミングでより多くのスイッチ制御信号供給回路が出力する電位に対応する電源電位を供給する外部電源線の幅が、他方の外部電源線の幅より太くなっていてもよい。そうすれば、データ信号印加タイミングにおいて第1の電源線と第2の電源線との間で流れる電流に偏りが生じる場合に、多くの電流が流れる電源線の電源供給能力不足に伴う問題をより軽減することができる。

【0061】

また、上述の例では1フレーム期間がデータ書込み期間と発光期間とで分かれていたが、データ書込み期間と発光期間とが分かれていない有機EL表示装置に本発明を適用してもよい。図12は、各画素回路PCの構成の他の例を示す回路図である。各画素回路PCは、発光素子ILと、発光素子ILに流れる電流を制御する駆動トランジスタDTRと、発光素子ILの発光タイミングを制御する点灯制御スイッチITRと、データ信号供給時に駆動トランジスタDTRとデータ線DATとの間の電位差を記憶する記憶容量C1と、駆動トランジスタDTRが流す電流量を制御する記憶容量C2と、記憶容量C1およびC2に貯まった電荷をリセットするリセットスイッチRTRと、データ信号を入力する対象となる画素回路を選択する選択スイッチSTRと、を含む。駆動トランジスタDTR、点灯制御スイッチITR、リセットスイッチRTR、および選択スイッチSTRはpチャネル型の薄膜トランジスタである。発光素子ILは有機EL素子である。

【0062】

発光素子ILのアノードは点灯制御スイッチITRを介して駆動トランジスタDTRのドレイン電極に接続され、カソードは基準電位を供給する配線に接続される。駆動トランジスタDTRのドレイン電極とゲート電極の間に、リセットスイッチRTRが設けられる。駆動トランジスタDTRのゲート電極とソース電極との間には、記憶容量C2が設けられる。記憶容量C1の一端が選択スイッチSTRを介して駆動トランジスタDTRのゲート電極と接続され、他端がこの画素回路PCに対応するデータ線DATと接続される。

【0063】

画素行Prowのそれぞれに対応して、選択スイッチ制御線SLと、リセットスイッチ制御線AZと、点灯スイッチ制御線AZBとが設けられている。選択スイッチ制御線SLは、対応する画素行Prowの画素回路PCに含まれる選択スイッチSTRのゲート電極に接続される。リセットスイッチ制御線AZは、その画素回路PCに含まれるリセットスイッチRTRのゲート電極に接続される。点灯スイッチ制御線AZBは、その画素回路PCに含まれる点灯制御スイッチITRのゲート電極と接続される。

【0064】

ここで、垂直走査回路YDVは、画素行Prowごとに3本あるスイッチ制御線にスイッチ制御信号を供給する点を除いて図2や図4で説明した例と同じである。また、データ線DATは、図2の例とは異なりRGB切替スイッチDSR,DSG,DSBや、統合データ線DATIを介すことなくデータ線駆動回路XDVに接続されている。

【0065】

本実施形態に係る有機EL表示装置の動作について説明する。1フレーム期間においては、行ごとに画素回路PCにデータ信号が書込まれ、データ信号が書き込まれた画素回路PCは次のフレーム期間にデータ信号が書き込まれるまで発光する。1つの画素行Prowを構成する画素回路PCに含まれる記憶容量C1およびC2にデータ書込みの操作を行う期間を一水平期間(1H)と呼ぶ。

【0066】

この有機EL表示装置の例では、一水平期間のはじめには選択スイッチ制御線SLの電位がハイレベルからローレベルとなり、選択スイッチSTRがオンになる。そして、リセットスイッチ制御線AZの電位がローレベルとなりリセットスイッチRTRがオンされると、駆動トランジスタDTRはダイオード接続され、記憶容量C2に電位差が蓄えられる。次に点灯スイッチ制御線AZBの電位がハイレベルとなり点灯制御スイッチITRがオフになる。その後リセットスイッチ制御線AZの電位がハイレベルとなりリセットスイッチRTRがオフとなり、そのタイミングで映像の階調に応じたデータ信号が供給されると、記憶容量C1および記憶容量C2の直列回路には画素回路駆動電源線PWRからの電源電位とデータ信号の電位との電位差を生じる電荷が蓄えられる。このタイミングがデータ信号印加タイミングである。その後、選択スイッチ制御線SLの電位がハイレベルとなり選択スイッチSTRがオフとされ、さらに点灯スイッチ制御線AZBの電位がローレベルとなり点灯制御スイッチITRがオンとなると、発光素子ILはデータ信号に応じた階調の光を発光する。

【0067】

図13は、図12に示す画素回路を含む有機EL表示装置においてデータ信号印加タイミングにスイッチ制御線に印加される電位を示す図である。本図の表にはデータ信号印加タイミングにおける、選択された画素行の各スイッチ制御線の電位Lselと、選択されずに発光している画素行の各スイッチ制御線の電位Lilmとが示されている。図に示すように、選択された画素行では、選択スイッチ制御線SLにはローレベルの電位が供給され、リセットスイッチ制御線AZと、点灯スイッチ制御線AZBにはハイレベルの電位が供給される。選択されている画素行Prowではハイレベルの電位が供給されるのは選択スイッチ制御線SELのみであり、他のスイッチ制御線にはローレベルの電位が供給される。選択されていない画素行Prowでは、選択スイッチ制御線SLとリセットスイッチ制御線AZとにハイレベルの電位が供給され、点灯スイッチ制御線AZBにはローレベルの電位が供給される。

【0068】

よって、データ信号印加タイミングにおいてハイレベルの電位が供給されるスイッチ制御線の数は選択されている画素行で該当するスイッチ制御線の数に、選択されていない画素行で該当するスイッチ制御線の本数を足した960(2+479×2)本であり、一方ローレベルの電位が供給されるスイッチ制御線の数は、480(1+479×1)本である。

【0069】

この例では第1電源電位を供給する第1の電源線の太さが27μmであり、第2の電源電位を供給する第2の電源線の太さが54μmである。高い方の電源電位を供給する第2の電源線の幅は、低い方の電源電位を供給する第1の電源線の幅の1.5倍以上になっている。第1の電源線の幅と第2の電源線の幅の比は、第1の電源電位に対応する電位が供給されるスイッチ制御線の数と第2の電源電位が供給されるスイッチ制御線の数との比と同じになっている。こうするとはじめに説明した実施形態の例と同じように、データ信号印加タイミングにおいて第1の電源線と第2の電源線との一方に生じる電源供給能力不足を抑制し、それにより起きる問題を軽減することができる。

【符号の説明】

【0070】

DA 表示領域、DIC ドライバ集積回路、FPC フレキシブルプリント基板、SUB アレイ基板、XDV データ線駆動回路、YDV 垂直走査回路、CLA,CLB,CLC RGB切替制御線、DAT,DATR,DATG,DATB データ線、DATI 統合データ線、DSR,DSG,DSB RGB切替スイッチ、ILM,AZB 点灯スイッチ制御線、MST 検査スイッチ制御線、PC,PCR,PCG,PCB 画素回路、Prow 画素行、PWR 画素回路駆動電源線、PX 画素、RES,AZ リセットスイッチ制御線、SEL,SL 選択スイッチ制御線、DTR 駆動トランジスタ、IL 発光素子、ITR 点灯制御スイッチ、MCP,C1,C2,CPP 記憶容量、MTR 検査スイッチ、RTR リセットスイッチ、STR 選択スイッチ、TRN,TRP トランジスタ、BF1,BF2,BFP バッファアンプ、CKB1,CK1,CKB2,CK2 クロック線、FF フリップフロップ回路、GA,GB,GC,GD タイミング制御線、GS 同時選択制御線、NA1 第1のNAND回路、NA2 第2のNAND回路、NR1 NOR回路、NT1 第1のNOT回路、NT2 第2のNOT回路、NT3 第3のNOT回路、SCR スイッチ制御信号制御回路、VDD1 第1の高電源電位供給線、VDD2 第2の高電源電位供給線、VDD3 第3の高電源電位供給線、VS 垂直スタート信号線、VSS1 第1の低電源電位供給線、VSS2 第2の低電源電位供給線、VSS3 第3の低電源電位供給線、VSS4 第4の低電源電位供給線、VDDW 高電源電位入力線、VSSW 低電源電位入力線、BA 白領域、WA グレー領域、SL1,SL2 横スメア線、Cpx,Cpxy 寄生容量、PDV 電源線駆動回路、PH 駆動用電源供給線、PL 駆動用接地線、SCL スイッチ制御線、VDD 高電源電位供給線、VSS 低電源電位供給線。

【技術分野】

【0001】

本発明はアクティブマトリクス方式を用いた画像表示装置、特にその画像表示装置に含まれる垂直走査回路に関する。

【背景技術】

【0002】

近年、液晶表示装置や有機EL表示装置などのアクティブマトリクス方式を用いた表示装置において、垂直走査回路をアレイ基板上に設けたものが開発されている。アレイ基板上には表示領域と垂直走査回路とが設けられ、垂直走査回路は表示領域とアレイ基板の端との間にある額縁領域に形成される。表示領域にはマトリクス状に配置された画素回路と、画素回路の列に対応して並ぶデータ線と、データ線に交差する複数のスイッチ制御線と、画素回路向け電源配線とが設けられている。

【0003】

図14は従来の有機EL表示装置の概要の一例を示す回路図である。図14には、垂直方向に並び、それぞれ画素回路の各行への電源供給を制御する有機EL表示装置が示されている。この有機EL表示装置には、電源線駆動回路PDVと、垂直走査回路YDVと、図中上下方向に延びるデータ線DATと、マトリクス状に配置された画素回路PCと、画素回路PCの行に対応して設けられる複数の画素回路駆動電源線PWRおよび複数のスイッチ制御線SCLと、を備えている。電源線駆動回路PDVは、図中上下方向(垂直方向)に延びる駆動用接地線PLと、垂直方向に延びる駆動用電源供給線PHと、駆動用接地線PLと駆動用電源供給線PHとの間に並んで配置されるバッファアンプBFPと、を含む。バッファアンプBFPには駆動用接地線PLと駆動用電源供給線PHとから電源電位が供給される。バッファアンプBFPの出力は、垂直方向に並ぶ画素回路駆動電源線PWRを経て画素回路PCに入力される。

【0004】

垂直走査回路YDVは、垂直方向に延びる低電源電位供給線VSSと、垂直方向に延びる高電源電位供給線VDDと、低電源電位供給線VSSと高電源電位供給線VDDとの間に並んで配置されるバッファアンプBF1と、を含む。バッファアンプBF1には低電源電位供給線VSSおよび高電源電位供給線VDDから電源が供給される。バッファアンプBF1の出力は、スイッチ制御線SCLを経てスイッチ制御信号として画素回路PCに入力される。各画素回路PCは、画素回路駆動電源線PWRに接続される駆動トランジスタDTRと、駆動トランジスタDTRを介して供給された電流により発光する発光素子ILと、データ線DATに基づく電位と画素回路駆動電源線PWRの電位との電位差によって駆動トランジスタDTRを制御する記憶容量CPPと、スイッチ制御線SCLにゲート電極が接続され、スイッチ制御信号により画素回路PCを選択する選択スイッチSTRと、を含む。選択スイッチSTRは薄膜トランジスタである。

【0005】

この有機EL表示装置では、走査された行の画素回路に対して電源を供給する画素回路駆動電源線PWRに対してのみ駆動用接地線PLからの電位が供給される。他の画素回路駆動電源線PWRには駆動用電源供給線PHからの電位が供給される。駆動用電源供給線PHから電位が供給されると、発光素子ILに向かって駆動用電源供給線PHに電流が流れる。結局、駆動用電源供給線PHには駆動用接地線PLより多くの電流が流れるため、それに応じて駆動用電源供給線PHは駆動用接地線PLより太くなっている。このような駆動用電源供給線PHが駆動用接地線PLより太い構成は、特許文献1に開示されている。

【0006】

一方、垂直走査回路YDVでは、スイッチ制御線SCLは選択スイッチSTRのゲート電極に接続されるため、電位が供給されてもスイッチ制御線SCLには定常的な電流はほとんど流れない。スイッチ制御線SCLに流れる電流は、主に電位が切り替わる際に寄生容量との間で充放電を行う際に生じるものと考えられている。表示装置では一定期間にスイッチ制御線SCLに供給する電位を高電位から低電位に切替する回数と低電位から高電位に切替する回数とは等しい。よって低電源電位供給線VSSと高電源電位供給線VDDとに流れる電流は同程度であり、それらの太さは同じとしていた。

【先行技術文献】

【特許文献】

【0007】

【特許文献1】特開2009−14796号公報

【発明の概要】

【発明が解決しようとする課題】

【0008】

近年、例えば表示装置を構成するアレイ基板の額縁領域を狭くするために、垂直走査回路内で電源電位を供給する線の幅が狭くなってきている。すると低電源電位供給線VSSと高電源電位供給線VDDとのうち一方の電源供給能力が不足し、例えば横スメアの発生のような表示品質の劣化が生じることがあった。

【0009】

本発明は上記課題を鑑みてなされたものであって、その目的は、スイッチ制御線に電位を供給する回路に互いに異なる電源電位を供給する2つの電源線のうち一方に生じる電源供給能力不足を抑制する画像表示装置を提供することにある。

【課題を解決するための手段】

【0010】

本出願において開示される発明のうち、代表的なものの概要を簡単に説明すれば、以下の通りである。

【0011】

(1)表示領域内に並んで設けられる複数のデータ線と、前記表示領域内に並んで設けられるとともにそれぞれ前記各データ線と交差する複数のスイッチ制御線と、2本の電源線および複数のスイッチ制御信号供給回路を含む垂直走査回路と、を含み、前記2本の電源線のうち一方は第1電源電位を供給し、前記2本の電源線のうち他方は第2電源電位を供給し、前記各スイッチ制御信号供給回路は、それぞれ前記複数のスイッチ制御線のうちの1つに対応して設けられ、データ信号が前記複数のデータ線に供給されるタイミングにおいて、前記第1電源電位に対応する電位、および、前記第2電源電位に対応する電位のいずれか一方を選択的に対応するスイッチ制御線に対して出力し、前記第1電源電位および前記第2電源電位のうち、前記タイミングでより多くの前記スイッチ制御信号供給回路が出力する電位に対応する電源電位を供給する電源線の幅が、他方の電源電位を供給する電源線の幅より太い、ことを特徴とする画像表示装置。

【0012】

(2)(1)において、前記第1電源電位および前記第2電源電位のうち、前記タイミングでより多くの前記スイッチ制御信号供給回路が出力する電位に対応する電源電位を供給する電源線の幅が、他方の電源電位を供給する電源線の幅の1.5倍以上である、ことを特徴とする画像表示装置。

【0013】

(3)(1)または(2)において、前記垂直走査回路の外に設けられ、前記第1電源電位を前記2つの電源線の一方に供給する外部電源線と、前記垂直走査回路の外に設けられ、前記第2電源電位を前記2つの電源線の他方に供給する外部電源線と、をさらに含み、前記第1電源電位および前記第2電源電位のうち、前記タイミングでより多くの前記スイッチ制御信号供給回路が出力する電位に対応する電源電位を供給する外部電源線の幅は、他方の電源電位を供給する外部電源線の幅より太い、ことを特徴とする画像表示装置。

【発明の効果】

【0014】

本発明によれば、スイッチ制御線に電位を供給する回路に互いに異なる電源電位を供給する2つの電源線のうち一方に生じる電源供給能力不足を抑制しつつ額縁領域に占める電源線領域を効率よく小さくすることができる。

【図面の簡単な説明】

【0015】

【図1】本発明の実施形態に係る有機EL表示装置の部品配置の一例を示す図である。

【図2】本発明の実施形態に係る有機EL表示装置の回路構成の一例を示す回路図である。

【図3】各画素回路の構成の一例を示す回路図である。

【図4】垂直走査回路の構成の一例を示す回路図である。

【図5】バッファアンプの回路構成を示す回路図である。

【図6】ある画素行において一水平期間に画素回路やRGB切替制御線に向けて供給される理想的な信号の電位と、スイッチ制御線やデータ線の電位とを示す波形図である。

【図7】第1の電源線と第2の電源線の太さを同じにした有機EL表示装置で起きる画質劣化の例を示す図である。

【図8】ある画素に発生する寄生容量と抵抗とを説明する図である。

【図9】データ信号印加タイミングにおけるスイッチ制御線に印加される電位を示す図である。

【図10】第1の電源線および第2の電源線に関する寄生容量と抵抗を示す図である。

【図11】図10に示す第1の電源線に関する寄生容量と抵抗の計算用モデルを示す図である。

【図12】各画素回路の他の構成を示す回路図である。

【図13】図12に示す画素回路を含む有機EL表示装置においてデータ信号印加タイミングにスイッチ制御線に印加される電位を示す図である。

【図14】従来の有機EL表示装置の概要の一例を示す回路図である。

【発明を実施するための形態】

【0016】

以下では、本発明の実施形態について図面に基づいて説明する。出現する構成要素のうち同一機能を有するものには同じ符号を付し、その説明を省略する。なお以下では、アクティブマトリクス方式を用いた画像表示装置の一種である有機EL表示装置に本発明を適用した場合について説明する。

【0017】

図1は、本発明の実施形態に係る有機EL表示装置の部品配置の一例を示す図である。有機EL表示装置は、物理的には、アレイ基板SUBと、フレキシブルプリント基板FPCと、ドライバ集積回路DICとを含む。アレイ基板SUB上には、画像を表示する表示領域DAが配置される。ここでアレイ基板SUB上の領域で、表示領域DA以外の領域を額縁領域という。垂直走査回路YDVは額縁領域のうち表示領域DAの右側に配置される。垂直走査回路YDVとドライバ集積回路DICとの間には、図示しない制御信号線が設けられている。フレキシブルプリント基板FPCからアレイ基板SUBに、高い方の電源電位と低い方の電源電位とが供給されている。高い方の電源電位は高電源電位入力線VDDWを介して、低い方の電源電位は低電源電位入力線VSSWを介して、垂直走査回路YDVに供給される。なお、低電源電位入力線VSSWおよび高電源電位入力線VDDWはアレイ基板SUBの外部からFPCと接触する端子を介して供給される電源を垂直走査回路YDVに供給する。これらをまとめて外部電源線と呼ぶ。

【0018】

図2は、本発明の第1の実施形態に係る有機EL表示装置の回路構成の一例を示す回路図である。有機EL表示装置は、回路構成として、表示領域DA内にマトリクス状に配置された画素回路PCと、画素回路PCの列に対応して設けられたデータ線DATと、画素回路PCの行(以下画素行Prowと記す)に対応して設けられたリセットスイッチ制御線RES、点灯スイッチ制御線ILM、検査スイッチ制御線MST、および選択スイッチ制御線SELと、画素回路駆動電源線PWRと、データ線DATに対応して設けられたRGB切替スイッチDSR,DSG,DSBと、統合データ線DATIと、データ線駆動回路XDVと、垂直走査回路YDVと、を含む。

【0019】

1つの画素回路PCは、赤、緑、青のうちいずれかの色を表示する。赤を表示する画素回路PC、緑を表示する画素回路PC、および青を表示する画素回路PCが1つずつ組合せられて1つの画素PXとなる。表示領域にはM列×N行の画素が配置されている。なお、m列目n行目の画素を表示する赤の画素回路PCをPCR(m,n)、緑の画素回路PCをPCG(m,n)、青の画素回路PCをPCB(m,n)と記す。また表示領域DA内には(3×M)列×N行の画素回路PCが並んでおり、同じ列に並んでいる画素回路PCは同じ色を表示する。

【0020】

画素回路PCの列に対応して、複数のデータ線DATが表示領域DA内をその列内を画素回路PCが並ぶ方向(垂直方向)に延びている。データ線DATは対応する画素回路PCに接続されている。同じデータ線DATに接続される画素回路PCは同じ色を表示する。以下では、m列の画素の列を構成する赤の画素回路PCの列に対応するデータ線DATをDATR(m)と、緑の画素回路PCの列に対応するデータ線DATをDATG(m)と、青の画素回路PCの列に対応するデータ線DATをDATB(m)と記す。また、表示領域DA内において垂直方向に並ぶN行の画素行Prowのそれぞれに対応して、N本のリセットスイッチ制御線RESと、N本の点灯スイッチ制御線ILMと、N本の検査スイッチ制御線MSTと、N本の選択スイッチ制御線SELとが画素回路PCの列が並ぶ方向に延びている。それぞれの画素行Prowは画素の行に対応する画素回路PCから構成される。ここで、n行目の画素行ProwをProw(n)と記し、Prow(n)に対応するリセットスイッチ制御線をRES(n)、点灯スイッチ制御線をILM(n)、検査スイッチ制御線MSTをMST(n)、選択スイッチ制御線SELをSEL(n)と記す。また、リセットスイッチ制御線RESと、点灯スイッチ制御線ILMと、検査スイッチ制御線MSTと、選択スイッチ制御線SELとは画素回路PC内のスイッチを制御する点で同じ機能を有しているため、以下では総称してスイッチ制御線と記す。表示領域DA内には(N×4)本のスイッチ制御線が並んでおり、スイッチ制御線はそれぞれ、各データ線DATと平面的に交差している。スイッチ制御線は垂直走査回路YDVに接続され、対応する画素行Prowに含まれる画素回路PCにスイッチを制御する信号(スイッチ制御信号)を供給する。また表示領域DA内には、各画素回路PCに電源を供給する画素回路駆動電源線PWRが設けられている。

【0021】

RGB切替スイッチDSR,DSG,DSBは薄膜トランジスタであって、画素の列に対応してそれぞれm個設けられている。RGB切替スイッチDSRのゲート電極にはRGB切替制御線CLAが接続され、RGB切替スイッチDSRのゲート電極にはRGB切替制御線CLBが接続され、RGB切替スイッチDSRのゲート電極にはRGB切替制御線CLCが接続される。

【0022】

画素のm列目に対応するデータ線DATのうち赤の画素回路PCに対応するデータ線DATR(m)の下端には、RGB切替スイッチDSRの一端が接続されている。RGB切替スイッチDSRの他端は、画素列に対応してM本設けられた統合データ線DATIのうちm列目の画素PXに対応する統合データ線DATIの一端と接続されている。同様に、データ線DATG(m)の下端はRGB切替スイッチDSGを介して対応する統合データ線DATIの一端と接続されており、データ線DATB(m)の下端はRGB切替スイッチDSBを介して対応する統合データ線DATIの一端と接続されている。統合データ線DATIの他端は、データ線駆動回路XDVに接続されている。

【0023】

なお、RGB切替スイッチDSR,DSG,DSBのドレイン電極は統合データ線DATIに接続され、ソース電極は対応するデータ線DATに接続されている。なお、薄膜トランジスタのソース電極とドレイン電極とは、その薄膜トランジスタを流れる電流の向きとトランジスタがnチャネル型かpチャネル型かとによって定まるものであり、薄膜トランジスタそのものに極性があるわけではない。よってソース電極の接続先とドレイン電極の接続先とが反対になっていてもよい。

【0024】

図3は各画素回路PCの構成の一例を示す回路図である。各画素回路PCは、発光素子ILと、発光素子ILに流れる電流を制御する駆動トランジスタDTRと、発光素子ILの発光タイミングを制御する点灯制御スイッチITRと、駆動トランジスタDTRが流す電流量を制御する記憶容量MCPと、記憶容量MCPに貯まった電荷をリセットするリセットスイッチRTRと、検査スイッチMTRと、データ信号を入力する対象となる画素回路を選択する選択スイッチSTRと、を含む。駆動トランジスタDTRはpチャネル型の薄膜トランジスタであり、点灯制御スイッチITR、リセットスイッチRTR、検査スイッチMTR、および選択スイッチSTRはnチャネル型の薄膜トランジスタである。発光素子ILは電流に応じて輝度が変化する自発光素子の一種である有機EL素子である。有機EL素子は一般的にダイオードの性質を示すため、OLED(Organic light-emitting diode)とも呼ばれる。

【0025】

発光素子ILのアノードは点灯制御スイッチITRを介して駆動トランジスタDTRのドレイン電極に接続され、カソードは基準電位を供給する配線に接続される。駆動トランジスタDTRのドレイン電極とゲート電極の間に、リセットスイッチRTRが設けられる。記憶容量MCPの一端が選択スイッチSTRを介して駆動トランジスタDTRのゲート電極と接続され、他端がこの画素回路PCに対応するデータ線DATと接続される。また、検査スイッチMTRの一端は発光素子ILのアノードに接続されている。

【0026】

リセットスイッチRTRのゲート電極はその画素回路PCを含む画素行Prowに対応するリセットスイッチ制御線RESに接続される。また、点灯制御スイッチITRのゲート電極はその画素行Prowに対応する点灯スイッチ制御線ILMに接続され、検査スイッチMTRのゲート電極はその画素行Prowに対応する検査スイッチ制御線MSTに接続され、選択スイッチSTRのゲート電極はその画素行Prowに対応する選択スイッチ制御線SELに接続される。これからわかるように、スイッチ制御線は複数の薄膜トランジスタのゲート電極に接続されている。

【0027】

図4は、垂直走査回路YDVの構成の一例を示す回路図である。垂直走査回路YDVは、スイッチ制御線に対応して設けられる複数の第1のバッファアンプBF1と、画素行Prowに対応して設けられる複数のスイッチ制御信号制御回路SCRと、第1から第4の低電源電位供給線VSS1〜VSS4と、第1から第3の高電源電位供給線VDD1〜VDD3と、タイミング制御線GA,GB,GC,GDと、同時選択制御線GSと、クロック線CKB1,CK1,CKB2,CK2と、垂直スタート信号線VSと、を含む。

【0028】

第1の低電源電位供給線VSS1と、第1の高電源電位供給線VDD1と、第2の低電源電位供給線VSS2と、第2の高電源電位供給線VDD2と、タイミング制御線GA,GB,GC,GDと、同時選択制御線GSと、第3の低電源電位供給線VSS3と、第3の高電源電位供給線VDD3と、クロック線CKB1,CK1,CKB2,CK2と、垂直スタート信号線VSと、第4の低電源電位供給線VSS4とは、それぞれ垂直方向に延びており、順に垂直方向に直交する方向(水平方向)に並んで配置されている。第1から第4の低電源電位供給線VSS1〜VSS4は低い方の電源電位(第1電源電位)を供給する。第1から第3の高電源電位供給線VDD1〜VDD3は高い方の電源電位(第2電源電位)を供給する。

【0029】

1つの画素行Prowに4本のスイッチ制御線があることに対応し、第1のバッファアンプBF1の数は(N×4)である。スイッチ制御信号制御回路SCRの数はNである。以下では画素行Prow(n)に対応するスイッチ制御信号制御回路SCRをSCR(n)と記す。ここで、ある画素行Prowに対応するスイッチ制御線と、第1のバッファアンプBF1と、スイッチ制御信号制御回路SCRとは、その画素行Prowに属する画素回路PCを制御する機能を有することから、これらをまとめて画素行制御回路と呼ぶ。垂直走査回路YDVには、N個の画素行制御回路が垂直方向に並んで配置されている。また第1のバッファアンプBF1はスイッチ制御線に、そのスイッチ制御線に接続されるスイッチを制御する信号(スイッチ制御信号)を供給することから、以下ではスイッチ制御信号供給回路とも呼ぶ。

【0030】

スイッチ制御信号制御回路SCRは、画素行制御回路内のスイッチ制御線のそれぞれに対応するスイッチ制御信号供給回路を制御する供給制御信号を供給する。各スイッチ制御信号制御回路SCRは第2のバッファアンプBF2、第1のNOT回路NT1、第1のNAND回路NA1、第2のNOT回路NT2、NOR回路NR1、第3のNOT回路NT3、第2のNAND回路NA2、およびフリップフロップ回路FFを有する。第2のバッファアンプBF2、第1のNOT回路NT1、第1のNAND回路NA1はスイッチ制御線のそれぞれに対応して設けられており、その数はスイッチ制御信号制御回路SCRごとにそれぞれ4つである。第2のNOT回路NT2、NOR回路NR1、第3のNOT回路NT3、第2のNAND回路NA2、およびフリップフロップ回路FFはスイッチ制御信号制御回路SCRごとに1つずつ含まれている。

【0031】

フリップフロップ回路FFのL端子はクロック線CK1またはクロック線CK2と接続され、フリップフロップ回路FFのH端子はクロック線CKB1またはCKB2と接続される。フリップフロップ回路FFのQ端子は次段のスイッチ制御信号制御回路SCRに含まれるフリップフロップ回路FFのD端子に接続される。また、フリップフロップ回路FFのD端子とQ端子とはそれぞれ第2のNAND回路NA2の入力に接続され、その出力は第3のNOT回路NT3に入力される。つまり、フリップフロップ回路FFのD端子とQ端子との論理積が第3のNOT回路NT3から出力される。これにより、第3のNOT回路NT3、第2のNAND回路NA2、およびフリップフロップ回路FFはいわゆるシフトレジスタ回路として動作する。第1のNAND回路NA1、第2のNAND回路NA2、第1のNOR回路NR1にはそれぞれ2つの入力があり、1つの出力がある。

【0032】

NOR回路NR1の入力の一方は、第3のNOT回路NT3の出力と接続され、入力のもう一方は同時選択制御線GSと接続されている。NOR回路NR1の出力は、第2のNOT回路NT2の入力と接続される。これにより、第2のNOT回路NT2およびNOR回路NR1は、シフトレジスタ回路からの出力と同時選択制御線GSとの論理和を出力するOR回路として機能する。これにより同時選択制御線GSからハイレベルの電位が供給される場合には、シフトレジスタ回路の出力にかかわらず各画素行Prowがスイッチ制御信号の供給対象となり、各画素回路PCが一斉に駆動される。なおこの例では1フレーム期間は、データ書込みを行うデータ書込み期間と各画素を構成する発光素子ILを発光させる発光期間と発光素子ILの検査を行う検査期間とに分かれている。この例では同時選択制御線GSは主に発光期間に各画素回路PCに含まれる発光素子ILを一斉に点灯させるために設けられている。

【0033】

第1のNOT回路NT1および第1のNAND回路NA1は、あわせてAND回路として機能する。そのAND回路は、第2のNOT回路NT2およびNOR回路NR1により選択された画素行Prowにおいて、各スイッチ制御線へスイッチ制御信号を供給するタイミングを制御する。具体的には第1のNAND回路NA1のうちリセットスイッチ制御線RESに対応するもの、点灯スイッチ制御線ILMに対応するもの、検査スイッチ制御線MSTに対応するもの、選択スイッチ制御線SELに対応するもの、の入力の一方にはそれぞれタイミング制御線GA、タイミング制御線GB、タイミング制御線GC、タイミング制御線GD、が接続される。また、それらの入力の他方には第2のNOT回路NT2の出力が接続される。タイミング制御線GA,GB,GC,GDのそれぞれには水平期間内でのスイッチ制御信号のオンオフを示す信号が送られる。これにより、スイッチ制御線の種類ごとに適切なタイミングでスイッチ制御信号が送られる。

【0034】

第2のバッファアンプBF2は、第1のNOT回路NT1の出力に接続され、第1のNOT回路NT1および第1のNAND回路NA1からの信号を受取り、その信号を増幅して、供給制御信号として第1のバッファアンプBF1に出力する。

【0035】

第1のバッファアンプBF1は、第2のバッファアンプBF2から送信される供給制御信号に応じて、第1電源電位と第2電源電位とのうち1つに対応する電位を選択的に対応するスイッチ制御線に出力する。第1のバッファアンプBF1から選択的に出力される電位がスイッチ制御信号である。図5は第1のバッファアンプBF1の回路構成を示す回路図である。本実施形態において第1のバッファアンプBF1は、CMOSインバータ回路と等価である。第1のバッファアンプBF1は、nチャネル型のトランジスタTRNと、pチャネル型のトランジスタTRPとを含む。トランジスタTRNのドレイン電極は対応するスイッチ制御線に接続され、そのソース電極は第1の低電源電位供給線VSS1に接続される。トランジスタTRPのドレイン電極は対応するスイッチ制御線に接続され、そのソース電極は第1の高電源電位供給線VDD1に接続される。トランジスタTRN,TRPのゲート電極は第1のバッファアンプBF1の入力として第2のバッファアンプBF2の出力と接続される。第1の低電源電位供給線VSS1のうち1つの画素行に対応する部分の抵抗がRVSSUであり、第1の高電源電位供給線VDD1のうち1つの画素行に対応する部分の抵抗をRVDDUである。この抵抗は後述の計算で使用する。なお、トランジスタTRN,TRPのチャネル幅Wは150μmであり、チャネル長Lは4μmである。

【0036】

第1のバッファアンプBF1は、入力される信号に応じて第1の低電源電位供給線VSS1もしくは第1の高電源電位供給線VDD1からの電流をスイッチ制御線に流す。なお第1のバッファアンプBF1が第1電源電位に対応する電位(第1スイッチ電位)をスイッチ制御線に供給する場合に、その電位は第1電源電位からその第1のバッファアンプBF1に含まれるトランジスタTRN等により生じる電圧降下分を除いた電位となる。また第1のバッファアンプBF1が第2電源電位に対応する電位(第2スイッチ電位)をスイッチ制御線に供給する場合に、その電位は第2電源電位からその第1のバッファアンプBF1に含まれるトランジスタTRP等により生じる電圧降下分を除いた電位となる。第1スイッチ電位と第2スイッチ電位とのうち一方が薄膜トランジスタをオンする電位、他方がオフする電位となる。本実施形態の例ではスイッチ制御線に接続された薄膜トランジスタがnチャネル型であるため、その薄膜トランジスタは第1スイッチ電位でオフになり、第2スイッチ電位でオンになる。もし薄膜トランジスタがpチャネル型となる場合はスイッチ電位とオンおよびオフとの関係が反対になる。

【0037】

第2のバッファアンプBF2の回路構成も、電源や入出力の接続先が異なる点を除けば、他の回路構成は同様である。ただし電源供給能力やインピーダンスを考慮し、トランジスタのチャネル幅は第1のNOT回路NT1より大きく、第1のバッファアンプBF1より小さくなっている。

【0038】

第2のバッファアンプBF2には、第1の高電源電位供給線VDD1と第2の低電源電位供給線VSS2とが接続され、それらから電源が供給される。第1のNOT回路NT1、第1のNAND回路NA1、第2のNOT回路NT2、およびNOR回路NR1には第2の高電源電位供給線VDD2および第3の低電源電位供給線VSS3が接続され、それらから電源が供給される。シフトレジスタ回路には第3の高電源電位供給線VDD3と第4の低電源電位供給線VSS4とが接続され、それらから電源が供給される。

【0039】

これまでに説明した有機EL表示装置の動作について従来のものと比較しながら説明する。この有機EL表示装置の例では、1フレーム期間がデータ書込み期間と発光期間と検査期間とに分かれており、データ書込み期間には画素行Prowごとにその画素行Prowを構成する各画素回路PCに含まれる記憶容量MCPにデータ信号に応じた電位差が書込まれる。データ信号は各画素回路PCが表示する階調を示す信号である。発光期間には有機EL表示装置は全ての画素行Prowに含まれる画素回路PCを一斉に発光させる。1つの画素行Prowを構成する画素回路PCに含まれる記憶容量MCPにデータ書込みの操作を行う期間を一水平期間(1H)と呼ぶ。また、RGB切替スイッチDSR,DSG,DSBを用い、赤のデータ線DATRと緑のデータ線DATGと青のデータ線DATBとに順にデータ信号が供給される。

【0040】

図6は、ある画素行Prowにおいて一水平期間に画素回路PC、RGB切替制御線CLA,CLB,CLCおよびデータ線DATに向けて供給される理想的な信号の電位と、スイッチ制御線やデータ線DATの実際の電位とを示す波形図である。図6は上から順にRGB切替制御線CLAの電位、RGB切替制御線CLBの電位、RGB切替制御線CLCの電位、垂直走査回路YDVが点灯スイッチ制御線ILMに供給する理想的な電位ViI、垂直走査回路YDVがリセットスイッチ制御線RESに供給する理想的な電位ViR、垂直走査回路YDVが検査スイッチ制御線MSTに供給する理想的な電位ViM、垂直走査回路YDVが選択スイッチ制御線SELに供給する理想的な電位ViS、データ線駆動回路XDVからk列目の青のデータ線DATB(k)に供給する理想的な電位ViDB(k)、そして、点灯スイッチ制御線ILMの実際の電位、リセットスイッチ制御線RESの実際の電位、検査スイッチ制御線MSTの実際の電位、選択スイッチ制御線SELの実際の電位、k列目の青のデータ線DATB(k)の実際の電位、k列目と異なるx列目の青のデータ線DATB(x)の実際の電位を示す。

【0041】

一水平期間の間ずっと、データ信号の書込み対象となる画素行に対応する選択スイッチ制御線SELにハイレベルの電位が供給され、選択スイッチSTRはその間オンとなる。選択スイッチ制御線SELの電位がハイレベルとなった後に、RGB切替制御線CLAにハイレベルの電位が供給され、データ線駆動回路XDVから統合データ線DATIを介して赤のデータ線DATRにデータ信号が供給され、その電位はデータ線DATRの寄生容量に充電されると同時に、赤の画素回路PCに含まれるすべての記憶容量MCPの一端にデータ信号の電位が印加される。次にRGB切替制御線CLBにハイレベルの電位が供給されて緑のデータ線DATGにデータ信号が供給され、緑の画素回路PCに含まれるすべての記憶容量MCPの一端にデータ信号の電位が印加される。次にRGB切替制御線CLCにハイレベルの電位が供給されて青のデータ線DATBにデータ信号が供給され、青の画素回路PCに含まれるすべての記憶容量MCPの一端にデータ信号の電位が印加される。各データ線に書き込まれた電位は各データ線の寄生容量により保持され、各RGB切替制御線がオフレベルとなった後もデータ電位を保持する。このようにデータ信号がデータ線DATR,DATG,DATBに順に供給されるタイミング(データ信号印加タイミング)には、データ信号の変化に伴いスイッチ制御線の電位が変化する。これについては後述する。

【0042】

その後点灯スイッチ制御線ILMとリセットスイッチ制御線RESの電位がハイレベルになり、点灯制御スイッチITRとリセットスイッチRTRがオンとなる。すると記憶容量MCPに充電されていた電荷がリセットされる。その後すぐに点灯スイッチ制御線ILMがローレベルになり点灯制御スイッチITRがオフになり、ゲート−ソース間の電位差が閾値電圧に相当するまで駆動トランジスタDTRに電流が流れる。この操作により駆動トランジスタの閾値電圧のばらつきをリセットすることができる。

【0043】

その後リセットスイッチ制御線RESの電位がハイレベルからローレベルに変わると、記憶容量MCPの駆動トランジスタDTRのゲート側の電荷が閉じ込められ、各記憶容量の両端に生じた電位差が次の発光期間まで記憶される。なお、書込み期間では検査スイッチ制御線MSTの電位はローレベルである。

【0044】

ここで、表示領域DA内では各データ線DATは複数のスイッチ制御線と交差しており、その交差している箇所では寄生容量が生じている。それにより、データ信号印加タイミングにはあるデータ線DATの電位の変化によりスイッチ制御線の電位が変動し、そのスイッチ制御線の電位の変動により、他のデータ線DATの電位も変動する現象が生じる。図6ではデータ信号印加タイミングのうちRGB切替スイッチDSBがオンとなるタイミングには、DATB(k)に白を表示するための高い電位が供給される。すると寄生容量によりリセットスイッチ制御線RES、点灯スイッチ制御線ILMおよび検査スイッチ制御線MSTの電位も一時的に高くなり、その後、各スイッチ制御線から電荷の供給を受けて一定の時間をかけて本来の電位に戻っていく。この電位の戻りが遅いと、データ線DATB(k)にデータ信号の供給が停止する時点で本来の電位との差Vdlが生じる。この時点ではデータ線DATBには外部から電位が供給されないため、スイッチ制御線の電位が本来の電位に戻る際にデータ線DATBの電位は寄生容量による影響を受けて電位差Vdkだけ低下してしまう。その後リセットスイッチ制御線RESの電位をローレベルにし、リセットスイッチRTRをオフにする際に理想的な電位に対して電位差Vdkの分だけ記憶容量MCPに記憶される電位がずれ、表示される輝度がその分変化する。また、他のデータ線DATB(x)についても同様の理由で理想的な電位に対して電位差Vdnの分だけ記憶容量MCPに記憶される電位がずれ、表示される輝度がその分変化する。電位差Vdnの大きさは電位差Vdkと概ね等しくなる。

【0045】

ここで、図4に示す第1から第4の低電源電位供給線VSS1〜VSS4、第1から第3の高電源電位供給線VDD1〜VDD3の幅について説明する。第1の低電源電位供給線VSS1の太さは48μm、第1の高電源電位供給線VDD1の太さは52μm、第2から第4の低電源電位供給線VSS2〜VSS4の太さは20μm、第2および第3の高電源電位供給線VDD2,VDD3の太さは20μmである。第1のバッファアンプBF1(スイッチ制御信号供給回路)への電源供給に着目すると、第1の低電源電位供給線VSS1からスイッチ制御信号供給回路に第1の電源電位が供給されている。第1の低電源電位供給線VSS1を以下ではスイッチ制御信号回路に第1の電位を供給する第1の電源線と呼ぶ。次に、第1の高電源電位供給線VDD1からスイッチ制御信号供給回路に第2の電源電位が供給されている。ここで第1の高電源電位供給線VDD1は第2のバッファアンプBF2にも電源を供給している。第1の高電源電位供給線VDD1は、スイッチ制御信号回路に第2の電源電位を供給する線(第2の電源線)と、第2のバッファアンプBF2に電源を供給する電源線とが統合されて設けられたものである。第1の高電源電位供給線VDD1のうち後者の電源線に相当する部分の太さは、第2の低電源電位供給線VSS2の太さと同じと考えられる。第2のバッファアンプBF2の回路構成も他の回路構成(例えば、図5に記載の回路構成)と同様であり、第2のバッファアンプBF2の構成から第1電源電位、第2電源電位ともに流れる電流の量は同じ程度と考えられるためである。よって、第1の高電源電位供給線VDD1のうち第2の電源線に相当する部分の太さは、52−20=32μmとなる。また、図1に示す低電源電位入力線VSSW(第3の電源線)および高電源電位入力線VDDW(第4の電源線)の太さは150μmである。これらからわかるように、第1の電源線は第2の電源線より太く、また、第1の電源線は第2の電源線の1.5倍の太さである。

【0046】

ここで、図6に示すVdnにより記憶容量MCPに記憶される電位差が変化するため、それが大きくなれば表示階調の変化が生じ、表示品質が劣化する。図7は、第1の電源線と第2の電源線の太さを同じにした有機EL表示装置で起きる画質劣化の例を示す図である。表示領域DAには、矩形の白領域BAとその周辺のグレー領域WAとを表示するようにデータ線信号が供給されている。データ線DATB(k)は表示領域DAにおいて白領域BAを貫くように上下方向に延びており、データ線DATB(x)は、表示領域DAにおいて白領域BAを貫かないように上下に延びている。従来の有機EL表示装置では、白領域BAの上端部分から左右方向に周辺より輝度の低い横スメア線SL1が、白領域BAの下端部分から左右方向に周辺より輝度の高い横スメア線SL2が表示される。

【0047】

以下では、この第1の電源線および第2の電源線の幅と表示品質の関係について、モデル化した構成を元に計算して説明する。なお以下では、本実施形態にかかる有機EL表示装置の画素の解像度は640列×480行として計算している。

【0048】

図8は、ある画素に発生する寄生容量と抵抗とを説明する図である。データ線DATとスイッチ制御線との間には、1画素回路PCあたり寄生容量Cpxyが発生している。さらに各スイッチ制御線には1画素PXあたりRpxの大きさの抵抗がある。また、図示しないがスイッチ制御線にはデータ線DAT以外の配線等との間に寄生容量Cpxoが、データ線DATにはスイッチ制御線以外の配線との間にも寄生容量Cpyoが発生する。本実施形態の例では寄生容量Cpxyが1画素回路あたり1fF、寄生容量Cpxoが1画素回路あたり17fF、寄生容量Cpyoは1画素回路あたり14fFである。各スイッチ制御線に発生する1画素回路あたりの寄生容量Cpxは寄生容量Cpxyに寄生容量Cpxoを足した18fFである。各データ線DATに発生する1画素回路あたりの寄生容量Cpyは寄生容量Cpxyに寄生容量Cpyoを足した15fFとなる。

【0049】

図9は、データ信号印加タイミングにおけるスイッチ制御線に印加される電位を示す図である。本図の表にはデータ信号印加タイミングにおける、選択された画素行の各スイッチ制御線の電位Lselと、選択されていない画素行の各スイッチ制御線の電位Lnslとが示されている。本図に示すように、選択された画素行でハイレベルの電位が供給されるのは選択スイッチ制御線SELのみであり、他のスイッチ制御線にはローレベルの電位が供給される。選択されていない画素行ではどのスイッチ制御線にもローレベルの電位が供給される。

【0050】

よって、データ信号印加タイミングにおいてハイレベルの電位が供給されるスイッチ制御線の数は1本、一方ローレベルの電位が供給されるスイッチ制御線の数Lは、選択されている画素行で該当するスイッチ制御線の数に、選択されていない画素行のスイッチ制御線の本数を足した1919(3+479×4)本である。

【0051】

図10は、第1の電源線および第2の電源線に関する寄生容量と抵抗を示す図である。データ信号印加タイミングでは、ローレベルの電位が供給される各スイッチ制御線の一端が、第1のバッファアンプBF1に含まれるトランジスタTRNのオン抵抗RONNを介して第1の電源線に接続される。ハイレベルの電位が供給されるスイッチ制御線の一端は、第1のバッファアンプBF1に含まれるトランジスタTRPのオン抵抗RONPを介して第2の電源線に接続される。第1の電源線には、画素行に対応する部分ごとに抵抗RVSSUが生じる。第2の電源線には、画素行に対応する部分ごとに抵抗RVDDUが生じる。第1の電源線に第1の電源電位を供給する低電源電位入力線VSSWには、抵抗RVSSWが生じる。第2の電源線に第2の電源電位を供給する高電源電位入力線VDDWには、抵抗RVDDWが生じる。各スイッチ制御線には、画素回路PCごとに寄生容量Cpxが生じ、画素PXごとに抵抗Rpxが生じる。

【0052】

図11は、図10に示す第1の電源線に関する寄生容量と抵抗の計算用モデルを示す図である。本図では全ての寄生容量が表示領域の中心に発生するとして図10の構成をモデル化している。ここで行数をN、列数をMとすると、第1の電源電位が低電源電位入力線VSSWに入力されてから寄生容量までの抵抗の大きさRtは、以下の示す式で計算される。

【0053】

Rt=RVSSW+RVSSU×(N/2)+RONN/L+Rpx×(M/2)/L

【0054】

ここで、実際のRVSSUおよびRVDDWは3.5Ω、RONNおよびRONPは6kΩ、RVSSUは0.138Ω、Rpxが28.4Ωである。これらを代入して計算すると、抵抗Rtは44.5Ωとなる。次に寄生容量Ctは以下に示す式で計算される。

【0055】

Ct=Cpx×M×L×3

【0056】

ここで、3を掛けているのは、1画素がRGBの3つの画素回路で構成されているからであり、Cpxyを用いずにCpxとしているのは一度変化してしまったスイッチ制御線をもとの電位に戻すことを考慮しているからである。実際の値を代入すると、寄生容量Ctは66.3nFとなる。ここで、図11に示すモデルからわかるように、第1の電源線と、それに接続されるスイッチ制御線はRC回路を構成している。このRC回路の時定数τは、抵抗Rtと寄生容量Ctを掛けた値である2.95μsとなる。

【0057】

次に、画質の劣化を起こさないように許容される時定数τについて検討する。データ線DATに印加される電位に電位変化ΔVdが与えられた時のスイッチ制御線の電位変化ΔVlは、ΔVd×Cpxy/Cpxで計算でき、電位変化ΔVdが5Vであれば、ΔVlは0.27Vとなる。一方、スイッチ制御線の電位変化ΔVlによる他のデータ線の電位変化ΔVrは、ΔVl×Cpxy/Cpyで計算できる。ΔVrの許容できる電位差は、256階調のうちの1階調の半分程度とすると、5V/256/2で約0.01V以下であるから、ΔVlの許容できる電位差は0.01×15で0.15V以下となる。当初の電位変動が0.27Vで許容できる電位差が0.15Vであることから、減衰率は0.15/0.27=0.55となり時定数τの時間が経過した際の減衰率(0.36)よりも大きいことから、時定数τがデータ線DATにデータ信号が供給される期間Tより小さければ画質の劣化は許容できると考えられる。ここで、本実施形態の例ではデータ信号が供給される期間Tは3μsであり、時定数τは期間Tより小さいので、画質の劣化は許容範囲に抑えられている。

【0058】

一方、第1の電源線と第2の電源線の太さが等しく、全体の幅を太くできない場合には、第1の電源線と第2の電源線の和が本実施形態の場合の第1の電源線と第2の電源線の和と同じになるため、第1の電源線および第2の電源線の幅は40μmとなる。これを代入して計算すると、抵抗Rtは51.0Ωとなり、時定数τは3.38μsとなる。これは期間Tより大きくなるため、許容範囲を外れているといえる。

【0059】

こうすることにより、データ信号印加タイミングにおいて第1の電源線と第2の電源線との間で流れる電流に偏りが生じる場合に、多くの電流が流れる電源線の電源供給能力不足による問題を軽減することができる。また、第1の電源線および第2の電源線のうち太い方の幅が細い方の幅の1.5倍以上もあれば、電位変化が抑制されていることは十分に認識可能である。

【0060】

なお、上述の実施形態では低電源電位入力線VSSWの幅と高電源電位入力線VDDWの幅とが同じとしているが、データ信号印加タイミングに流れる電流量に合わせて異ならせてもよい。より具体的には、第1電源電位および第2電源電位のうち、データ信号印加タイミングでより多くのスイッチ制御信号供給回路が出力する電位に対応する電源電位を供給する外部電源線の幅が、他方の外部電源線の幅より太くなっていてもよい。そうすれば、データ信号印加タイミングにおいて第1の電源線と第2の電源線との間で流れる電流に偏りが生じる場合に、多くの電流が流れる電源線の電源供給能力不足に伴う問題をより軽減することができる。

【0061】

また、上述の例では1フレーム期間がデータ書込み期間と発光期間とで分かれていたが、データ書込み期間と発光期間とが分かれていない有機EL表示装置に本発明を適用してもよい。図12は、各画素回路PCの構成の他の例を示す回路図である。各画素回路PCは、発光素子ILと、発光素子ILに流れる電流を制御する駆動トランジスタDTRと、発光素子ILの発光タイミングを制御する点灯制御スイッチITRと、データ信号供給時に駆動トランジスタDTRとデータ線DATとの間の電位差を記憶する記憶容量C1と、駆動トランジスタDTRが流す電流量を制御する記憶容量C2と、記憶容量C1およびC2に貯まった電荷をリセットするリセットスイッチRTRと、データ信号を入力する対象となる画素回路を選択する選択スイッチSTRと、を含む。駆動トランジスタDTR、点灯制御スイッチITR、リセットスイッチRTR、および選択スイッチSTRはpチャネル型の薄膜トランジスタである。発光素子ILは有機EL素子である。

【0062】

発光素子ILのアノードは点灯制御スイッチITRを介して駆動トランジスタDTRのドレイン電極に接続され、カソードは基準電位を供給する配線に接続される。駆動トランジスタDTRのドレイン電極とゲート電極の間に、リセットスイッチRTRが設けられる。駆動トランジスタDTRのゲート電極とソース電極との間には、記憶容量C2が設けられる。記憶容量C1の一端が選択スイッチSTRを介して駆動トランジスタDTRのゲート電極と接続され、他端がこの画素回路PCに対応するデータ線DATと接続される。

【0063】

画素行Prowのそれぞれに対応して、選択スイッチ制御線SLと、リセットスイッチ制御線AZと、点灯スイッチ制御線AZBとが設けられている。選択スイッチ制御線SLは、対応する画素行Prowの画素回路PCに含まれる選択スイッチSTRのゲート電極に接続される。リセットスイッチ制御線AZは、その画素回路PCに含まれるリセットスイッチRTRのゲート電極に接続される。点灯スイッチ制御線AZBは、その画素回路PCに含まれる点灯制御スイッチITRのゲート電極と接続される。

【0064】

ここで、垂直走査回路YDVは、画素行Prowごとに3本あるスイッチ制御線にスイッチ制御信号を供給する点を除いて図2や図4で説明した例と同じである。また、データ線DATは、図2の例とは異なりRGB切替スイッチDSR,DSG,DSBや、統合データ線DATIを介すことなくデータ線駆動回路XDVに接続されている。

【0065】

本実施形態に係る有機EL表示装置の動作について説明する。1フレーム期間においては、行ごとに画素回路PCにデータ信号が書込まれ、データ信号が書き込まれた画素回路PCは次のフレーム期間にデータ信号が書き込まれるまで発光する。1つの画素行Prowを構成する画素回路PCに含まれる記憶容量C1およびC2にデータ書込みの操作を行う期間を一水平期間(1H)と呼ぶ。

【0066】

この有機EL表示装置の例では、一水平期間のはじめには選択スイッチ制御線SLの電位がハイレベルからローレベルとなり、選択スイッチSTRがオンになる。そして、リセットスイッチ制御線AZの電位がローレベルとなりリセットスイッチRTRがオンされると、駆動トランジスタDTRはダイオード接続され、記憶容量C2に電位差が蓄えられる。次に点灯スイッチ制御線AZBの電位がハイレベルとなり点灯制御スイッチITRがオフになる。その後リセットスイッチ制御線AZの電位がハイレベルとなりリセットスイッチRTRがオフとなり、そのタイミングで映像の階調に応じたデータ信号が供給されると、記憶容量C1および記憶容量C2の直列回路には画素回路駆動電源線PWRからの電源電位とデータ信号の電位との電位差を生じる電荷が蓄えられる。このタイミングがデータ信号印加タイミングである。その後、選択スイッチ制御線SLの電位がハイレベルとなり選択スイッチSTRがオフとされ、さらに点灯スイッチ制御線AZBの電位がローレベルとなり点灯制御スイッチITRがオンとなると、発光素子ILはデータ信号に応じた階調の光を発光する。

【0067】

図13は、図12に示す画素回路を含む有機EL表示装置においてデータ信号印加タイミングにスイッチ制御線に印加される電位を示す図である。本図の表にはデータ信号印加タイミングにおける、選択された画素行の各スイッチ制御線の電位Lselと、選択されずに発光している画素行の各スイッチ制御線の電位Lilmとが示されている。図に示すように、選択された画素行では、選択スイッチ制御線SLにはローレベルの電位が供給され、リセットスイッチ制御線AZと、点灯スイッチ制御線AZBにはハイレベルの電位が供給される。選択されている画素行Prowではハイレベルの電位が供給されるのは選択スイッチ制御線SELのみであり、他のスイッチ制御線にはローレベルの電位が供給される。選択されていない画素行Prowでは、選択スイッチ制御線SLとリセットスイッチ制御線AZとにハイレベルの電位が供給され、点灯スイッチ制御線AZBにはローレベルの電位が供給される。

【0068】

よって、データ信号印加タイミングにおいてハイレベルの電位が供給されるスイッチ制御線の数は選択されている画素行で該当するスイッチ制御線の数に、選択されていない画素行で該当するスイッチ制御線の本数を足した960(2+479×2)本であり、一方ローレベルの電位が供給されるスイッチ制御線の数は、480(1+479×1)本である。

【0069】

この例では第1電源電位を供給する第1の電源線の太さが27μmであり、第2の電源電位を供給する第2の電源線の太さが54μmである。高い方の電源電位を供給する第2の電源線の幅は、低い方の電源電位を供給する第1の電源線の幅の1.5倍以上になっている。第1の電源線の幅と第2の電源線の幅の比は、第1の電源電位に対応する電位が供給されるスイッチ制御線の数と第2の電源電位が供給されるスイッチ制御線の数との比と同じになっている。こうするとはじめに説明した実施形態の例と同じように、データ信号印加タイミングにおいて第1の電源線と第2の電源線との一方に生じる電源供給能力不足を抑制し、それにより起きる問題を軽減することができる。

【符号の説明】

【0070】

DA 表示領域、DIC ドライバ集積回路、FPC フレキシブルプリント基板、SUB アレイ基板、XDV データ線駆動回路、YDV 垂直走査回路、CLA,CLB,CLC RGB切替制御線、DAT,DATR,DATG,DATB データ線、DATI 統合データ線、DSR,DSG,DSB RGB切替スイッチ、ILM,AZB 点灯スイッチ制御線、MST 検査スイッチ制御線、PC,PCR,PCG,PCB 画素回路、Prow 画素行、PWR 画素回路駆動電源線、PX 画素、RES,AZ リセットスイッチ制御線、SEL,SL 選択スイッチ制御線、DTR 駆動トランジスタ、IL 発光素子、ITR 点灯制御スイッチ、MCP,C1,C2,CPP 記憶容量、MTR 検査スイッチ、RTR リセットスイッチ、STR 選択スイッチ、TRN,TRP トランジスタ、BF1,BF2,BFP バッファアンプ、CKB1,CK1,CKB2,CK2 クロック線、FF フリップフロップ回路、GA,GB,GC,GD タイミング制御線、GS 同時選択制御線、NA1 第1のNAND回路、NA2 第2のNAND回路、NR1 NOR回路、NT1 第1のNOT回路、NT2 第2のNOT回路、NT3 第3のNOT回路、SCR スイッチ制御信号制御回路、VDD1 第1の高電源電位供給線、VDD2 第2の高電源電位供給線、VDD3 第3の高電源電位供給線、VS 垂直スタート信号線、VSS1 第1の低電源電位供給線、VSS2 第2の低電源電位供給線、VSS3 第3の低電源電位供給線、VSS4 第4の低電源電位供給線、VDDW 高電源電位入力線、VSSW 低電源電位入力線、BA 白領域、WA グレー領域、SL1,SL2 横スメア線、Cpx,Cpxy 寄生容量、PDV 電源線駆動回路、PH 駆動用電源供給線、PL 駆動用接地線、SCL スイッチ制御線、VDD 高電源電位供給線、VSS 低電源電位供給線。

【特許請求の範囲】

【請求項1】

表示領域内に並んで設けられる複数のデータ線と、

前記表示領域内に並んで設けられるとともにそれぞれ前記各データ線と交差する複数のスイッチ制御線と、

2本の電源線および複数のスイッチ制御信号供給回路を含む垂直走査回路と、

を含み、

前記2本の電源線のうち一方は第1電源電位を供給し、

前記2本の電源線のうち他方は第2電源電位を供給し、

前記各スイッチ制御信号供給回路は、それぞれ前記複数のスイッチ制御線のうちの1つに対応して設けられ、データ信号が前記複数のデータ線に供給されるタイミングにおいて、前記第1電源電位に対応する電位、および、前記第2電源電位に対応する電位のいずれか一方を選択的に対応するスイッチ制御線に対して出力し、

前記第1電源電位および前記第2電源電位のうち、前記タイミングでより多くの前記スイッチ制御信号供給回路が出力する電位に対応する電源電位を供給する電源線の幅が、他方の電源電位を供給する電源線の幅より太い、

ことを特徴とする画像表示装置。

【請求項2】

前記第1電源電位および前記第2電源電位のうち、前記タイミングでより多くの前記スイッチ制御信号供給回路が出力する電位に対応する電源電位を供給する電源線の幅が、他方の電源電位を供給する電源線の幅の1.5倍以上である、

ことを特徴とする請求項1に記載の画像表示装置。

【請求項3】

前記垂直走査回路の外に設けられ、前記第1電源電位を前記2つの電源線の一方に供給する外部電源線と、

前記垂直走査回路の外に設けられ、前記第2電源電位を前記2つの電源線の他方に供給する外部電源線と、をさらに含み、

前記第1電源電位および前記第2電源電位のうち、前記タイミングでより多くの前記スイッチ制御信号供給回路が出力する電位に対応する電源電位を供給する外部電源線の幅は、他方の電源電位を供給する外部電源線の幅より太い、

ことを特徴とする請求項1または2に記載の画像表示装置。

【請求項1】

表示領域内に並んで設けられる複数のデータ線と、

前記表示領域内に並んで設けられるとともにそれぞれ前記各データ線と交差する複数のスイッチ制御線と、

2本の電源線および複数のスイッチ制御信号供給回路を含む垂直走査回路と、

を含み、

前記2本の電源線のうち一方は第1電源電位を供給し、

前記2本の電源線のうち他方は第2電源電位を供給し、

前記各スイッチ制御信号供給回路は、それぞれ前記複数のスイッチ制御線のうちの1つに対応して設けられ、データ信号が前記複数のデータ線に供給されるタイミングにおいて、前記第1電源電位に対応する電位、および、前記第2電源電位に対応する電位のいずれか一方を選択的に対応するスイッチ制御線に対して出力し、

前記第1電源電位および前記第2電源電位のうち、前記タイミングでより多くの前記スイッチ制御信号供給回路が出力する電位に対応する電源電位を供給する電源線の幅が、他方の電源電位を供給する電源線の幅より太い、

ことを特徴とする画像表示装置。

【請求項2】

前記第1電源電位および前記第2電源電位のうち、前記タイミングでより多くの前記スイッチ制御信号供給回路が出力する電位に対応する電源電位を供給する電源線の幅が、他方の電源電位を供給する電源線の幅の1.5倍以上である、

ことを特徴とする請求項1に記載の画像表示装置。

【請求項3】

前記垂直走査回路の外に設けられ、前記第1電源電位を前記2つの電源線の一方に供給する外部電源線と、

前記垂直走査回路の外に設けられ、前記第2電源電位を前記2つの電源線の他方に供給する外部電源線と、をさらに含み、

前記第1電源電位および前記第2電源電位のうち、前記タイミングでより多くの前記スイッチ制御信号供給回路が出力する電位に対応する電源電位を供給する外部電源線の幅は、他方の電源電位を供給する外部電源線の幅より太い、

ことを特徴とする請求項1または2に記載の画像表示装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【公開番号】特開2012−58378(P2012−58378A)

【公開日】平成24年3月22日(2012.3.22)

【国際特許分類】

【出願番号】特願2010−199828(P2010−199828)

【出願日】平成22年9月7日(2010.9.7)

【出願人】(502356528)株式会社 日立ディスプレイズ (2,552)

【出願人】(000001007)キヤノン株式会社 (59,756)

【Fターム(参考)】

【公開日】平成24年3月22日(2012.3.22)

【国際特許分類】

【出願日】平成22年9月7日(2010.9.7)

【出願人】(502356528)株式会社 日立ディスプレイズ (2,552)

【出願人】(000001007)キヤノン株式会社 (59,756)

【Fターム(参考)】

[ Back to top ]