GaN系LED素子

【課題】n側メタル電極の延伸部を通してn型導電層に流れる電流を増加させたGaN系LED素子を提供する。

【解決手段】GaN系LED素子は、複数のGaN系半導体層を含む半導体積層体を有し、該複数のGaN系半導体には、上面および底面を有するp型導電層と、該p型導電層の底面側に配置された活性層と、該p型導電層とで該活性層を挟むように配置されたn型導電層とが含まれる。該p型導電層の上面にはp側電極およびn側メタル電極が互いに重ならないように設けられ、該p側電極は透光性を有する部分を有し、該n側メタル電極は接続部および該接続部から延びる延伸部を有し、該半導体積層体には該p型導電層の上面に開口しその底部に該n型導電層が露出する穴が設けられ、少なくとも該延伸部の一部が該穴を通して該n型導電層に接することにより該n側メタル電極と該n型導電層とが電気的に接続されている。

【解決手段】GaN系LED素子は、複数のGaN系半導体層を含む半導体積層体を有し、該複数のGaN系半導体には、上面および底面を有するp型導電層と、該p型導電層の底面側に配置された活性層と、該p型導電層とで該活性層を挟むように配置されたn型導電層とが含まれる。該p型導電層の上面にはp側電極およびn側メタル電極が互いに重ならないように設けられ、該p側電極は透光性を有する部分を有し、該n側メタル電極は接続部および該接続部から延びる延伸部を有し、該半導体積層体には該p型導電層の上面に開口しその底部に該n型導電層が露出する穴が設けられ、少なくとも該延伸部の一部が該穴を通して該n型導電層に接することにより該n側メタル電極と該n型導電層とが電気的に接続されている。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、GaN系半導体を用いて構成されたpn接合型の発光構造を備えるGaN系LED素子に関する。GaN系半導体は、一般式AlaInbGa1−a−bN(0≦a≦1、0≦b≦1、0≦a+b≦1)で表される化合物半導体であり、窒化物半導体などとも呼ばれる。

【背景技術】

【0002】

pn接合型の発光構造を有するGaN系LED素子、とりわけ、n型導電層とp型導電層との間に活性層を有するダブルヘテロ型のGaN系LED素子は、近紫外〜緑の波長域の光を高い効率で発生させることができる。高効率のGaN系LED素子に蛍光体を組み合わせて構成した白色発光装置が、液晶ディスプレイのバックライトユニット用光源や照明用光源として実用化されている。

【0003】

一般的なGaN系LED素子は、サファイア基板上にMOVPE法によりGaN系半導体をエピタキシャル成長させる工程を経て製造される。この工程では、サファイア基板上にバッファ層を介してn型導電層が形成され、そのn型導電層の上に活性層とp型導電層が順次形成される。電極は、p型導電層の表面と、p型導電層側に露出するn型導電層の表面とに、それぞれ形成される。n側電極は、通常はメタル電極である。p側電極は、導電性酸化物からなる透光性電極とメタル電極との組み合せによって構成される。メタル電極には、ボンディングワイヤ等が接続できるよう、接続部が設けられる。大型のLED素子では、素子内で電流が横方向(GaN系半導体膜の厚さ方向と直交する方向)に広がるのを補助するために、n側とp側のいずれかまたは両方のメタル電極に、接続部に加え延伸部が設けられる(特許文献1〜5)。延伸部はライン状、櫛状、ネット状など、種々の形状に形成され得る。ライン状の延伸部は、腕(アーム)あるいは指(フィンガー)に喩えられる場合がある。

【0004】

MOVPE法を用いてp型導電層を成長させるときの温度を800℃程度の低温とすると、その表面は多数のピットが形成された粗化面(textured surface)となる(非特許文献1)。エッチバック法を用いることによって、この粗化面の任意の一部を平坦化することが可能である(特許文献6)。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2000−164930号公報

【特許文献2】特表2003−524295号公報

【特許文献3】特開2001−345480号公報

【特許文献4】特開2004−221529号公報

【特許文献5】特開2004−56109号公報

【特許文献6】特開2006−196692号公報

【非特許文献】

【0006】

【非特許文献1】L.W. Wu et al., Solid-State Electronics, 47, 2027 (2003)

【発明の概要】

【発明が解決しようとする課題】

【0007】

接続部と延伸部を有するn側メタル電極を、その全体がn型導電層と接するように設けたGaN系LED素子では、該接続部に接合されるボンディングワイヤからn側メタル電

極に供給される電流の多くが接続部から直にn型導電層に流れ込み、延伸部を経由してn型導電層に流れる電流は少ないと考えられる。なぜなら、n型のGaN系半導体は比較的高い導電性を有しており、電極材料との接触抵抗も低いからであり、さらに、GaN系LED素子では、そのようなn型GaN系半導体からなるn型導電層が比較的厚く形成される(通常2μm以上)からである。単純化していえば、n型導電層の抵抗が低いので、電流がn側電極からn型導電層に容易に流れ出すのである。

【0008】

本願発明はかかる考察に基づきなされたものであり、n側メタル電極の延伸部を通してn型導電層に流れる電流を増加させたGaN系LED素子を提供することを、主たる目的とする。

【課題を解決するための手段】

【0009】

本発明の好ましい実施形態に係るGaN系LED素子は、下記構成を備える。

(1)複数のGaN系半導体層を含む半導体積層体を有し、該複数のGaN系半導体には、上面および底面を有するp型導電層と、該p型導電層の底面側に配置された活性層と、該p型導電層とで該活性層を挟むように配置されたn型導電層とが含まれるGaN系LED素子であって;該p型導電層の上面にはp側電極およびn側メタル電極が互いに重ならないように設けられ、該p側電極は透光性を有する部分を有し、該n側メタル電極は接続部および該接続部から延びる延伸部を有し、該半導体積層体には該p型導電層の上面に開口しその底部に該n型導電層が露出する穴が設けられ、少なくとも該延伸部の一部が該穴を通して該n型導電層に接することにより該n側メタル電極と該n型導電層とが電気的に接続されている、GaN系LED素子。

(2)前記n側メタル電極と前記n型導電層との総接触面積が、当該n側メタル電極に含まれる前記接続部の総面積と同等以上である、前記(1)記載のGaN系LED素子。

(3)前記延伸部がAu、Ag、CuまたはAlで形成された高導電層を含む、前記(1)または(2)記載のGaN系LED素子。

(4)前記半導体積層体より低い屈折率を有する絶縁膜が、前記n側メタル電極と前記p型導電層との間を絶縁している前記(1)〜(3)のいずれか記載のGaN系LED素子。

(5)前記p型導電層の上面のうち、前記n側メタル電極が形成された領域が選択的に平坦化されており、その他の領域は粗化されている、前記(1)〜(4)のいずれか記載のGaN系LED素子。

【0010】

本発明の他の好ましい実施形態に係るGaN系LED素子は、下記構成を備える。

(6)複数のGaN系半導体層を含む半導体積層体を有し、該複数のGaN系半導体には、上面および底面を有するp型導電層と、該p型導電層の底面側に配置された活性層と、該p型導電層とで該活性層を挟むように配置されたn型導電層とが含まれ、該p型導電層の上面にはp側電極が設けられ、該p型導電層側に一部露出した該n型導電層の表面にはn側メタル電極が設けられるGaN系LED素子であって;該n側メタル電極は接続部および該接続部から延びる延伸部を有し、該延伸部と該n型導電層との間には互いに孤立した複数のオーミック接触部が設けられている、GaN系LED素子。

(7)前記延伸部と前記n型導電層との間のオーミック接触界面の面積が、前記延伸部と前記n型導電層との物理的接触面積よりも小さい、前記(6)記載のGaN系LED素子。

(8)開口部を有する絶縁膜が前記延伸部と前記n型導電層との間に挿入され、前記延伸部と前記n型導電層とが該開口部を通して接触している、前記(6)記載のGaN系LED素子。

(9)前記延伸部がAu、Ag、CuまたはAlで形成された高導電層を含む、前記(6)〜(8)のいずれか記載のGaN系LED素子。

(10)前記延伸部と前記n型導電層との間に設けられたオーミック接触界面の面積が、

前記接続部から離れるにつれ大きくなっている、前記(6)〜(9)のいずれか記載のGaN系LED素子。

【発明の効果】

【0011】

本発明の実施形態に係る上記GaN系LED素子では、延伸部を通してn型導電層に流れる電流が増加するように、n側メタル電極とn型導電層との接触を制限しているので、n側メタル電極からn型導電層に供給される電流が延伸部を通して接続部から離れた部位まで十分に行き渡る。

【図面の簡単な説明】

【0012】

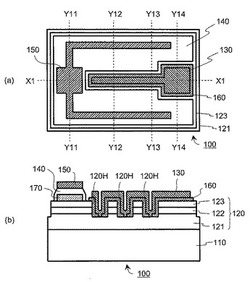

【図1】第1実施形態に係るGaN系LED素子の構造を示しており、図1(a)は平面図、図1(b)は図1(a)のX1−X1線の位置における断面図である。

【図2】第1実施形態に係るGaN系LED素子の構造を示しており、図2(c)は図1(a)のY11−Y11線の位置における断面図であり、図2(d)は図1(a)のY12−Y12線の位置における断面図である。

【図3】第1実施形態に係るGaN系LED素子の構造を示しており、図3(e)は図1(a)のY13−Y13線の位置における断面図であり、図3(f)は図1(a)のY14−Y14線の位置における断面図である。

【図4】第1実施形態に係るGaN系LED素子に含まれるメタル電極のみを抜き出して表示しており、図4(a)はn側メタル電極の平面図、図4(b)はp側メタル電極の平面図である。

【図5】第1実施形態に係るGaN系LED素子の製造方法を説明するための工程断面図である。

【図6】第1実施形態に係るGaN系LED素子の製造方法を説明するための工程断面図である。

【図7】平坦化工程を含むGaN系LED素子の製造方法を説明するための工程断面図である。

【図8】平坦化工程を含むGaN系LED素子の製造方法を説明するための工程断面図である。

【図9】平坦化工程を含むGaN系LED素子の製造方法を説明するための工程断面図である。

【図10】第2実施形態に係るGaN系LED素子の構造を示しており、図10(a)は平面図、図10(b)は図10(a)のX2−X2線の位置における断面図である。ただし、接触制限膜280には図12(a)に示す開口パターンが設けられている。

【図11】第2実施形態に係るGaN系LED素子に含まれるメタル電極のみを抜き出して表示しており、図11(a)はn側メタル電極の平面図、図11(b)はp側メタル電極の平面図である。

【図12】図12(a)〜(c)は、それぞれ、接触制限膜に設けられる開口パターンを例示する平面図である。

【図13】第3実施形態に係るGaN系LED素子の構造を示しており、図13(a)は平面図、図13(b)は図13(a)のX3−X3線の位置における断面図である。ただし、接触制限膜280には図12(a)に示す開口パターンが設けられている。

【図14】第3実施形態に係るGaN系LED素子の構造を示しており、図14(a)および図14(b)は、それぞれ、図13(a)のY31−Y31線およびY32−Y32線の位置における断面図である。

【図15】第3実施形態の変形に係るGaN系LED素子に含まれるメタル電極のみを抜き出して表示しており、図15(a)はn側メタル電極の平面図、図15(b)はp側メタル電極の平面図である。

【0013】

(第1実施形態)

第1実施形態に係るGaN系LED素子100の構造を図1〜図3に示す。図1(a)は平面図であり、図1(b)は図1(a)のX1−X1線の位置における断面図である。また、図2(c)、図2(d)、図3(e)および図3(f)は、それぞれ、図1(a)のY11−Y11線、Y12−Y12線、Y13−Y13線およびY14−Y14線の位置における断面図である。GaN系LED素子100は、基板110上に半導体積層体120を有している。半導体積層体120は、基板110側から順に、それぞれがGaN系半導体からなるn型導電層121、活性層122およびp型導電層123を含んでいる。これらの層は、それぞれが積層構造を有していてもよい。

【0014】

半導体積層体120の上面には、n側メタル電極130と透光性電極140が、互いに重ならないように設けられている。n側メタル電極130とp型導電層123とは絶縁膜160によって隔てられている。透光性電極140上にはp側メタル電極150が部分的に形成されている。透光性電極140とp側メタル電極150とがp側電極を構成している。

【0015】

n側メタル電極130のみを抜き出して表示した平面図が図4(a)、p側メタル電極150のみを抜き出して表示した平面図が図4(b)である。n側メタル電極130は、接続部131および該接続部から延びるライン状の延伸部132とから構成されている。p側メタル電極150は、接続部151および該接続部から延びる2本の延伸部152とから構成されている。p側メタル接続部150の延伸部152は、2つの真直ぐなライン状部分152a、152bが直角をなすように組み合さった形状にパターニングされている。なお、本発明または本明細書でラインという場合には、真直ぐなラインだけではなく、曲がったラインを含むものとする。

【0016】

n側メタル電極130とp側メタル電極150がそれぞれ有する接続部131、151には、LED素子100を実装する際に、ボンディングワイヤ、ハンダ、導電ペースト、メタルバンプなどが接続される。接続部131、151の平面形状は矩形に限定されるものではなく、円形、楕円形などであってもよい。接続部131、151の平面形状が正方形の場合、その1辺は60〜120μmの範囲内であることが好ましい。接続部の平面形状が円形の場合、その直径は60〜120μmの範囲内であることが好ましい。

【0017】

n側メタル電極130とp側メタル電極150のそれぞれの延伸部132、152は、Au、Ag、Cu、Alのような導電率の高い金属で形成された高導電層を含むことが好ましい。高導電層の厚さは好ましくは1μm〜10μm、特に2μm〜5μmである。また、高導電層の幅(ライン幅)は7μm〜30μmとし得るが、好ましくは10μm〜20μmである。機械的な安定性の観点から、延伸部132、152は、高さ(厚さ)よりも幅を大きくすることが好ましい。

【0018】

図1(b)に示すように、半導体積層体120にはp型導電層123の上面に開口する穴120Hが設けられている。穴120Hはn側メタル電極130の延伸部の下方に配置されており、その側壁は絶縁膜160で覆われている。穴120Hの底は絶縁膜160に覆われておらず、露出したn型導電層121とn側メタル電極の延伸部132とが接触している。n側メタル電極130とn型導電層121との接点は、この穴120Hの底にのみ設けられている。

【0019】

穴120Hの開口形状は、円形、正方形、正六角形、正八角形などであり得る。穴120Hは、半導体積層体120の積層方向に直交する平面で切断したときの断面積が、底面から開口部に向かって広くなるように、側壁が傾斜していることが望ましい。側壁をこのように傾斜させることによって、n側メタル電極130の膜厚が極端に薄くなった部分が該側壁上に形成されるのを防ぐことができる。

【0020】

n側メタル電極130とn型導電層121との接触面積の総和(以下、総接触面積ともいう)は、半導体積層体120に設ける穴120Hの数と、ひとつひとつの穴120Hの中にあるn側メタル電極130とn型導電層121の接触部の面積とを調節することにより、設定することができる。n側メタル電極130とn型導電層121の総接触面積が小さ過ぎると、接触抵抗が高くなるので、GaN系LED素子100の順方向電圧が高くなる。順方向電圧の増加を防ぐためには、ひとつのn側メタル電極130とn型導電層123との総接触面積を、当該ひとつのn側メタル電極に含まれる接続部131の面積と同等以上とすることが望ましい。

【0021】

p側メタル電極123の接続部の直下には、透光性電極140とp型導電層123との接触を妨げる電流ブロック層170が設けられている。電流ブロック層170の直下ではp型キャリアの注入が抑制されることから、活性層122で発光が生じない。該領域で生じる光は、p側メタル電極123の接続部による強い遮蔽および吸収を受けるので、その発生を抑制した方が発光効率改善の観点から望ましいのである。

【0022】

以下では、GaN系LED素子100の製造手順の一例を、工程断面図を参照しながら説明する。なお、実際にはウェハサイズの基板上に複数のLED素子を形成するところ、工程断面図では便宜のために1個のLED素子の断面のみを示す。

【0023】

まず、GaN系半導体のエピタキシャル成長に使用可能なウェハサイズ(例えば、直径2インチ)の基板110を準備する(図5(a))。好ましく使用できる基板として、サファイア、スピネル、炭化ケイ素、酸化亜鉛、酸化マグネシウム、GaN、AlGaN、AlN、NGO(NdGaO3)、LGO(LiGaO2)、LAO(LaAlO3)などからなる単結晶基板が挙げられる。特に好ましい基板のひとつは、GaN系半導体を成長させるべき表面に、光散乱を発生させるための凸部または凹部がエッチング加工により形成された、PSS(Patterned Sapphire Substrate)である。

【0024】

次に、準備した基板110上に、エピタキシャル成長法によってn型導電層121、活性層122、p型導電層123を順次成長させて、半導体積層体120を形成する(図5(b))。エピタキシャル成長法としては、MOVPE法、HVPE法、MBE法、スパッタリング法、反応性スパッタ法、その他の公知の方法を適宜用いることができる。

【0025】

GaN系半導体にn型導電性またはp型導電性を付与するために添加することのできる不純物の種類については、公知技術を参照することができる。n型導電層121は、好ましくは、Si(ケイ素)を3×1018〜5×1019cm−3の濃度で添加したAlxGa1−xN(0≦x≦0.05)で、2〜6μmの厚さに形成する。活性層122は、好ましくは、InxGa1−xN(0<x)井戸層とInyGa1−yN(0≦y<x)障壁層とを交互に積層した多重量子井戸層とする。活性層に添加することのできる不純物の種類および濃度、井戸層および障壁層の厚さなどについては、公知技術を参照することができる。

【0026】

p型導電層123は、好ましくは、Mg(マグネシウム)を5×1019〜1×1021cm−3の濃度で添加したAlxGa1−xN(0≦x≦0.05)で、0.05〜2μmの厚さに形成する。

【0027】

基板110とn型導電層121の間、n型導電層121と活性層122の間、活性層122とp型導電層123の間には、公知技術を参照して、様々な機能を有するGaN系半導体層を挿入することができる。例えば、欠陥低減層、歪緩和層、キャップ層(分解防止層)、キャリアブロック層などである。挿入するGaN系半導体層は、超格子のように多

層構造を有するものであってもよい。

【0028】

半導体積層体120の形成が完了したら、図5(c)に示すように、穴120Hを半導体積層体120の所定の位置に形成する。穴120Hの形成は、塩素を含むエッチングガスを用いたドライエッチングによって行うことができる。エッチング深さは、穴120Hの底部にn型導電層121が露出するように設定する。なお、図5(c)の例では、穴120Hの形成と同時に、素子分離溝が形成されている。素子分離溝は、ウェハ上の各素子を電気的に孤立させるために素子間に設ける溝である。LED素子の場合、素子分離溝は活性層が素子毎に孤立する深さに形成すればよいので、穴120Hの形成と同時に素子分離溝を形成することができる。素子分離溝は穴120Hの形成とは別途の工程で形成してもよく、その場合には、基板に達する深さに形成しても構わない。

【0029】

穴120Hの形成後、図5(d)に示すように、半導体積層体120の表面のうち、後の工程でn側メタル電極を形成する領域に、絶縁膜160を形成する。絶縁膜160は、穴120Hの側壁が覆われるように形成するが、穴120Hの底は完全に覆わないようにする。絶縁膜160の材料には、各種の金属酸化物または金属窒化物を特に制限なく使用することができる。例えば、酸化ケイ素、酸化マグネシウム、スピネル、酸化アルミニウム、酸化ジルコニウム、酸化タンタル、酸化ニオブ、酸化チタン、窒化ケイ素、酸窒化ケイ素などである。絶縁膜160のパターニングは通常のフォトリソグラフィ技法を用いて行うことができる。

【0030】

好ましくは、絶縁膜160の屈折率を、半導体積層体120の屈折率よりも低くすると、半導体積層体120と絶縁膜160との界面で全反射が発生するので、絶縁膜160上に形成されるn側メタル電極130による光吸収を抑制することができる。屈折率が低いという点で、絶縁膜160に好ましく用いることができる材料は、酸化ケイ素(SiO2)、スピネル、酸化アルミニウム、酸窒化ケイ素などである。

【0031】

絶縁膜160の形成の次は、図6(e)に示すように、電流ブロック層170を形成する。電流ブロック層170に使用可能な材料は、絶縁膜160に使用可能と同じである。このことから、絶縁膜160と電流ブロック層170は、同じ材料を用いて同時に形成してもよい。

【0032】

電流ブロック層170の形成後、図6(f)に示すように、p型導電層123の表面に、透光性電極140を形成する。透光性電極140は、一部が絶縁膜160と接しても構わない。透光性電極140の材料には、透明導電性酸化物(TCO:Transparent Conductive Oxide)を好ましく用いることができる。ITO、IZO(インジウム亜鉛酸化物)などの酸化インジウムベースのTCO、AZO(アルミニウム亜鉛酸化物)、GZO(ガリウム亜鉛酸化物)などの酸化亜鉛ベースのTCO、FTO(フッ素ドープ酸化錫)などの酸化錫ベースのTCOは、いずれも使用することができる。透光性電極140の形成方法に限定はなく、スパッタ法、反応性スパッタ法、真空蒸着法、イオンビームアシスト蒸着法、イオンプレーティング法、レーザアブレーション法、CVD法、スプレー法、スピンコート法、ディップ法など、公知の方法を適宜用いることができる。透光性電極140は、サブトラクティブ法とアディティブ法(リフトオフ法)のいずれを用いてパターニングしてもよい。透光性電極140がITOで、これをサブトラクティブ法によりパターニングする場合、エッチャントには塩酸あるいは塩化鉄水溶液などが使用できるので、絶縁膜160および電流ブロック層170には、該エッチャントに対し耐性を有するSiO2のような材料を用いればよい。

【0033】

なお、電流ブロック層170は透光性電極140よりも前に形成しておく必要があるが、絶縁膜160と透光性電極140はいずれを先に形成してもよい。

【0034】

透光性電極140の形成後、図6(g)に示すように、n側メタル電極130とp側メタル電極140の形成を行う。形成の順序に特に限定はなく、n側メタル電極130をp側メタル電極140より先に形成してもよいし、後に形成してもよい。n側メタル電極130とp側メタル電極150を同時に形成することも可能であり、その場合、両方の電極の断面構造と厚さは略同一となる。n側メタル電極130は、p側電極である透光性電極140と一部でも接触しないように形成しなくてはならない。n側メタル電極130とp側メタル電極140は、一方または両方を多層膜構造とすることができる。

【0035】

n側メタル電極130は、少なくともn型導電層121に接する部分を、n型のGaN系半導体とオーミック接触を形成し得る材料で形成する。かかる材料として、Al(アルミニウム)、Ti(チタン)、W(タングステン)、Cr(クロム)、V(バナジウム)などが例示される。これらの材料は合金として用いることもできる。近紫外〜青の波長域における反射率が高いことから、AlおよびAl合金は特に好ましい材料である。Al合金としては、Ti、Nd(ネオジム)、Si(ケイ素)、Cu(銅)、Mg(マグネシウム)、Mn(マンガン)、Crなどの添加元素を含むものが例示される。

【0036】

n側メタル電極130およびp側メタル電極150の表面層の材料は、ボンディングワイヤのボンダビリティを考慮して選択することができる。Auワイヤのボンダビリティを高くするには、該表面層をAuまたはAlで形成することが好ましい。n側メタル電極130およびp側メタル電極150には、ボンディングワイヤの代わりにハンダが接合されることもある。ハンダの濡れ性を高くするには、これらの電極の表面層をAu、Ptのような酸化し難い金属、あるいは、使用が予定されているハンダに含まれる成分金属で形成することが好ましい。前述の高導電層の上に、異なる材料からなる表面層を設ける場合には、これらの層の間で所望しない合金化反応が生じることのないように、高融点金属からなるバリア層を両層の間に設けてもよい。ワイヤボンダビリティやハンダの濡れ性を改善するための表面層は、接続部131、151にのみ設けることもできる。

【0037】

p側メタル電極150は、透光性電極140と接する部分を、Al、Ag、白金族(Pt、Pt、Pd、Rh、Ru、Ir)のような反射率の高い金属で形成することができる。透光性電極140をTCOで形成する場合には、該部分をCr、Ni(ニッケル)、Ti(チタン)、Zr(ジルコニウム)、W(タングステン)のような、TCOに対する接着性の良好な金属で形成することが好ましい。

【0038】

図示していないが、ウェハを分割してLED素子をチップ(ダイともいう)にするダイシング工程の前に、半導体積層体120が形成された側のウェハ表面(メタル電極の接続部の表面を除く)に、絶縁性かつ透光性の保護膜を形成する。この保護膜の好ましい材料は、酸化ケイ素、窒化ケイ素、酸窒化ケイ素などである。ダイシングの方法については、公知技術を適宜参照することができる。

【0039】

上記手順によって得られるGaN系LED素子100は、フェイスアップまたはフェイスダウン(フリップチップ)でパッケージに実装することができる。フェイスダウン(フリップチップ)実装した後、更に、レーザリフトオフ技法を用いて半導体積層体120から基板110を取り外すこともできる。

【0040】

(第1実施形態の変形例)

基板110としてc面サファイア基板を用いる場合、半導体積層体120を形成する工程において、最後に成長させるp型導電層123を窒素雰囲気下、700℃〜900℃で成長させると、その表面には多数のピットが発生する。生成するピットの深さが0.1μm以上となるようすると、LED素子の光取出し効率が好ましく改善される。このピット

の発生には貫通転位が関与していることから、GaN基板のような、GaN系半導体との間の格子定数差の小さな結晶基板を用いた場合には、この方法でp型導電層123に粗化面を形成することはできない。かかる結晶基板を用いる場合には、平坦に成長したp型導電層123の表面をナノマスクを用いたエッチングによって粗化することにより、光取出し効率の改善を図ることができる。

【0041】

ここで、p型導電層123の粗化された表面上にn側メタル電極130を形成した場合、n側メタル電極130の裏面がその粗化された表面の形状を反映した荒れた面となり、強い光吸収体となるという問題がある。そこで、エッチバック法を用いて、n側メタル電極130を形成すべき領域だけを、予め平坦化することが望ましい。以下に、エッチバック法による平坦化の手順を、工程断面図を参照しながら説明する。

【0042】

図7(a)は、前述の方法を含む任意の方法を用いてp型導電層123の表面全体を粗化したウェハの断面図(便宜上、1個の素子のみを表示)である。エッチバック法では、最初に、このp型導電層123の粗化された表面全体にエッチング停止膜Aを形成する(図7(b))。エッチング停止膜Aは、メタルあるいはSiO2のような酸化物で形成することができる。次に、フォトリソグラフィ技法を用いて、図7(c)に示すように、平坦化すべき領域の形状に合わせた開口部をエッチング停止膜Aに形成する。開口部形成後、図8(d)に示すように、起伏を平坦に埋め込むマスク層Bで粗化面を覆う。マスク層Bはフォトレジストを用いて形成することができる。

【0043】

次に、マスク層Bの上からウェハをドライエッチする。このとき、エッチング停止膜Aのエッチング速度がマスク層Bのエッチング速度よりも小さくなるように、かつ、マスク層BとGaN系半導体(p型導電層123)のエッチング速度が同等となるように、ドライエッチング条件を設定する。かかる条件を用いると、図8(e)に示すように、エッチング停止膜Aが存在する領域では、該エッチング停止膜Aが露出したところでエッチングが止まる。一方、エッチング停止膜Aが存在しない開口部では、マスク層Bとp型導電層123とが同じ速度でエッチングされるので、図8(f)に示すように、マスク層Bが完全に除去された時点で、エッチング停止膜Aで保護されていないp型導電層123の表面は平坦となる。

【0044】

マスク層Bが完全に除去されたらドライエッチングを終了し、適当なエッチャントを用いてエッチング停止膜Aを除去する(図9(g))。その後の穴120Hを形成する工程からは、前述の第1実施形態と同様に行うことにより、図9(h)に示すように、p型導電層123の上面のうちn側メタル電極130が設けられた領域が選択的に平坦化され、他の領域は粗化されているGaN系LED素子101を得ることができる。

【0045】

(第2実施形態)

第2実施形態に係るGaN系LED素子200の構造を図10に示す。図10(a)は平面図であり、図10(b)は図10(a)のX2−X2線の位置における断面図である。GaN系LED素子200は、基板210上に半導体積層体220を有している。半導体積層体220は、基板210側から順に、それぞれがGaN系半導体からなるn型導電層221、活性層222およびp型導電層223を含んでいる。

【0046】

半導体積層体220の一部ではp型導電層223と活性層222が除去されてn型導電層221が露出している。n型導電層221の露出面上には、接触制限膜280が形成されており、その上にn側メタル電極230が形成されている。p型導電層223の上面には透光性電極240が略全面的に形成され、その上にp側メタル電極250が部分的に形成されている。透光性電極240とp側メタル電極250とがp側電極を構成している。

【0047】

n側メタル電極230のみを抜き出して表示した平面図が図11(a)、p側メタル電極250のみを抜き出して表示した平面図が図11(b)である。n側メタル電極230は、接続部231および該接続部から延びるライン状の延伸部232とから構成されている。p側メタル電極250も同様で、接続部251および該接続部から延びるライン状の延伸部252とから構成されている。

【0048】

第2実施形態のGaN系LED素子200の構成上の特徴は、n型導電層221とn側メタル電極230との間に設けられる接触制限膜280にある。接触制限膜280は絶縁性であり、開口部を有するパターンに形成されている。n型導電層221とn側メタル電極230との接触は、接触制限膜280の開口部を通しての接触に限定されている。この開口部を主としてn側メタル電極の延伸部231とn型導電層221との間に配置することによって、n側メタル電極230からn型導電層221に注入される電流に占める、延伸部232を通して注入される電流の比率の増大が図られている。

【0049】

GaN系LED素子200に含まれる接触制限膜280の平面形状の例を図12(a)〜(c)に示す。図12(a)の接触制限膜280では、円形の開口部OPが複数設けられている。図10(b)に示すGaN系LED素子200の断面図は、接触制限膜280がこの図12(a)に示す平面形状を有している場合の断面図である。

【0050】

接触制限膜280を用いれば、n側メタル電極230の延伸部231の幅を狭くすることなく、n側メタル電極230とn型導電層221との接触に制限を加えることが可能であることが理解されよう。つまり、延伸部232の長手方向の電気抵抗を増加させることなく、接続部231やその近傍でn型導電層221に流れ込む電流を減少させることができるのである。延伸部232の電気抵抗が高いと、この効果が十分に発揮されないことから、延伸部232は、Au、Ag、Cu、Alのような導電率の高い金属で形成された高導電層を含むことが好ましい。この高導電層の厚さは好ましくは1μm〜10μm、特に2μm〜5μmである。また、この高導電層の幅(ライン幅)は7μm〜30μmとし得るが、好ましくは10μm〜20μmである。機械的な安定性の観点から高導電層は高さ(厚さ)よりも幅を大きくすることが好ましい。ただし、メタル材料は活性層222で生じる光の吸収体となることから、高導電層の幅を広くし過ぎた場合にはLED素子200の光出力が低下するので、注意が必要である。

【0051】

図12(b)に平面形状を示す接触制限膜280では、n側メタル電極の延伸部232とn型導電層223との接触面積が、n側メタル電極の接続部231から離れるにつれ大きくなるように、開口部OPの面積を変化させてある。このような接触制限膜280を用いると、n側メタル電極の延伸部232のライン幅を変えることなく、延伸部232とn型導電層221との接触面積を、接続部231からの距離に応じて変化させることができる。

【0052】

図12(c)に示す例では、接触制限膜280に設けられる開口部OPが幾何学的に閉じた形状ではない。すなわち、開口部OPの輪郭線がループを描いていない。開口部OPの平面形状がこの例のような開いた形状であっても、n側メタル電極の延伸部232とn型導電層223との間に、互いに孤立した複数のオーミック接触部を形成するという目的が達成できることは、当業者であれば理解できるであろう。

【0053】

接触制限膜280の材料には、各種の金属酸化物または金属窒化物を特に制限なく使用することができる。例えば、酸化ケイ素、酸化マグネシウム、スピネル、酸化アルミニウム、酸化ジルコニウム、酸化タンタル、酸化ニオブ、酸化チタン、窒化ケイ素、酸窒化ケイ素などである。接触制限膜280の厚さは、例えば50nm〜500nmとすることができる。接触制限膜280のパターニングは通常のフォトリソグラフィ技法を用いて行う

ことができる。

【0054】

第2実施形態に係るGaN系LED素子200に含まれる、上記において特に言及しなかった部位の好ましい態様は、第1実施形態に係るGaN系LED素子100と同様である。

【0055】

(第2実施形態の変形例)

第2実施形態に係るGaN系LED素子200では、触制限膜280が絶縁性の材料で形成されているが、その変形例では、この接触制限膜280を、n型GaN系半導体に対する接触抵抗の高いメタル(以下、「非オーミックメタル」ともいう)で形成する。非オーミックメタルには、例えば、Pt(白金)、Pd(パラジウム)、Rh(ロジウム)のような白金族、Au(金)、Ag(銀)、Cu(銅)、Ni(ニッケル)、Co(コバルト)などがある。非オーミックメタルで形成した接触制限膜280は導体として働くことから、機能上は電極の一部ということができる。

【0056】

(第3実施形態)

第3実施形態に係るGaN系LED素子300の構造を図13および図14に示す。図13(a)は平面図であり、図13(b)、図14(c)および図14(d)は、それぞれ、図13(a)のX3−X3線、Y31−Y31線およびY32−Y32線の位置における断面図である。GaN系LED素子300は、基板310上に半導体積層体320を有している。半導体積層体320は、基板310側から順に、それぞれがGaN系半導体からなるn型導電層321、活性層322およびp型導電層323を含んでいる。

【0057】

半導体積層体320の一部ではp型導電層323と活性層322が除去されてn型導電層321が露出している。n型導電層321の露出面上には、n側電極330が形成されている。p型導電層323の上面には透光性電極340が略全面的に形成され、その上にp側メタル電極350が部分的に形成されている。透光性電極340とp側メタル電極350とがp側電極を構成している。

【0058】

n側メタル電極330のみを抜き出して表示した平面図が図15(a)、p側メタル電極350のみを抜き出して表示した平面図が図15(b)である。n側メタル電極330は、接続部331、第1延伸部332および2つの第2延伸部333とから構成されている。第1延伸部332は接続部331からライン状に延びている。第2延伸部は第1延伸部に接続されている。p側メタル電極350は、接続部351および該接続部から延びる2つの延伸部352とから構成されている。

【0059】

第3実施形態の特徴的な構成は、n側メタル電極330のうちn型導電層321と接する部分が、接続部331および第1延伸部332では非オーミックメタルから構成されており、第2延伸部333ではオーミックメタルから構成されているところである。ここで、オーミックメタルとは、n型GaN系半導体とオーミック接触を形成し得るメタルであり、例えば、Al(アルミニウム)、Ti(チタン)、W(タングステン)、V(バナジウム)、Cr(クロム)などである。これらのメタルを主成分とする合金も、オーミックメタルとなり得る。非オーミックメタルについては、既に定義した通りである。

【0060】

第3実施形態のGaN系LED素子300では、n側メタル電極330からn型導電層321に流れる電流の実質的に全ては、第2延伸部333とn型導電層321との界面を通してn型導電層321に注入される。なぜなら、n側メタル電極330のうち接続部331および第1延伸部332は、n型導電層321と物理的には接触しているものの、これらの部分とn型導電層321との界面では、第2延伸部333とn型導電層321との界面よりも、接触抵抗が高いからである。換言すれば、第2延伸部333とn型導電層3

21との界面だけがオーミック接触界面であり、接続部331とn型導電層321との界面および第1延伸部332とn型導電層321との界面はオーミック接触界面ではないからである。

【0061】

GaN系LED素子300では、図13(a)および図15(a)に示すように、n側メタル電極330を上面視したとき、第2延伸部333が第1延伸部332と交差しているが、かかる構成は必須ではない。例えば、第1延伸部332と第2延伸部333とは、n側メタル電極330を上面視したとき、第1延伸部332の下に第2延伸部333が完全に隠れるように設けることもできる。

【0062】

第1延伸部332は、電気抵抗を低くするために、Au、Ag、Cu、Alのような導電率の高い金属で形成された高導電層を含むことが好ましい。この高導電層の厚さは好ましくは1μm〜10μm、特に2μm〜5μmである。また、この高導電層の幅(ライン幅)は7μm〜30μmとし得るが、好ましくは10μm〜20μmである。第2延伸部333を第1延伸部331から分枝状に延ばす場合には、第2延伸部333中にも同様の高導電層を設けることが望ましい。高導電層をライン状に形成する場合には、機械的な安定性の観点から、その高さ(厚さ)よりも幅を大きくすることが好ましい。ただし、メタル材料は活性層322で生じる光の吸収体となることから、高導電層の幅は広くし過ぎないようにすべきである。

【0063】

第3実施形態に係るGaN系LED素子300に含まれる、上記において特に言及しなかった部位の好ましい態様は、第1実施形態に係るGaN系LED素子100と同様である。

【0064】

以上、本発明を具体的な実施形態に即して説明したが、本発明は上記実施形態に限定されるものではなく、その趣旨を逸脱しない範囲内で種々の変形が可能である。

【符号の説明】

【0065】

100、200、300 GaN系LED素子

110、210、210 基板

120、220、310 半導体積層体

121、221、321 n型導電層

122、222、322 活性層

123、223、323 p型導電層

130、230、330 n側メタル電極

131、231、331 接続部

132、232 延伸部

322 第1延伸部

323 第2延伸部

140、240、340 透光性電極

150、250、350 p側メタル電極

151、251、351 接続部

152、252、352 延伸部

160 絶縁膜

170、370 電流ブロック層

280 接触制限膜

【技術分野】

【0001】

本発明は、GaN系半導体を用いて構成されたpn接合型の発光構造を備えるGaN系LED素子に関する。GaN系半導体は、一般式AlaInbGa1−a−bN(0≦a≦1、0≦b≦1、0≦a+b≦1)で表される化合物半導体であり、窒化物半導体などとも呼ばれる。

【背景技術】

【0002】

pn接合型の発光構造を有するGaN系LED素子、とりわけ、n型導電層とp型導電層との間に活性層を有するダブルヘテロ型のGaN系LED素子は、近紫外〜緑の波長域の光を高い効率で発生させることができる。高効率のGaN系LED素子に蛍光体を組み合わせて構成した白色発光装置が、液晶ディスプレイのバックライトユニット用光源や照明用光源として実用化されている。

【0003】

一般的なGaN系LED素子は、サファイア基板上にMOVPE法によりGaN系半導体をエピタキシャル成長させる工程を経て製造される。この工程では、サファイア基板上にバッファ層を介してn型導電層が形成され、そのn型導電層の上に活性層とp型導電層が順次形成される。電極は、p型導電層の表面と、p型導電層側に露出するn型導電層の表面とに、それぞれ形成される。n側電極は、通常はメタル電極である。p側電極は、導電性酸化物からなる透光性電極とメタル電極との組み合せによって構成される。メタル電極には、ボンディングワイヤ等が接続できるよう、接続部が設けられる。大型のLED素子では、素子内で電流が横方向(GaN系半導体膜の厚さ方向と直交する方向)に広がるのを補助するために、n側とp側のいずれかまたは両方のメタル電極に、接続部に加え延伸部が設けられる(特許文献1〜5)。延伸部はライン状、櫛状、ネット状など、種々の形状に形成され得る。ライン状の延伸部は、腕(アーム)あるいは指(フィンガー)に喩えられる場合がある。

【0004】

MOVPE法を用いてp型導電層を成長させるときの温度を800℃程度の低温とすると、その表面は多数のピットが形成された粗化面(textured surface)となる(非特許文献1)。エッチバック法を用いることによって、この粗化面の任意の一部を平坦化することが可能である(特許文献6)。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2000−164930号公報

【特許文献2】特表2003−524295号公報

【特許文献3】特開2001−345480号公報

【特許文献4】特開2004−221529号公報

【特許文献5】特開2004−56109号公報

【特許文献6】特開2006−196692号公報

【非特許文献】

【0006】

【非特許文献1】L.W. Wu et al., Solid-State Electronics, 47, 2027 (2003)

【発明の概要】

【発明が解決しようとする課題】

【0007】

接続部と延伸部を有するn側メタル電極を、その全体がn型導電層と接するように設けたGaN系LED素子では、該接続部に接合されるボンディングワイヤからn側メタル電

極に供給される電流の多くが接続部から直にn型導電層に流れ込み、延伸部を経由してn型導電層に流れる電流は少ないと考えられる。なぜなら、n型のGaN系半導体は比較的高い導電性を有しており、電極材料との接触抵抗も低いからであり、さらに、GaN系LED素子では、そのようなn型GaN系半導体からなるn型導電層が比較的厚く形成される(通常2μm以上)からである。単純化していえば、n型導電層の抵抗が低いので、電流がn側電極からn型導電層に容易に流れ出すのである。

【0008】

本願発明はかかる考察に基づきなされたものであり、n側メタル電極の延伸部を通してn型導電層に流れる電流を増加させたGaN系LED素子を提供することを、主たる目的とする。

【課題を解決するための手段】

【0009】

本発明の好ましい実施形態に係るGaN系LED素子は、下記構成を備える。

(1)複数のGaN系半導体層を含む半導体積層体を有し、該複数のGaN系半導体には、上面および底面を有するp型導電層と、該p型導電層の底面側に配置された活性層と、該p型導電層とで該活性層を挟むように配置されたn型導電層とが含まれるGaN系LED素子であって;該p型導電層の上面にはp側電極およびn側メタル電極が互いに重ならないように設けられ、該p側電極は透光性を有する部分を有し、該n側メタル電極は接続部および該接続部から延びる延伸部を有し、該半導体積層体には該p型導電層の上面に開口しその底部に該n型導電層が露出する穴が設けられ、少なくとも該延伸部の一部が該穴を通して該n型導電層に接することにより該n側メタル電極と該n型導電層とが電気的に接続されている、GaN系LED素子。

(2)前記n側メタル電極と前記n型導電層との総接触面積が、当該n側メタル電極に含まれる前記接続部の総面積と同等以上である、前記(1)記載のGaN系LED素子。

(3)前記延伸部がAu、Ag、CuまたはAlで形成された高導電層を含む、前記(1)または(2)記載のGaN系LED素子。

(4)前記半導体積層体より低い屈折率を有する絶縁膜が、前記n側メタル電極と前記p型導電層との間を絶縁している前記(1)〜(3)のいずれか記載のGaN系LED素子。

(5)前記p型導電層の上面のうち、前記n側メタル電極が形成された領域が選択的に平坦化されており、その他の領域は粗化されている、前記(1)〜(4)のいずれか記載のGaN系LED素子。

【0010】

本発明の他の好ましい実施形態に係るGaN系LED素子は、下記構成を備える。

(6)複数のGaN系半導体層を含む半導体積層体を有し、該複数のGaN系半導体には、上面および底面を有するp型導電層と、該p型導電層の底面側に配置された活性層と、該p型導電層とで該活性層を挟むように配置されたn型導電層とが含まれ、該p型導電層の上面にはp側電極が設けられ、該p型導電層側に一部露出した該n型導電層の表面にはn側メタル電極が設けられるGaN系LED素子であって;該n側メタル電極は接続部および該接続部から延びる延伸部を有し、該延伸部と該n型導電層との間には互いに孤立した複数のオーミック接触部が設けられている、GaN系LED素子。

(7)前記延伸部と前記n型導電層との間のオーミック接触界面の面積が、前記延伸部と前記n型導電層との物理的接触面積よりも小さい、前記(6)記載のGaN系LED素子。

(8)開口部を有する絶縁膜が前記延伸部と前記n型導電層との間に挿入され、前記延伸部と前記n型導電層とが該開口部を通して接触している、前記(6)記載のGaN系LED素子。

(9)前記延伸部がAu、Ag、CuまたはAlで形成された高導電層を含む、前記(6)〜(8)のいずれか記載のGaN系LED素子。

(10)前記延伸部と前記n型導電層との間に設けられたオーミック接触界面の面積が、

前記接続部から離れるにつれ大きくなっている、前記(6)〜(9)のいずれか記載のGaN系LED素子。

【発明の効果】

【0011】

本発明の実施形態に係る上記GaN系LED素子では、延伸部を通してn型導電層に流れる電流が増加するように、n側メタル電極とn型導電層との接触を制限しているので、n側メタル電極からn型導電層に供給される電流が延伸部を通して接続部から離れた部位まで十分に行き渡る。

【図面の簡単な説明】

【0012】

【図1】第1実施形態に係るGaN系LED素子の構造を示しており、図1(a)は平面図、図1(b)は図1(a)のX1−X1線の位置における断面図である。

【図2】第1実施形態に係るGaN系LED素子の構造を示しており、図2(c)は図1(a)のY11−Y11線の位置における断面図であり、図2(d)は図1(a)のY12−Y12線の位置における断面図である。

【図3】第1実施形態に係るGaN系LED素子の構造を示しており、図3(e)は図1(a)のY13−Y13線の位置における断面図であり、図3(f)は図1(a)のY14−Y14線の位置における断面図である。

【図4】第1実施形態に係るGaN系LED素子に含まれるメタル電極のみを抜き出して表示しており、図4(a)はn側メタル電極の平面図、図4(b)はp側メタル電極の平面図である。

【図5】第1実施形態に係るGaN系LED素子の製造方法を説明するための工程断面図である。

【図6】第1実施形態に係るGaN系LED素子の製造方法を説明するための工程断面図である。

【図7】平坦化工程を含むGaN系LED素子の製造方法を説明するための工程断面図である。

【図8】平坦化工程を含むGaN系LED素子の製造方法を説明するための工程断面図である。

【図9】平坦化工程を含むGaN系LED素子の製造方法を説明するための工程断面図である。

【図10】第2実施形態に係るGaN系LED素子の構造を示しており、図10(a)は平面図、図10(b)は図10(a)のX2−X2線の位置における断面図である。ただし、接触制限膜280には図12(a)に示す開口パターンが設けられている。

【図11】第2実施形態に係るGaN系LED素子に含まれるメタル電極のみを抜き出して表示しており、図11(a)はn側メタル電極の平面図、図11(b)はp側メタル電極の平面図である。

【図12】図12(a)〜(c)は、それぞれ、接触制限膜に設けられる開口パターンを例示する平面図である。

【図13】第3実施形態に係るGaN系LED素子の構造を示しており、図13(a)は平面図、図13(b)は図13(a)のX3−X3線の位置における断面図である。ただし、接触制限膜280には図12(a)に示す開口パターンが設けられている。

【図14】第3実施形態に係るGaN系LED素子の構造を示しており、図14(a)および図14(b)は、それぞれ、図13(a)のY31−Y31線およびY32−Y32線の位置における断面図である。

【図15】第3実施形態の変形に係るGaN系LED素子に含まれるメタル電極のみを抜き出して表示しており、図15(a)はn側メタル電極の平面図、図15(b)はp側メタル電極の平面図である。

【0013】

(第1実施形態)

第1実施形態に係るGaN系LED素子100の構造を図1〜図3に示す。図1(a)は平面図であり、図1(b)は図1(a)のX1−X1線の位置における断面図である。また、図2(c)、図2(d)、図3(e)および図3(f)は、それぞれ、図1(a)のY11−Y11線、Y12−Y12線、Y13−Y13線およびY14−Y14線の位置における断面図である。GaN系LED素子100は、基板110上に半導体積層体120を有している。半導体積層体120は、基板110側から順に、それぞれがGaN系半導体からなるn型導電層121、活性層122およびp型導電層123を含んでいる。これらの層は、それぞれが積層構造を有していてもよい。

【0014】

半導体積層体120の上面には、n側メタル電極130と透光性電極140が、互いに重ならないように設けられている。n側メタル電極130とp型導電層123とは絶縁膜160によって隔てられている。透光性電極140上にはp側メタル電極150が部分的に形成されている。透光性電極140とp側メタル電極150とがp側電極を構成している。

【0015】

n側メタル電極130のみを抜き出して表示した平面図が図4(a)、p側メタル電極150のみを抜き出して表示した平面図が図4(b)である。n側メタル電極130は、接続部131および該接続部から延びるライン状の延伸部132とから構成されている。p側メタル電極150は、接続部151および該接続部から延びる2本の延伸部152とから構成されている。p側メタル接続部150の延伸部152は、2つの真直ぐなライン状部分152a、152bが直角をなすように組み合さった形状にパターニングされている。なお、本発明または本明細書でラインという場合には、真直ぐなラインだけではなく、曲がったラインを含むものとする。

【0016】

n側メタル電極130とp側メタル電極150がそれぞれ有する接続部131、151には、LED素子100を実装する際に、ボンディングワイヤ、ハンダ、導電ペースト、メタルバンプなどが接続される。接続部131、151の平面形状は矩形に限定されるものではなく、円形、楕円形などであってもよい。接続部131、151の平面形状が正方形の場合、その1辺は60〜120μmの範囲内であることが好ましい。接続部の平面形状が円形の場合、その直径は60〜120μmの範囲内であることが好ましい。

【0017】

n側メタル電極130とp側メタル電極150のそれぞれの延伸部132、152は、Au、Ag、Cu、Alのような導電率の高い金属で形成された高導電層を含むことが好ましい。高導電層の厚さは好ましくは1μm〜10μm、特に2μm〜5μmである。また、高導電層の幅(ライン幅)は7μm〜30μmとし得るが、好ましくは10μm〜20μmである。機械的な安定性の観点から、延伸部132、152は、高さ(厚さ)よりも幅を大きくすることが好ましい。

【0018】

図1(b)に示すように、半導体積層体120にはp型導電層123の上面に開口する穴120Hが設けられている。穴120Hはn側メタル電極130の延伸部の下方に配置されており、その側壁は絶縁膜160で覆われている。穴120Hの底は絶縁膜160に覆われておらず、露出したn型導電層121とn側メタル電極の延伸部132とが接触している。n側メタル電極130とn型導電層121との接点は、この穴120Hの底にのみ設けられている。

【0019】

穴120Hの開口形状は、円形、正方形、正六角形、正八角形などであり得る。穴120Hは、半導体積層体120の積層方向に直交する平面で切断したときの断面積が、底面から開口部に向かって広くなるように、側壁が傾斜していることが望ましい。側壁をこのように傾斜させることによって、n側メタル電極130の膜厚が極端に薄くなった部分が該側壁上に形成されるのを防ぐことができる。

【0020】

n側メタル電極130とn型導電層121との接触面積の総和(以下、総接触面積ともいう)は、半導体積層体120に設ける穴120Hの数と、ひとつひとつの穴120Hの中にあるn側メタル電極130とn型導電層121の接触部の面積とを調節することにより、設定することができる。n側メタル電極130とn型導電層121の総接触面積が小さ過ぎると、接触抵抗が高くなるので、GaN系LED素子100の順方向電圧が高くなる。順方向電圧の増加を防ぐためには、ひとつのn側メタル電極130とn型導電層123との総接触面積を、当該ひとつのn側メタル電極に含まれる接続部131の面積と同等以上とすることが望ましい。

【0021】

p側メタル電極123の接続部の直下には、透光性電極140とp型導電層123との接触を妨げる電流ブロック層170が設けられている。電流ブロック層170の直下ではp型キャリアの注入が抑制されることから、活性層122で発光が生じない。該領域で生じる光は、p側メタル電極123の接続部による強い遮蔽および吸収を受けるので、その発生を抑制した方が発光効率改善の観点から望ましいのである。

【0022】

以下では、GaN系LED素子100の製造手順の一例を、工程断面図を参照しながら説明する。なお、実際にはウェハサイズの基板上に複数のLED素子を形成するところ、工程断面図では便宜のために1個のLED素子の断面のみを示す。

【0023】

まず、GaN系半導体のエピタキシャル成長に使用可能なウェハサイズ(例えば、直径2インチ)の基板110を準備する(図5(a))。好ましく使用できる基板として、サファイア、スピネル、炭化ケイ素、酸化亜鉛、酸化マグネシウム、GaN、AlGaN、AlN、NGO(NdGaO3)、LGO(LiGaO2)、LAO(LaAlO3)などからなる単結晶基板が挙げられる。特に好ましい基板のひとつは、GaN系半導体を成長させるべき表面に、光散乱を発生させるための凸部または凹部がエッチング加工により形成された、PSS(Patterned Sapphire Substrate)である。

【0024】

次に、準備した基板110上に、エピタキシャル成長法によってn型導電層121、活性層122、p型導電層123を順次成長させて、半導体積層体120を形成する(図5(b))。エピタキシャル成長法としては、MOVPE法、HVPE法、MBE法、スパッタリング法、反応性スパッタ法、その他の公知の方法を適宜用いることができる。

【0025】

GaN系半導体にn型導電性またはp型導電性を付与するために添加することのできる不純物の種類については、公知技術を参照することができる。n型導電層121は、好ましくは、Si(ケイ素)を3×1018〜5×1019cm−3の濃度で添加したAlxGa1−xN(0≦x≦0.05)で、2〜6μmの厚さに形成する。活性層122は、好ましくは、InxGa1−xN(0<x)井戸層とInyGa1−yN(0≦y<x)障壁層とを交互に積層した多重量子井戸層とする。活性層に添加することのできる不純物の種類および濃度、井戸層および障壁層の厚さなどについては、公知技術を参照することができる。

【0026】

p型導電層123は、好ましくは、Mg(マグネシウム)を5×1019〜1×1021cm−3の濃度で添加したAlxGa1−xN(0≦x≦0.05)で、0.05〜2μmの厚さに形成する。

【0027】

基板110とn型導電層121の間、n型導電層121と活性層122の間、活性層122とp型導電層123の間には、公知技術を参照して、様々な機能を有するGaN系半導体層を挿入することができる。例えば、欠陥低減層、歪緩和層、キャップ層(分解防止層)、キャリアブロック層などである。挿入するGaN系半導体層は、超格子のように多

層構造を有するものであってもよい。

【0028】

半導体積層体120の形成が完了したら、図5(c)に示すように、穴120Hを半導体積層体120の所定の位置に形成する。穴120Hの形成は、塩素を含むエッチングガスを用いたドライエッチングによって行うことができる。エッチング深さは、穴120Hの底部にn型導電層121が露出するように設定する。なお、図5(c)の例では、穴120Hの形成と同時に、素子分離溝が形成されている。素子分離溝は、ウェハ上の各素子を電気的に孤立させるために素子間に設ける溝である。LED素子の場合、素子分離溝は活性層が素子毎に孤立する深さに形成すればよいので、穴120Hの形成と同時に素子分離溝を形成することができる。素子分離溝は穴120Hの形成とは別途の工程で形成してもよく、その場合には、基板に達する深さに形成しても構わない。

【0029】

穴120Hの形成後、図5(d)に示すように、半導体積層体120の表面のうち、後の工程でn側メタル電極を形成する領域に、絶縁膜160を形成する。絶縁膜160は、穴120Hの側壁が覆われるように形成するが、穴120Hの底は完全に覆わないようにする。絶縁膜160の材料には、各種の金属酸化物または金属窒化物を特に制限なく使用することができる。例えば、酸化ケイ素、酸化マグネシウム、スピネル、酸化アルミニウム、酸化ジルコニウム、酸化タンタル、酸化ニオブ、酸化チタン、窒化ケイ素、酸窒化ケイ素などである。絶縁膜160のパターニングは通常のフォトリソグラフィ技法を用いて行うことができる。

【0030】

好ましくは、絶縁膜160の屈折率を、半導体積層体120の屈折率よりも低くすると、半導体積層体120と絶縁膜160との界面で全反射が発生するので、絶縁膜160上に形成されるn側メタル電極130による光吸収を抑制することができる。屈折率が低いという点で、絶縁膜160に好ましく用いることができる材料は、酸化ケイ素(SiO2)、スピネル、酸化アルミニウム、酸窒化ケイ素などである。

【0031】

絶縁膜160の形成の次は、図6(e)に示すように、電流ブロック層170を形成する。電流ブロック層170に使用可能な材料は、絶縁膜160に使用可能と同じである。このことから、絶縁膜160と電流ブロック層170は、同じ材料を用いて同時に形成してもよい。

【0032】

電流ブロック層170の形成後、図6(f)に示すように、p型導電層123の表面に、透光性電極140を形成する。透光性電極140は、一部が絶縁膜160と接しても構わない。透光性電極140の材料には、透明導電性酸化物(TCO:Transparent Conductive Oxide)を好ましく用いることができる。ITO、IZO(インジウム亜鉛酸化物)などの酸化インジウムベースのTCO、AZO(アルミニウム亜鉛酸化物)、GZO(ガリウム亜鉛酸化物)などの酸化亜鉛ベースのTCO、FTO(フッ素ドープ酸化錫)などの酸化錫ベースのTCOは、いずれも使用することができる。透光性電極140の形成方法に限定はなく、スパッタ法、反応性スパッタ法、真空蒸着法、イオンビームアシスト蒸着法、イオンプレーティング法、レーザアブレーション法、CVD法、スプレー法、スピンコート法、ディップ法など、公知の方法を適宜用いることができる。透光性電極140は、サブトラクティブ法とアディティブ法(リフトオフ法)のいずれを用いてパターニングしてもよい。透光性電極140がITOで、これをサブトラクティブ法によりパターニングする場合、エッチャントには塩酸あるいは塩化鉄水溶液などが使用できるので、絶縁膜160および電流ブロック層170には、該エッチャントに対し耐性を有するSiO2のような材料を用いればよい。

【0033】

なお、電流ブロック層170は透光性電極140よりも前に形成しておく必要があるが、絶縁膜160と透光性電極140はいずれを先に形成してもよい。

【0034】

透光性電極140の形成後、図6(g)に示すように、n側メタル電極130とp側メタル電極140の形成を行う。形成の順序に特に限定はなく、n側メタル電極130をp側メタル電極140より先に形成してもよいし、後に形成してもよい。n側メタル電極130とp側メタル電極150を同時に形成することも可能であり、その場合、両方の電極の断面構造と厚さは略同一となる。n側メタル電極130は、p側電極である透光性電極140と一部でも接触しないように形成しなくてはならない。n側メタル電極130とp側メタル電極140は、一方または両方を多層膜構造とすることができる。

【0035】

n側メタル電極130は、少なくともn型導電層121に接する部分を、n型のGaN系半導体とオーミック接触を形成し得る材料で形成する。かかる材料として、Al(アルミニウム)、Ti(チタン)、W(タングステン)、Cr(クロム)、V(バナジウム)などが例示される。これらの材料は合金として用いることもできる。近紫外〜青の波長域における反射率が高いことから、AlおよびAl合金は特に好ましい材料である。Al合金としては、Ti、Nd(ネオジム)、Si(ケイ素)、Cu(銅)、Mg(マグネシウム)、Mn(マンガン)、Crなどの添加元素を含むものが例示される。

【0036】

n側メタル電極130およびp側メタル電極150の表面層の材料は、ボンディングワイヤのボンダビリティを考慮して選択することができる。Auワイヤのボンダビリティを高くするには、該表面層をAuまたはAlで形成することが好ましい。n側メタル電極130およびp側メタル電極150には、ボンディングワイヤの代わりにハンダが接合されることもある。ハンダの濡れ性を高くするには、これらの電極の表面層をAu、Ptのような酸化し難い金属、あるいは、使用が予定されているハンダに含まれる成分金属で形成することが好ましい。前述の高導電層の上に、異なる材料からなる表面層を設ける場合には、これらの層の間で所望しない合金化反応が生じることのないように、高融点金属からなるバリア層を両層の間に設けてもよい。ワイヤボンダビリティやハンダの濡れ性を改善するための表面層は、接続部131、151にのみ設けることもできる。

【0037】

p側メタル電極150は、透光性電極140と接する部分を、Al、Ag、白金族(Pt、Pt、Pd、Rh、Ru、Ir)のような反射率の高い金属で形成することができる。透光性電極140をTCOで形成する場合には、該部分をCr、Ni(ニッケル)、Ti(チタン)、Zr(ジルコニウム)、W(タングステン)のような、TCOに対する接着性の良好な金属で形成することが好ましい。

【0038】

図示していないが、ウェハを分割してLED素子をチップ(ダイともいう)にするダイシング工程の前に、半導体積層体120が形成された側のウェハ表面(メタル電極の接続部の表面を除く)に、絶縁性かつ透光性の保護膜を形成する。この保護膜の好ましい材料は、酸化ケイ素、窒化ケイ素、酸窒化ケイ素などである。ダイシングの方法については、公知技術を適宜参照することができる。

【0039】

上記手順によって得られるGaN系LED素子100は、フェイスアップまたはフェイスダウン(フリップチップ)でパッケージに実装することができる。フェイスダウン(フリップチップ)実装した後、更に、レーザリフトオフ技法を用いて半導体積層体120から基板110を取り外すこともできる。

【0040】

(第1実施形態の変形例)

基板110としてc面サファイア基板を用いる場合、半導体積層体120を形成する工程において、最後に成長させるp型導電層123を窒素雰囲気下、700℃〜900℃で成長させると、その表面には多数のピットが発生する。生成するピットの深さが0.1μm以上となるようすると、LED素子の光取出し効率が好ましく改善される。このピット

の発生には貫通転位が関与していることから、GaN基板のような、GaN系半導体との間の格子定数差の小さな結晶基板を用いた場合には、この方法でp型導電層123に粗化面を形成することはできない。かかる結晶基板を用いる場合には、平坦に成長したp型導電層123の表面をナノマスクを用いたエッチングによって粗化することにより、光取出し効率の改善を図ることができる。

【0041】

ここで、p型導電層123の粗化された表面上にn側メタル電極130を形成した場合、n側メタル電極130の裏面がその粗化された表面の形状を反映した荒れた面となり、強い光吸収体となるという問題がある。そこで、エッチバック法を用いて、n側メタル電極130を形成すべき領域だけを、予め平坦化することが望ましい。以下に、エッチバック法による平坦化の手順を、工程断面図を参照しながら説明する。

【0042】

図7(a)は、前述の方法を含む任意の方法を用いてp型導電層123の表面全体を粗化したウェハの断面図(便宜上、1個の素子のみを表示)である。エッチバック法では、最初に、このp型導電層123の粗化された表面全体にエッチング停止膜Aを形成する(図7(b))。エッチング停止膜Aは、メタルあるいはSiO2のような酸化物で形成することができる。次に、フォトリソグラフィ技法を用いて、図7(c)に示すように、平坦化すべき領域の形状に合わせた開口部をエッチング停止膜Aに形成する。開口部形成後、図8(d)に示すように、起伏を平坦に埋め込むマスク層Bで粗化面を覆う。マスク層Bはフォトレジストを用いて形成することができる。

【0043】

次に、マスク層Bの上からウェハをドライエッチする。このとき、エッチング停止膜Aのエッチング速度がマスク層Bのエッチング速度よりも小さくなるように、かつ、マスク層BとGaN系半導体(p型導電層123)のエッチング速度が同等となるように、ドライエッチング条件を設定する。かかる条件を用いると、図8(e)に示すように、エッチング停止膜Aが存在する領域では、該エッチング停止膜Aが露出したところでエッチングが止まる。一方、エッチング停止膜Aが存在しない開口部では、マスク層Bとp型導電層123とが同じ速度でエッチングされるので、図8(f)に示すように、マスク層Bが完全に除去された時点で、エッチング停止膜Aで保護されていないp型導電層123の表面は平坦となる。

【0044】

マスク層Bが完全に除去されたらドライエッチングを終了し、適当なエッチャントを用いてエッチング停止膜Aを除去する(図9(g))。その後の穴120Hを形成する工程からは、前述の第1実施形態と同様に行うことにより、図9(h)に示すように、p型導電層123の上面のうちn側メタル電極130が設けられた領域が選択的に平坦化され、他の領域は粗化されているGaN系LED素子101を得ることができる。

【0045】

(第2実施形態)

第2実施形態に係るGaN系LED素子200の構造を図10に示す。図10(a)は平面図であり、図10(b)は図10(a)のX2−X2線の位置における断面図である。GaN系LED素子200は、基板210上に半導体積層体220を有している。半導体積層体220は、基板210側から順に、それぞれがGaN系半導体からなるn型導電層221、活性層222およびp型導電層223を含んでいる。

【0046】

半導体積層体220の一部ではp型導電層223と活性層222が除去されてn型導電層221が露出している。n型導電層221の露出面上には、接触制限膜280が形成されており、その上にn側メタル電極230が形成されている。p型導電層223の上面には透光性電極240が略全面的に形成され、その上にp側メタル電極250が部分的に形成されている。透光性電極240とp側メタル電極250とがp側電極を構成している。

【0047】

n側メタル電極230のみを抜き出して表示した平面図が図11(a)、p側メタル電極250のみを抜き出して表示した平面図が図11(b)である。n側メタル電極230は、接続部231および該接続部から延びるライン状の延伸部232とから構成されている。p側メタル電極250も同様で、接続部251および該接続部から延びるライン状の延伸部252とから構成されている。

【0048】

第2実施形態のGaN系LED素子200の構成上の特徴は、n型導電層221とn側メタル電極230との間に設けられる接触制限膜280にある。接触制限膜280は絶縁性であり、開口部を有するパターンに形成されている。n型導電層221とn側メタル電極230との接触は、接触制限膜280の開口部を通しての接触に限定されている。この開口部を主としてn側メタル電極の延伸部231とn型導電層221との間に配置することによって、n側メタル電極230からn型導電層221に注入される電流に占める、延伸部232を通して注入される電流の比率の増大が図られている。

【0049】

GaN系LED素子200に含まれる接触制限膜280の平面形状の例を図12(a)〜(c)に示す。図12(a)の接触制限膜280では、円形の開口部OPが複数設けられている。図10(b)に示すGaN系LED素子200の断面図は、接触制限膜280がこの図12(a)に示す平面形状を有している場合の断面図である。

【0050】

接触制限膜280を用いれば、n側メタル電極230の延伸部231の幅を狭くすることなく、n側メタル電極230とn型導電層221との接触に制限を加えることが可能であることが理解されよう。つまり、延伸部232の長手方向の電気抵抗を増加させることなく、接続部231やその近傍でn型導電層221に流れ込む電流を減少させることができるのである。延伸部232の電気抵抗が高いと、この効果が十分に発揮されないことから、延伸部232は、Au、Ag、Cu、Alのような導電率の高い金属で形成された高導電層を含むことが好ましい。この高導電層の厚さは好ましくは1μm〜10μm、特に2μm〜5μmである。また、この高導電層の幅(ライン幅)は7μm〜30μmとし得るが、好ましくは10μm〜20μmである。機械的な安定性の観点から高導電層は高さ(厚さ)よりも幅を大きくすることが好ましい。ただし、メタル材料は活性層222で生じる光の吸収体となることから、高導電層の幅を広くし過ぎた場合にはLED素子200の光出力が低下するので、注意が必要である。

【0051】

図12(b)に平面形状を示す接触制限膜280では、n側メタル電極の延伸部232とn型導電層223との接触面積が、n側メタル電極の接続部231から離れるにつれ大きくなるように、開口部OPの面積を変化させてある。このような接触制限膜280を用いると、n側メタル電極の延伸部232のライン幅を変えることなく、延伸部232とn型導電層221との接触面積を、接続部231からの距離に応じて変化させることができる。

【0052】

図12(c)に示す例では、接触制限膜280に設けられる開口部OPが幾何学的に閉じた形状ではない。すなわち、開口部OPの輪郭線がループを描いていない。開口部OPの平面形状がこの例のような開いた形状であっても、n側メタル電極の延伸部232とn型導電層223との間に、互いに孤立した複数のオーミック接触部を形成するという目的が達成できることは、当業者であれば理解できるであろう。

【0053】

接触制限膜280の材料には、各種の金属酸化物または金属窒化物を特に制限なく使用することができる。例えば、酸化ケイ素、酸化マグネシウム、スピネル、酸化アルミニウム、酸化ジルコニウム、酸化タンタル、酸化ニオブ、酸化チタン、窒化ケイ素、酸窒化ケイ素などである。接触制限膜280の厚さは、例えば50nm〜500nmとすることができる。接触制限膜280のパターニングは通常のフォトリソグラフィ技法を用いて行う

ことができる。

【0054】

第2実施形態に係るGaN系LED素子200に含まれる、上記において特に言及しなかった部位の好ましい態様は、第1実施形態に係るGaN系LED素子100と同様である。

【0055】

(第2実施形態の変形例)

第2実施形態に係るGaN系LED素子200では、触制限膜280が絶縁性の材料で形成されているが、その変形例では、この接触制限膜280を、n型GaN系半導体に対する接触抵抗の高いメタル(以下、「非オーミックメタル」ともいう)で形成する。非オーミックメタルには、例えば、Pt(白金)、Pd(パラジウム)、Rh(ロジウム)のような白金族、Au(金)、Ag(銀)、Cu(銅)、Ni(ニッケル)、Co(コバルト)などがある。非オーミックメタルで形成した接触制限膜280は導体として働くことから、機能上は電極の一部ということができる。

【0056】

(第3実施形態)

第3実施形態に係るGaN系LED素子300の構造を図13および図14に示す。図13(a)は平面図であり、図13(b)、図14(c)および図14(d)は、それぞれ、図13(a)のX3−X3線、Y31−Y31線およびY32−Y32線の位置における断面図である。GaN系LED素子300は、基板310上に半導体積層体320を有している。半導体積層体320は、基板310側から順に、それぞれがGaN系半導体からなるn型導電層321、活性層322およびp型導電層323を含んでいる。

【0057】

半導体積層体320の一部ではp型導電層323と活性層322が除去されてn型導電層321が露出している。n型導電層321の露出面上には、n側電極330が形成されている。p型導電層323の上面には透光性電極340が略全面的に形成され、その上にp側メタル電極350が部分的に形成されている。透光性電極340とp側メタル電極350とがp側電極を構成している。

【0058】

n側メタル電極330のみを抜き出して表示した平面図が図15(a)、p側メタル電極350のみを抜き出して表示した平面図が図15(b)である。n側メタル電極330は、接続部331、第1延伸部332および2つの第2延伸部333とから構成されている。第1延伸部332は接続部331からライン状に延びている。第2延伸部は第1延伸部に接続されている。p側メタル電極350は、接続部351および該接続部から延びる2つの延伸部352とから構成されている。

【0059】

第3実施形態の特徴的な構成は、n側メタル電極330のうちn型導電層321と接する部分が、接続部331および第1延伸部332では非オーミックメタルから構成されており、第2延伸部333ではオーミックメタルから構成されているところである。ここで、オーミックメタルとは、n型GaN系半導体とオーミック接触を形成し得るメタルであり、例えば、Al(アルミニウム)、Ti(チタン)、W(タングステン)、V(バナジウム)、Cr(クロム)などである。これらのメタルを主成分とする合金も、オーミックメタルとなり得る。非オーミックメタルについては、既に定義した通りである。

【0060】

第3実施形態のGaN系LED素子300では、n側メタル電極330からn型導電層321に流れる電流の実質的に全ては、第2延伸部333とn型導電層321との界面を通してn型導電層321に注入される。なぜなら、n側メタル電極330のうち接続部331および第1延伸部332は、n型導電層321と物理的には接触しているものの、これらの部分とn型導電層321との界面では、第2延伸部333とn型導電層321との界面よりも、接触抵抗が高いからである。換言すれば、第2延伸部333とn型導電層3

21との界面だけがオーミック接触界面であり、接続部331とn型導電層321との界面および第1延伸部332とn型導電層321との界面はオーミック接触界面ではないからである。

【0061】

GaN系LED素子300では、図13(a)および図15(a)に示すように、n側メタル電極330を上面視したとき、第2延伸部333が第1延伸部332と交差しているが、かかる構成は必須ではない。例えば、第1延伸部332と第2延伸部333とは、n側メタル電極330を上面視したとき、第1延伸部332の下に第2延伸部333が完全に隠れるように設けることもできる。

【0062】

第1延伸部332は、電気抵抗を低くするために、Au、Ag、Cu、Alのような導電率の高い金属で形成された高導電層を含むことが好ましい。この高導電層の厚さは好ましくは1μm〜10μm、特に2μm〜5μmである。また、この高導電層の幅(ライン幅)は7μm〜30μmとし得るが、好ましくは10μm〜20μmである。第2延伸部333を第1延伸部331から分枝状に延ばす場合には、第2延伸部333中にも同様の高導電層を設けることが望ましい。高導電層をライン状に形成する場合には、機械的な安定性の観点から、その高さ(厚さ)よりも幅を大きくすることが好ましい。ただし、メタル材料は活性層322で生じる光の吸収体となることから、高導電層の幅は広くし過ぎないようにすべきである。

【0063】

第3実施形態に係るGaN系LED素子300に含まれる、上記において特に言及しなかった部位の好ましい態様は、第1実施形態に係るGaN系LED素子100と同様である。

【0064】

以上、本発明を具体的な実施形態に即して説明したが、本発明は上記実施形態に限定されるものではなく、その趣旨を逸脱しない範囲内で種々の変形が可能である。

【符号の説明】

【0065】

100、200、300 GaN系LED素子

110、210、210 基板

120、220、310 半導体積層体

121、221、321 n型導電層

122、222、322 活性層

123、223、323 p型導電層

130、230、330 n側メタル電極

131、231、331 接続部

132、232 延伸部

322 第1延伸部

323 第2延伸部

140、240、340 透光性電極

150、250、350 p側メタル電極

151、251、351 接続部

152、252、352 延伸部

160 絶縁膜

170、370 電流ブロック層

280 接触制限膜

【特許請求の範囲】

【請求項1】

複数のGaN系半導体層を含む半導体積層体を有し、該複数のGaN系半導体には、上面および底面を有するp型導電層と、該p型導電層の底面側に配置された活性層と、該p型導電層とで該活性層を挟むように配置されたn型導電層とが含まれるGaN系LED素子であって、

該p型導電層の上面にはp側電極およびn側メタル電極が互いに重ならないように設けられ、

該p側電極は透光性を有する部分を有し、

該n側メタル電極は接続部および該接続部から延びる延伸部を有し、

該半導体積層体には該p型導電層の上面に開口しその底部に該n型導電層が露出する穴が設けられ、少なくとも該延伸部の一部が該穴を通して該n型導電層に接することにより該n側メタル電極と該n型導電層とが電気的に接続されている、GaN系LED素子。

【請求項2】

前記n側メタル電極と前記n型導電層との総接触面積が、当該n側メタル電極に含まれる前記接続部の総面積と同等以上である、請求項1記載のGaN系LED素子。

【請求項3】

前記延伸部がAu、Ag、CuまたはAlで形成された高導電層を含む、請求項1または2記載のGaN系LED素子。

【請求項4】

前記半導体積層体より低い屈折率を有する絶縁膜が、前記n側メタル電極と前記p型導電層との間を絶縁している、請求項1〜3のいずれか一項記載のGaN系LED素子。

【請求項5】

前記p型導電層の上面のうち、前記n側メタル電極が形成された領域が選択的に平坦化されており、その他の領域は粗化されている、請求項1〜4のいずれか一項記載のGaN系LED素子。

【請求項6】

複数のGaN系半導体層を含む半導体積層体を有し、該複数のGaN系半導体には、上面および底面を有するp型導電層と、該p型導電層の底面側に配置された活性層と、該p型導電層とで該活性層を挟むように配置されたn型導電層とが含まれるGaN系LED素子であって、

該n側メタル電極は接続部および該接続部から延びる延伸部を有し、該延伸部と該n型導電層との間には互いに孤立した複数のオーミック接触部が設けられている、GaN系LED素子。

【請求項7】

前記延伸部と前記n型導電層との間のオーミック接触界面の面積が、前記延伸部と前記n型導電層との物理的接触面積よりも小さい、請求項6に記載のGaN系LED素子。

【請求項8】

開口部を有する絶縁膜が前記延伸部と前記n型導電層との間に挿入され、前記延伸部と前記n型導電層とが該開口部を通して接触している、請求項6に記載のGaN系LED素子。

【請求項9】

前記延伸部がAu、Ag、CuまたはAlで形成された高導電層を含む、請求項6〜8のいずれかに記載のGaN系LED素子。

【請求項10】

前記延伸部と前記n型導電層との間に設けられたオーミック接触界面の面積が、前記接続部から離れるにつれ大きくなっている、請求項6〜9のいずれか一項記載のGaN系LED素子。

【請求項1】

複数のGaN系半導体層を含む半導体積層体を有し、該複数のGaN系半導体には、上面および底面を有するp型導電層と、該p型導電層の底面側に配置された活性層と、該p型導電層とで該活性層を挟むように配置されたn型導電層とが含まれるGaN系LED素子であって、

該p型導電層の上面にはp側電極およびn側メタル電極が互いに重ならないように設けられ、

該p側電極は透光性を有する部分を有し、

該n側メタル電極は接続部および該接続部から延びる延伸部を有し、

該半導体積層体には該p型導電層の上面に開口しその底部に該n型導電層が露出する穴が設けられ、少なくとも該延伸部の一部が該穴を通して該n型導電層に接することにより該n側メタル電極と該n型導電層とが電気的に接続されている、GaN系LED素子。

【請求項2】

前記n側メタル電極と前記n型導電層との総接触面積が、当該n側メタル電極に含まれる前記接続部の総面積と同等以上である、請求項1記載のGaN系LED素子。

【請求項3】

前記延伸部がAu、Ag、CuまたはAlで形成された高導電層を含む、請求項1または2記載のGaN系LED素子。

【請求項4】

前記半導体積層体より低い屈折率を有する絶縁膜が、前記n側メタル電極と前記p型導電層との間を絶縁している、請求項1〜3のいずれか一項記載のGaN系LED素子。

【請求項5】

前記p型導電層の上面のうち、前記n側メタル電極が形成された領域が選択的に平坦化されており、その他の領域は粗化されている、請求項1〜4のいずれか一項記載のGaN系LED素子。

【請求項6】

複数のGaN系半導体層を含む半導体積層体を有し、該複数のGaN系半導体には、上面および底面を有するp型導電層と、該p型導電層の底面側に配置された活性層と、該p型導電層とで該活性層を挟むように配置されたn型導電層とが含まれるGaN系LED素子であって、

該n側メタル電極は接続部および該接続部から延びる延伸部を有し、該延伸部と該n型導電層との間には互いに孤立した複数のオーミック接触部が設けられている、GaN系LED素子。

【請求項7】

前記延伸部と前記n型導電層との間のオーミック接触界面の面積が、前記延伸部と前記n型導電層との物理的接触面積よりも小さい、請求項6に記載のGaN系LED素子。

【請求項8】

開口部を有する絶縁膜が前記延伸部と前記n型導電層との間に挿入され、前記延伸部と前記n型導電層とが該開口部を通して接触している、請求項6に記載のGaN系LED素子。

【請求項9】

前記延伸部がAu、Ag、CuまたはAlで形成された高導電層を含む、請求項6〜8のいずれかに記載のGaN系LED素子。

【請求項10】

前記延伸部と前記n型導電層との間に設けられたオーミック接触界面の面積が、前記接続部から離れるにつれ大きくなっている、請求項6〜9のいずれか一項記載のGaN系LED素子。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【公開番号】特開2013−48200(P2013−48200A)

【公開日】平成25年3月7日(2013.3.7)

【国際特許分類】

【出願番号】特願2011−228938(P2011−228938)

【出願日】平成23年10月18日(2011.10.18)

【出願人】(000005968)三菱化学株式会社 (4,356)

【Fターム(参考)】

【公開日】平成25年3月7日(2013.3.7)

【国際特許分類】

【出願日】平成23年10月18日(2011.10.18)

【出願人】(000005968)三菱化学株式会社 (4,356)

【Fターム(参考)】

[ Back to top ]