Fターム[2G014AA03]の内容

短絡、断線、漏洩、誤接続の試験 (9,053) | 検査内容 (3,191) | 接続状態 (2,290) | 短絡 (710)

Fターム[2G014AA03]の下位に属するFターム

Fターム[2G014AA03]に分類される特許

121 - 140 / 525

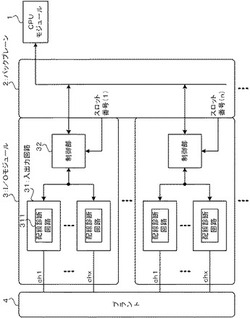

プラント制御システム

【課題】配線診断を正確に行うことができるプラント制御システムを実現することを目的にする。

【解決手段】本発明は、プラントの制御を行うプラント制御システムに改良を加えたものである。本システムは、トリガ信号を出力する制御装置と、この制御装置のトリガ信号を入力し、トリガ信号の入力からスロット番号に対応した時間経過後、プラントとの配線診断を行う複数のモジュールとを備えたことを特徴とする装置である。

(もっと読む)

試験装置、試験方法、プログラムおよびインターフェイス回路

【課題】少ない構成でオープン試験を行う。

【解決手段】被試験デバイスを試験する試験装置であって、被試験デバイスの電源入力端子に電源電圧を供給する電源部と、被試験デバイスの信号端子に試験信号を供給する信号供給部と、信号端子に供給する電圧より低い電源電圧を電源入力端子に供給した状態において、信号端子に入力された過電圧を電源入力端子へと流すための被試験デバイス内の保護ダイオードを介して信号供給部から電源入力端子へと流れる電流を検出する検出部と、信号端子から電源入力端子へと流れる電流を検出した場合に、信号供給部および信号端子の間がオープンでないと判定するオープン判定部と、を備える試験装置を提供する。

(もっと読む)

電子回路の検査方法

【課題】電子回路の実装状態の検査に使用する検査装置の簡素化を図るとともに、インサーキットテスタによらないECU単体での検査対象回路の検査を実現する電子回路の検査方法を提供し、テストパッドの削減および省略を図ることによりECUの小型化を実現する。

【解決手段】マイコン3から検査対象回路2に対して、特性に応じた出力信号Voutを出力する工程と、出力信号Voutを検査対象回路2に通過させて、特性に応じて変化した計測対象信号Vbを生成する工程と、計測対象信号Vbをマイコン3に入力する工程と、マイコン3によって、出力信号Voutが出力された時刻から、計測対象信号Vbの値と予め設定した閾値X1等との大小関係が入れ替わる時刻までの時間である遅れ時間t1等を計測する工程と、遅れ時間t1等に基づいて、マイコン3あるいは検査装置8によって、検査対象回路2の実装状態の良否を判定する工程と、を備える。

(もっと読む)

変圧器故障判定器

【課題】 巻線間短絡検出の精度向上を図る変圧器故障判定器を提供すること

【解決手段】 変圧器の鉄心を消磁する消磁部2と、その消磁部で鉄心が消磁された変圧器に交流電圧を印加し、その時の励磁電流に基づいて変圧器の巻線間短絡の有無を判定する故障判定部3と、故障判定部の判定結果を報知する報知部5と、を備える。消磁部は、直流電圧を一定時間印加して正の飽和状態にする初期処理機能と、その後、負の直流電圧を印加し、飽和したならば電源を遮断し、逆起電力が0になるのを待ち、当該直流電圧を印加開始から逆起電力が0になるまでの時間t1を取得する機能と、そのt1の半分の時間だけ正の直流電圧を印加し、消磁する機能を備える。

(もっと読む)

導電パターン検査装置及び検査方法

【課題】基板上に形成された複数本の導電パターンの欠陥位置を迅速かつ簡易に特定できる手段を提供する。

【解決手段】導電パターンの検査装置10は、第一電極12を介して導電パターン17に電気信号を供給する供給部20と、導電パターン17に沿って第一電極12から所定の間隔で配置された複数の第二電極14を介して、導電パターン17から供給部20によって印加された電気信号をそれぞれ検出する受容部13と、第一電極12及び第二電極14を、1本目の導電パターン17からN本目の導電パターン17へ向かって走査する操作部24と、受容部13が検出した各導電パターン17の電気信号に基づいて、断線のある導電パターン17の本数目及び当該導電パターン17上における断線の位置を判断する制御部23と、を備える。

(もっと読む)

スイッチ入力装置

【課題】使用される入力点数を抑えて、異常を検出することができるスイッチ入力装置を提供する。

【解決手段】走査制御手段12は、走査ラインCOM0〜COM7を所定順序で一つずつ選択して、選択した走査ラインに選択期間の間、走査電圧を出力すると共に、いずれの走査ラインにも走査電圧を出力しない走査オフ期間を設けて走査処理を行う。異常検知手段14は、走査ラインCOM0に走査電圧が出力されているときに入力ポートP30への入力がLowとなったとき、及び、走査オフ期間において入力ポートP30への入力がHighとなったときに、スイッチ入力装置が異常状態であると検知する。

(もっと読む)

基板のテスト方法

【課題】付加のテスト回路層を備えずに基板に内蔵された能動素子間の連結回路層の接続状態を確認し、基板に形成された回路パターンの接続状態を確認する基板のテスト方法を提供する。

【解決手段】基板に内蔵された第1能動素子1の第1接続パッドに連結された第1外部回路層11に第1テスト端子を接続し、第1能動素子の第2接続パッドに連結された第2外部回路層13に第2テスト端子を接続し、第1テスト端子を介して静電気を印加して第1能動素子1に含まれた静電放電保護回路の電圧降下を第2テスト端子で測定することで、基板に内蔵された能動素子1と外部回路層11,13の接続状態をテストする。能動素子1〜4の接続状態をテストする段階の外に、連結回路層20の接続状態をテストする段階、外部回路層11〜19、31〜36の接続状態をテストする段階、表面実装素子5,6の接続状態をテストする段階、及び基板の正常作動状態をテストする段階をさらに含む。

(もっと読む)

回路パターン検査装置

【課題】導体パターンに非接触で容量結合した電極を用いた回路パターン検査装置においては、検査対象の導電パターンの微細化が進むと共に、得られる検査信号値が小さくなり、欠陥の判定が難しくなっている。

【解決手段】回路パターン検査装置は、間隔を空けて配置された2組のセンサ対を備える検査部を移動しつつ、各導電パターンに交流信号からなる検査信号を容量結合により印加し、且つ導電パターンを伝搬した検査信号を容量結合により検出して、一度の移動による検査により各導電パターンから検査信号をそれぞれに検出し、これらの検出信号を判定基準値と比較して欠陥候補を選出し、各検査信号における導電パターンの位置を一致させて、欠陥候補どうしを比較し、同じパターン位置に共通して欠陥候補が存在する導電パターンを不良と判定する。

(もっと読む)

集積回路における外部端子の開放/短絡検査方法及び集積回路における外部端子の開放/短絡検査装置

【課題】複数の回路を有する集積回路において、一の回路に接続された外部端子間の短絡の有無を、他の回路に流れる電流の大きさ又変動の影響を抑制して判定できる、開放/短絡検出方法を提供する。

【解決手段】電源端子11は電源線36を介して直流電源4に接続される。電源端子21は電源線36から分岐した電源線37に接続される。回路10,20はそれぞれ電源端子11,21に接続される。外部端子群P20は回路20に接続され、所定の方向に配置され、外部からの制御によって電位H,Lを任意に出力可能である。検査装置3は外部端子群P20の各々に電位H,Lの何れか一方を出力させて隣り合う外部端子間の少なくとも一つに電位差を生じさせ、電源線37を流れる電流を検出し、電流の値が所定の基準値を超えたことを以って、電位差が生じている外部端子の間に短絡が生じていると判定する。

(もっと読む)

複数電源供給装置

【課題】複数の負荷回路に対して、それぞれ所望の電源電圧を供給する複数電源供給装置において、短絡を検出し、負荷回路および電源回路を保護する。

【解決手段】負荷回路に対応して設けられ、出力オンオフ信号に基づいて、所望の電圧を出力する電源回路と、複数の電源回路のうち第1の電源回路を除く電源回路に対応して設けられ、対応する電源回路に対する出力オンオフ信号がオフの場合に当該電源回路の電圧出力端において基準値以上の電圧を検出するとFAIL信号を出力する短絡検出回路と、第1の電源回路から残りの電源回路に対して、所定の時間間隔をおいて出力オンオフ信号を順次オンにするとともに、FAIL信号が出力されたことを検出すると、すべての電源回路に対する出力オンオフ信号をオフにするシーケンス回路とを備える。

(もっと読む)

電子部品の検査装置

【課題】BGAを用いた電子部品の接続箇所の検査を効率良く実施できるようにする。

【解決手段】電子部品1は、複数の接続端子を配列したBGAを用いて実装したCPU2を有する。検査装置10は、検査する接続端子の組み合わせや短絡の有無の判定基準を示すデータをCPU2に送信する。CPU2の端子設定部15と、検査装置10の端子設定部24で全ての接続端子の論理レベルをランダムに設定し、モニタ部17で短絡の有無を調べる。検査結果は、CPU2の判定部18でチェックし、その後、検査装置10の判定部22で最終的な確認を行う。

(もっと読む)

検出装置

【課題】検出回路の欠陥に起因した検出精度の低下を抑制する。

【解決手段】複数の検出回路Uの各々は、被検出物の有無に応じた検出信号Sを生成する。駆動回路20は、複数の検出回路から検出信号Sを取得する。欠陥判定部38は、複数の検出回路Uの各々における欠陥の有無を当該検出回路Uの検出信号Sに応じて判定する。駆動回路20は、複数の検出回路Uに含まれる複数の第1検出回路U1および複数の第2検出回路U2のうち欠陥の総数が少ない方から検出信号Sを取得する。

(もっと読む)

電子部品の検査装置

【課題】BGAを用いた電子部品の接続箇所の検査を効率良く実施できるようにする。

【解決手段】電子部品1は、複数の接続端子を配列したBGAを用いて実装したCPU2を有する。CPU2の接続端子の検査は、全ての接続端子を複数のグループに分けて検査する。端子選択部23は、各グループから検査対象となる接続端子をターゲット端子として1つずつ選択する。モニタ部25で、各ターゲット端子と他の接続端子との短絡を各グループにおいて同時に検査する。各グループ内の全ての接続端子をターゲット端子に選択して検査を行ったら、処理を終了する。

(もっと読む)

基板検査方法

【課題】検査精度を低下させることなく、検査時間を短縮して検査効率の向上が図れる基板検査方法を提供する。

【解決手段】順番に実行される各単位検査工程1〜4では、互いに異なるいずれか1つの配線パターンA〜Dを正極側、他の配線パターンA〜Dを負極側に設定し、その正負の配線パターンA〜D間に電位差を付与して配線パターンと出力部との間に流れる電流値に基づいて正負の配線パターンA〜D間の電気的特性を検査する。各単位検査工程1〜4において、負極側の配線パターンA〜Dのうちの未だ正極側に設定されたことのない配線パターンA〜Dに関する電流検出を第1特性検出部により行い、既に正極側に設定されたことのある配線パターンA〜Dに関する電流検出を第2特性検出部により行う。第2特性検出部による電流検出は、第1特性検出部による電流検出よりも早いタイミングで行う。

(もっと読む)

ネットワーク状態の監視方法および装置

本発明は、第1相、第2相および第3相を有する三相交流電圧ネットワークの電気的諸量の検出方法であって、次のステップ、すなわち、第1時点に、第1相、第2相および第3相の中性導体に関するそれぞれの電圧値を測定するステップと、第1時点の3つの電圧値を、電圧振幅および位相角を有する極座標に変換するステップと、少なくとも1つの別の時点に対して測定および変換を繰り返すステップと、極座標に変換された電圧値から少なくとも1つの相の現時点の周波数、電圧振幅および/または位相角を決定するステップと、を含む方法に関する。  (もっと読む)

(もっと読む)

回転子検査装置及び回転子検査方法

【課題】回転子の良否を判定するだけでなく、回転子が不良品である場合の不良原因及び不良箇所を特定するすることが可能な回転子検査装置及び回転子検査方法を提供する。

【解決手段】回転子検査装置1は、回転子2に設けられた複数のセグメントのうちの二つのセグメント間に印加する周波数可変な交流信号を出力する周波数可変発振器11と、交流信号が印加された二つのセグメント間の電圧または電流を測定する計測部13と、交流信号の周波数を変更しつつ測定された二つのセグメント間の電圧または電流から少なくとも一つの特性値を算出する特性値算出部32と、少なくとも一つの特性値が予め求められた回転子の不良品に対応する少なくとも一つの不良品条件の何れかを満たす場合、回転子は不良品であり、かつ、回転子の不良原因及び不良箇所を、その不良品条件に関連付けられた不良原因及び不良箇所として特定する判定部33とを有する。

(もっと読む)

プリント配線板の検査装置及び検査方法

【課題】プリント配線板の断線検査及び短絡検査を容易かつ安価に検査することができるプリント配線板の検査技術を提供する。

【解決手段】検査対象のプリント配線板の基準面に第1のプローブを接触させ、前記プリント配線板のネットに第2のプローブを接触させ、前記第2のプローブを介して前記ネットに矩形パルス電圧を印加し、前記第1のプローブで、矩形パルス印加直後の第1の電圧測定と、絶縁抵抗を判別するため設定された最適測定時間に第2の電圧測定を行い、前記プリント配線板のすべてのネットについて前記電圧測定を行い、予め測定した良品の第1の測定値および第2の測定値と、前記測定した第1の測定値および第2の測定値とを比較し、第1の測定値で同一ネット内の完全断線を含む導通抵抗の増加不良の検出を行い、第2の測定値で近接するネットとの完全短絡を含む絶縁抵抗の減少不良の検出を行う。

(もっと読む)

基板検査装置

【課題】今回検査点の位置情報を検査済みの検査点との関係で検知しながら確実、迅速にプロービングできる基板検査装置の提供。

【解決手段】平面位置決め装置15にプロービング装置16とをプロービング情報検出手段17とを搭載させ、かつ、記憶装置13が備える中央処理手段12に接続させ、各検査点との関係でプロービングのX−Y方向が位置決めされるプロービング装置16は、今回検査点が被検査基板の基準水平面との関係で一定の条件を満たせばこれに接触させ、満たさなければプロービング情報検出手段17で今回検査点についてのZ方向位置情報を検出してから接触させ、次順の検査点の位置が一定の条件を満たせば今回検査スタート時のZ位置へとコンタクトプローブを移動させ、満たさなければ予め設定されている離間位置へとコンタクトプローブを移動させるようにした。

(もっと読む)

電気的試験システム及び電気的試験方法

【課題】短絡確認検査及びコンデンサ逆実装確認検査を効率的に実施可能な電気的試験システム及び電気的試験方法を提供すること。

【解決手段】電気的試験システムは、電気的試験装置と、電気的試験装置によって試験される電子装置と、を備える。電子装置は、グループ毎に分けられた複数の電子素子と、各グループに少なくとも1つ配され、電源配線及びグランド配線のうち少なくともいずれかと電子素子との電気的接続を開閉するスイッチと、を有する。複数の電子素子のうち少なくとも1つは有極性コンデンサである。電気的試験装置は、スイッチの開閉を制御するスイッチ制御回路と、グループにおける電源配線とグランド配線間のショートの有無を検出するショート検出回路と、有極性コンデンサの実装方向を検出する逆実装検出回路と、電源配線とグランド配線に電力供給する電源回路と、を有する。

(もっと読む)

電気光学装置および電子機器

【課題】電気光学装置の検査に必要な回路の規模を縮小する。

【解決手段】複数の画素回路PXは、M本の走査線22とN本の信号線24との各交差に対応して配置され、走査線22の選択時に信号線24に供給される階調信号X[n]に応じた階調に制御される。走査線駆動回路32は、各走査線22の選択/非選択を指示する走査信号Y[1]〜Y[M]を各走査線22に出力する。検査回路44は、信号線24毎に配置されたN個のスイッチQを含む。N個のスイッチQは、K本の検査線52[1]〜52[K]に対応するK個毎に複数のブロックBに区分される。ブロックB内の各スイッチQ[k]は、検査線52[k}と信号線24との間に介在し、N個のスイッチQは、ブロックB毎に相異なる走査信号Y[m]に応じてオン状態またはオフ状態に制御される。

(もっと読む)

121 - 140 / 525

[ Back to top ]