Fターム[2H092JA44]の内容

液晶−電極、アクティブマトリックス (131,435) | 能動素子 (19,865) | 三端子素子 (19,408) | 構造 (10,751) | ソース、ドレイン電極 (2,019) | 層構造 (472)

Fターム[2H092JA44]に分類される特許

41 - 60 / 472

半導体装置の作製方法

【課題】安定した電気特性を有する薄膜トランジスタを有する、信頼性のよい半導体装置

を提供することを課題の一とする。また、高信頼性の半導体装置を低コストで生産性よく

作製することを課題の一とする。

【解決手段】チャネル形成領域を含む半導体層、ソース領域及びドレイン領域を酸化物半

導体層とする薄膜トランジスタを有する半導体装置の作製方法において、酸化物半導体層

の純度を高め、不純物である水分などを低減する加熱処理(脱水化または脱水素化のため

の加熱処理)を行う。

(もっと読む)

配線構造、表示装置、および半導体装置

【課題】Cu合金層と半導体層との間に通常設けられるバリアメタル層を省略しても優れた低接触抵抗を発揮し得、さらに半導体層との密着性に優れており、且つ電気抵抗率が低減された配線構造を提供すること。

【解決手段】本発明の配線構造は、基板の上に、基板側から順に、半導体層と、Cu合金層とを備えた配線構造であって、前記Cu合金層は、基板側から順に、合金成分としてMnと、X(Xは、Ag、Au、C、W、Ca、Mg、Al、SnおよびNiよりなる群から選択される少なくとも一種)を含有する第一層と、純Cu、またはCuを主成分とするCu合金であって前記第一層よりも電気抵抗率の低いCu合金からなる第二層、とを含む積層構造である。

(もっと読む)

電気光学装置の製造方法、電気光学装置、投射型表示装置および電子機器

【課題】絶縁膜の穴内に設けたプラグ電極によって導電層同士の導通を行うにあたって、研磨時間やプラグ電極形成用導電膜の成膜時間を短縮することのできる電気光学装置の製造方法、電気光学装置、投射型表示装置、および電子機器を提供すること。

【解決手段】液晶装置の素子基板において、第2電極層7aと画素電極9aとを層間絶縁膜48の穴48a内に設けたプラグ電極8aを介して電気的に接続するにあたって、第1絶縁膜46に設けたコンタクトホール46aを埋めるようにプラグ電極8aを形成した後、第2絶縁膜47を成膜する。そして、第2絶縁膜47を表面側から研磨してプラグ電極8aを露出させた後、第2絶縁膜47の表面側に画素電極9aを形成する。

(もっと読む)

薄膜トランジスタおよび反射型カラー表示装置

【課題】薄膜トランジスタ(背面基板)とカラーフィルタの画素とを位置合わせを、より容易にする。

【解決手段】実質的に透明な第1の基板1と、上記第1の基板1上に設けられた実質的に透明なゲート電極2と、上記ゲート電極と同一層に離間して設けられた実質的に透明なキャパシタ電極3と、上記ゲート電極および上記キャパシタ電極を覆うように設けられた実質的に透明なゲート絶縁膜4と、上記ゲート絶縁膜上に設けられた半導体層5と、上記半導体層と接続した実質的に透明なソース電極6と、上記半導体層に接続すると共に上記ソース電極と離間して形成された実質的に透明なドレイン電極7と、少なくとも上記ドレイン電極上を覆うように形成された着色層11と、を備える。

(もっと読む)

電気光学装置、投射型表示装置および電子機器

【課題】狭い領域内に高い容量値をもった蓄積容量を構成することができる電気光学装置、該電気光学装置を備えた投射型表示装置、および電子機器を提供すること。

【解決手段】液晶装置100においては、複数層の層間絶縁膜41〜45のうち、層間絶縁膜42に溝状凹部42eが設けられ、かかる溝状凹部42eの底壁42e1および側壁42e2に沿って形成された第1電極層5a、誘電体層40、および第2電極層7aにより蓄積容量55が構成されている。また、層間絶縁膜42には層間絶縁膜43が積層され、層間絶縁膜43において溝状凹部42eが反映されてなる凹部43eの内部で、第1電極層5a、誘電体層40、および第2電極層7aが蓄積容量55を構成している。

(もっと読む)

半導体装置

【課題】大面積化しても低消費電力を実現した半導体装置の構造およびその作製方法を提供する。

【解決手段】画面で使われる画素の薄膜トランジスタを作製する。その薄膜トランジスタにおいて、ソース配線、ゲート電極を同一平面上に作製する。また、ソース配線と薄膜トランジスタをつなぐ配線と、画素電極と薄膜トランジスタをつなぐ配線を同一工程で作製する。

(もっと読む)

電気光学装置、投射型表示装置、および電気光学装置の製造方法

【課題】絶縁膜を間に挟む導電層同士の導通部分の構造を改良することにより、導電層のレイアウト面での自由度を高めることのできる電気光学装置、投射型表示装置、および電気光学装置の製造方法を提供すること。

【解決手段】液晶装置100において、ドレイン電極6bと画素電極9aとの間には第3層間絶縁膜44が形成されており、第3層間絶縁膜44のコンタクトホール7dの底部7d0でドレイン電極6bと画素電極9aの第1方向Yの一方側Y1の端部9a0とが導通している。画素電極9aの端部9a0において、第1方向Yの一方側Y1に位置する先端縁9a1は、コンタクトホール7dの開口縁のうち、第1方向Yの一方側Y1に位置する開口縁部分7dyより、第1方向Yの一方側Y1とは反対側の他方側Y2に位置しており、コンタクトホール7dより一方側Y1に張り出していない。

(もっと読む)

液晶表示装置

【課題】応答速度の高速化が可能であるとともに透過率の低減を抑制しつつ高精細化が可能な液晶表示装置を提供する。

【解決手段】ポリシリコン半導体層を備えたスイッチング素子と、第1電極と、前記第1電極と向かい合うとともに前記スイッチング素子と電気的に接続され且つ第1方向に沿って複数のV字型スリットが並んで形成された第2電極と、第1配向膜と、を備えた第1基板と、第2配向膜を備えた第2基板と、前記第1基板と前記第2基板との間に保持された液晶層と、を備え、前記V字型スリットは、第1中央部、前記第1中央部の一端側に繋がった第1端部、前記第1中央部の他端側に繋がった第2端部、第2中央部、前記第2中央部の一端側に繋がった第3端部、及び、前記第2中央部の他端側に繋がった第4端部を有し、前記第1端部と前記第3端部とが繋がったことを特徴とする液晶表示装置。

(もっと読む)

電気光学装置の製造方法

【課題】遮光層の遮光性能を低下させずに、素子基板に対する加熱処理を行うことのできる電気光学装置の製造方法を提供すること。

【解決手段】液晶装置の製造工程において、素子基板用の基板本体10wの一方面10sに走査線3a(遮光層)、絶縁膜12を形成した後、半導体層1aを形成する半導体層形成工程、および半導体層1aに導入した不純物を拡散させる不純物拡散工程では、レーザーアニール装置やランプアニール装置等の加熱装置920によって、一方面10s側を他方面10t側より温度を高くした状態で加熱する。このため、走査線3aは高い温度に加熱されないので、走査線3aに用いたアルミニウム膜やタングステンシリサイド膜に溶融や再結晶化等が発生しない。

(もっと読む)

薄膜トランジスタの製造方法、薄膜トランジスタ、表示装置、センサ及びX線デジタル撮影装置

【課題】基板の選択性を広げつつ、電界効果移動度が高くノーマリーオフ駆動する薄膜トランジスタ等を得る。

【解決手段】活性層の成膜工程での成膜室中の雰囲気の全圧に対する酸素分圧をPo2depo(%)とし、熱処理工程中の雰囲気の全圧に対する酸素分圧をPo2anneal(%)としたときに、熱処理工程時の酸素分圧Po2anneal(%)が、−20/3Po2depo+40/3≦Po2anneal≦−800/43Po2depo+5900/43の関係を満たすように成膜工程と熱処理工程とを行う。

(もっと読む)

液晶装置、液晶装置の製造方法、および投射型表示装置

【課題】無機配向膜が基板間導通用電極部の表面を覆っている場合でも、簡素な構成で、基板間導通用電極部と導電粒子とを導通させることのできる液晶装置、液晶装置の製造方法、および当該液晶装置をライトバルブとして用いた投射型表示装置を提供すること。

【解決手段】液晶装置100において、素子基板10および対向基板20からなる一対の基板のうち、対向基板20では、配向膜26が基板間導通用電極部25tの表面を覆う無機配向膜である。但し、基板間導通用電極部25tが導電粒子209bより低硬度のアルミニウム合金膜により形成されていることから、導電粒子109bが配向膜26を突き破って基板間導通用電極部25tに食い込み、基板間導通用電極部25tと導通している。このため、対向基板20では、全面に配向膜26を形成することができ、マスク蒸着を行う必要がない。

(もっと読む)

表示装置及び表示装置の製造方法

【課題】オン電流を確保しつつ、オフ電流を低減した薄膜トランジスタを有する表示装置を提供することを目的とする。

【解決手段】ゲート電極GTと、ゲート電極GTの上側に形成される結晶化された第1の半導体層MSと、第1の半導体層MSの上側に形成される、ソース電極STおよびドレイン電極DTと、第1の半導体層MSの側方から延伸して、ソース電極ST及びドレイン電極DTのうちの一方と第1の半導体層MSとの間に介在する第2の半導体層SLと、を有する表示装置であって、第2の半導体層SLは、第1の半導体層MSと接触して結晶化されて形成される第1部分SLaと、第1部分SLaよりも結晶性が低い第2部分SLbを有する、ことを特徴とする表示装置。

(もっと読む)

半導体装置の作製方法

【課題】オフ電流が小さく、好ましくはオン電流及び移動度も高く、工程が簡略化された半導体装置の作製方法を提供する。

【解決手段】チャネルエッチ型の薄膜トランジスタの作製に際して、ゲート絶縁層上に少なくとも半導体層を形成し、半導体層上に導電膜を形成し、導電膜上にエッチングマスクを形成し、基板を反応室内に搬入し、導電膜を加工してソース電極及びドレイン電極層を形成し、反応室内に半導体エッチング用のガスを導入し、反応室内で半導体エッチング用のガスでエッチングを行い、基板を反応室から搬出し、その後エッチングマスクを除去する。すなわち、導電膜の加工から半導体エッチング用のガスで行うエッチングまでを同一チャンバー内で連続して行い、半導体エッチング用のガスで行うエッチングはエッチングマスクを除去する前に行う。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体層の側面からの酸素の脱離を防ぎ、酸化物半導体層中の欠陥(酸素欠損)が十分に少なく、ソースとドレインの間のリーク電流が抑制された半導体装置を提供する。

【解決手段】酸化物半導体膜に対して第1の加熱処理を施した後に該酸化物半導体膜を加工して酸化物半導体層を形成し、その直後に該酸化物半導体層の側壁を絶縁性酸化物で覆い、第2の加熱処理を施すことで、酸化物半導体層の側面が真空に曝されることを防ぎ、酸化物半導体層中の欠陥(酸素欠損)を少なくして半導体装置を作製する。酸化物半導体層の側壁はサイドウォール絶縁層により覆われている。なお、該半導体装置はTGBC(Top Gate Bottom Contact)構造とする。

(もっと読む)

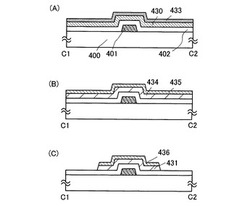

半導体装置、モジュール及び電子機器

【課題】本発明は、アクティブマトリクス型の表示装置において、配線の断面積を増大させることなく、相性の悪い2つの膜(ITO膜とアルミニウム膜)からなる配線や電極等を接続し、且つ、大画面化しても低消費電力を実現することを課題とする。

【解決手段】本発明は、上層と、上層よりも広い幅を有する下層とからなる2層構造とする。TiまたはMoからなる第1導電層を設け、その上に電気抵抗値の低いアルミニウム単体(純アルミニウム)からなる第2導電層を設ける。上層の端面から突出させた下層部分と、ITOとを接合させる。

(もっと読む)

液晶表示装置

【課題】コントラスト比と広視野角を同時に確保することができ、液晶分子の応答速度を速くすることができるだけでなく、優れた表示特性を示す液晶表示装置を提供する。

【解決手段】本発明の実施形態にかかる液晶表示装置は、互いに対向する第1基板および第2基板と、第1および第2基板の間に介在しており、液晶分子を含む液晶層と、第1基板の上に配置されており、互いに分離されている第1画素電極および第2画素電極とを含み、第1画素電極および第2画素電極の1つは、データ線を介して第1電圧が印加され、第1画素電極および第2画素電極の残りの1つは、電圧伝達線を介して第2電圧が印加され、第1画素電極および第2画素電極は、幹部と、幹部から延びた複数の枝電極とを含み、第1画素電極の枝電極と第2画素電極の枝電極は交互に配置されており、第1画素電極および第2画素電極の幹部は、電圧伝達線と少なくとも一部重畳する。

(もっと読む)

電気光学装置及び電子機器

【課題】電気光学装置において、積層構造の単純化を図り、しかも高品質な表示を可能とする。

【解決手段】電気光学装置は、基板上に、データ線(6)に接続された第1ソースドレイン領域、及び画素電極(9)に接続された第2ソースドレイン領域を含んでなる半導体層(30a)と、半導体層と画素電極との間に配置され、一の走査線(11)に接続されたゲート電極(30b)とを有するトランジスター(30)と、一の走査線に隣り合う走査線に接続された第2トランジスターのゲート電極が延在してなる第1容量電極と、第1容量電極と画素電極との間に設けられるとともに第2ソースドレイン領域に接続された第2容量電極とを有する蓄積容量(70)とを備える。蓄積容量は、半導体層とゲート電極との間の絶縁膜及び半導体層と基板との間の絶縁膜を貫通するとともに基板に設けられた溝内の少なくとも一部に設けられている。

(もっと読む)

タッチセンシング基板及びそれの製造方法

【課題】タッチセンシング基板及びその製造方法を提供する。

【解決手段】第1光センシング素子は、ベース基板上に配置され、第1の光によって動作し、第1ゲート電極、第1ゲート電極と重なる第1アクティブパターン、第1アクティブパターンと部分的に重なる第1ソース電極、及び第1ドレーン電極を含む。第2光センシング素子は、ベース基板上に配置され、第2の光により動作し、第2ゲート電極、第2ゲート電極と重なる第1アクティブパターンと異なった物質を含む第2アクティブパターン、第2アクティブパターンと部分的に重なる第2ソース電極、及び第2ドレーン電極を含む。第1バイアス配線は、第1及び第2ゲート電極から延長されて第1及び第2ゲート電極と接続される。ソース及びドレーン電極がソース及びドレーン接続電極によりコンタクトホールを通じて接続されることによって、ソース及びドレーン電極のショート不良を防止することができる。

(もっと読む)

電気光学装置及び電子機器

【課題】電気光学装置において、積層構造の単純化を図り、しかも高品質な表示を可能とする。

【解決手段】電気光学装置は、基板(10)上に、互いに交差するデータ線(6)及び複数の走査線(11)と、データ線に電気的に接続された第1ソースドレイン領域、及び第2ソースドレイン領域を含んでなる半導体層(30a)と、複数の走査線のうち一の走査線に電気的に接続されたゲート電極とを有するトランジスター(30a)と、半導体層と基板との間に配置され、第2ソースドレイン領域に電気的に接続された第1容量電極(71)と、第1容量電極に対向するように設けられるとともに一の走査線に隣り合う走査線に電気的に接続された第2容量電極(73)とを有する蓄積容量(70)と、を備え、蓄積容量は、基板上に設けられた溝の内部の少なくとも一部に設けられている。

(もっと読む)

電気光学装置及び電子機器

【課題】液晶装置等の電気光学装置において、サンプリング用トランジスターの高速化とプッシュダウン現象の抑制を両立させ、高品位な表示を行う。

【解決手段】電気光学装置は、データ線(6)に画像信号線(60)から供給される画像信号をサンプリングするサンプリング用トランジスター(71)を備える。サンプリング用トランジスターのゲート絶縁膜(73)は、ゲート電極(71G)の第1ソースドレイン領域(74S)側の縁部(71Ges)に重なる部分及びゲート電極の第2ソースドレイン領域(74D)側の縁部(71Ged)に重なる部分の各々の膜厚が、ゲート電極の中央部(71Gc)に重なる部分の膜厚よりも厚くなるように形成されている。

(もっと読む)

41 - 60 / 472

[ Back to top ]