Fターム[4M104AA03]の内容

Fターム[4M104AA03]の下位に属するFターム

Fターム[4M104AA03]に分類される特許

241 - 260 / 1,500

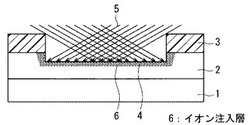

炭化珪素半導体装置の製造方法

【課題】本発明は、製造プロセスが煩雑でなく、かつ高い絶縁耐力を有する炭化珪素半導体装置の製造方法の提供を目的とする。

【解決手段】本発明の炭化珪素半導体装置の製造方法は、(a)第1導電型の炭化珪素半導体よりなる下地であるSiC基板1を準備する工程と、(b)SiC基板1上において、素子領域を囲むリセス構造4を、レジストパターン3を用いて形成する工程と、(c)工程(b)の後、レジストパターン3を介した不純物注入により、リセス構造4内のリセス底面及びリセス側面の面内に、第2導電型の不純物層としてのイオン注入層6を形成する工程とを備え、工程(c)は、斜め回転イオン注入により不純物注入を行う工程である。

(もっと読む)

半導体装置およびその作製方法

【課題】従来のDRAMは、データを保持するために数十ミリ秒間隔でリフレッシュをしなければならず、消費電力の増大を招いていた。また、頻繁にトランジスタのオン状態とオフ状態が切り換わるのでトランジスタの劣化が問題となっていた。この問題は、メモリ容量が増大し、トランジスタの微細化が進むにつれて顕著なものとなっていた。

【解決手段】酸化物半導体を有するトランジスタを用い、ゲート電極用のトレンチと、素子分離用のトレンチを有するトレンチ構造のトランジスタとする。ソース電極とドレイン電極との距離を狭くしてもゲート電極用のトレンチの深さを適宜設定することで、短チャネル効果の発現を抑制することができる。

(もっと読む)

半導体装置およびその作製方法

【課題】電気特性の変動が生じにくく、且つ電気特性の良好な半導体装置、およびその作製方法を提供することである。

【解決手段】基板上に下地絶縁膜を形成し、下地絶縁膜上に第1の酸化物半導体膜を形成し、第1の酸化物半導体膜を形成した後、第1の加熱処理を行って第2の酸化物半導体膜を形成した後、選択的にエッチングして、第3の酸化物半導体膜を形成し、第1の絶縁膜および第3の酸化物半導体膜上に絶縁膜を形成し、第3の酸化物半導体膜の表面が露出するように絶縁膜の表面を研磨して、少なくとも第3の酸化物半導体膜の側面に接するサイドウォール絶縁膜を形成した後、サイドウォール絶縁膜および第3の酸化物半導体膜上にソース電極およびドレイン電極を形成し、ゲート絶縁膜およびゲート電極を形成する。

(もっと読む)

半導体装置の製造方法

【課題】シリコン膜のエッチング時に膜厚方向中央部での括れの発生を防止する。

【解決手段】多結晶シリコン膜3の上部と下部はノンドープ層3a、3cにてそれぞれ構成され、多結晶シリコン膜3の中央部は不純物ドープ層3bにて構成され、多結晶シリコン膜3に凹部M1を形成した後、多結晶シリコン膜3の酸化処理にて凹部M1の表面にシリコン酸化膜6を形成し、凹部M1下の多結晶シリコン膜3を除去する。

(もっと読む)

配線又は電極の形成方法、電子デバイス及びその製造方法

【課題】下地にダメージを与えず、また、電極材料のゴミの再付着も防止される配線又は電極の形成方法と、この配線又は電極の形成方法により配線又は電極を形成する電子デバイス及びその製造方法を提供する。

【解決手段】下地2上に第1のレジスト層1を形成し、開口部5を形成し、導電材料層3を成膜する。導電材料層3の全体を覆う第2のレジスト層4を形成し、該開口部5以外の導電材料層3上の第2のレジスト層4を除去することにより、該開口部5の導電材料層3を覆う保護レジスト層4’を形成する。該保護レジスト層4’で覆われていない導電材料層3を除去し、次いで保護レジスト層1,4’を除去することにより、残留した導電材料3よりなる配線又は電極を形成する。

(もっと読む)

半導体装置

【課題】半導体装置の寄生容量成分を好適に調整する。

【解決手段】半導体装置10は、複数個のエミッタ領域20を備える。半導体層の表面から所定の深さまでの領域に形成されているボディ領域12を備える。ボディ領域12の下部に形成されているドリフト領域4を備える。ドリフト領域4の下部に形成されているコレクタ領域3を備える。各エミッタ領域20の表面からボディ領域12を貫通して伸びている第1トレンチ31を備える。第1トレンチ31の内面を覆っているゲート絶縁膜18を備える。第1トレンチ31内に収容されているゲート電極8を備える。隣接している第1トレンチ31間に形成され、ボディ領域12を貫通して伸びている第2トレンチ32を備える。第2トレンチ32の内面を覆っているトレンチ絶縁膜33を備える。第2トレンチ32内に収容されている導電層35を備える。導電層35がゲート電極8に電気的に接続されている。

(もっと読む)

半導体装置とその製造方法

【課題】配線加工時のエッチングレートの極端な上昇を抑え、プロセスを安定化させる。

【解決手段】炭化珪素基板1上に形成された炭化珪素層20の上に、ソース電極8、ゲート電極9、層間絶縁膜10、層間絶縁膜10上に形成されたソース電極上部配線11およびゲート電極上部配線12とが形成され、ソース電極上部配線11とゲート電極上部配線12の下には、これらの上部配線を構成する金属が炭化珪素層20に拡散することを抑制するためのバリアメタル16が形成されている。層間絶縁膜10には、炭化珪素層20上に形成されたソース電極8およびゲート電極9に到達するようにコンタクトホール13、15が形成されており、バリアメタル16はコンタクトホール内の電極と上部配線との界面、層間絶縁膜10の側壁と上部配線との界面、および側壁の上端部近傍と上部配線との界面にのみ形成されている。

(もっと読む)

薄膜トランジスタ用ゲート絶縁膜および該絶縁膜を備えた薄膜トランジスタ素子

【課題】低温条件下かつ溶液塗布プロセスにより形成可能であり、薄膜トランジスタにおける電気特性であるヒステリシス、On/Off比が良好な薄膜トランジスタ用ゲート絶縁膜及び該絶縁膜を備えた薄膜トランジスタを提供する。

【解決手段】必須成分として(A)アルケニル基を有する化合物、(B)SiH基を有する化合物、(C)ヒドロシリル化触媒を含有する硬化性組成物を低温条件下によるポストベイクしたゲート絶縁膜を用いることにより、良好なトランジスタ特性が発現する。

(もっと読む)

レーザアニール方法及びレーザアニール装置

【課題】高エネルギ効率でレーザアニールを行う方法及び装置を提供する。

【解決手段】(a)不純物がイオン注入により添加されたSiC基板を準備する。(b)SiC基板に、炭酸ガス(CO2)レーザ発振器から出射された反射率の低い9μm〜10.3μmの範囲内のいずれかの波長のレーザビームを照射して、SiC基板に添加された不純物を活性化させる。

(もっと読む)

炭化珪素半導体装置およびその製造方法

【課題】炭化珪素半導体層に設けられたリセス底部の不純物領域を含む終端構造の形成において、リセスの底端部に発生したノッチを除去あるいは緩やかな形状にする。

【解決手段】ガードリング6の形成領域のSiCドリフト層2にリセス7を形成したとき、リセス7の底端部に尖ったノッチ11が現れる。リセス7の形成後、リセス7の内部を含むSiCドリフト層2の表面を熱酸化して酸化層12を形成し、当該酸化層12をエッチングにより除去すると、ノッチ11は緩やかな形状になる。

(もっと読む)

電力用半導体装置

【課題】JBSであってもサージ電流による温度上昇とその正帰還により素子破壊に至る場合があった。

【解決手段】n型のSiC基板と、SiC基板の第一主面に形成され、SiC基板よりも不純物濃度の低いn型SiCドリフト層と、ドリフト層に形成されたp型SiCの第一の半導体領域と、第一の半導体領域の表層側に形成され、第一の半導体領域よりも不純物濃度が高濃度であるp型SiCの第二の半導体領域と、ドリフト層の表面に形成され第一の半導体領域とショットキー接続し、第二の半導体領域とオーミック接続するショットキー電極と、ショットキー電極の表面に形成されたアノード電極と、アノード電極の表面で、第一の半導体領域の直上に形成され、上面から見て第一の半導体領域の領域を含むように第一の半導体領域よりも広い面積に形成されたファーストボンドと、SiC基板の第二主面に形成されたカソード電極とを備えている。

(もっと読む)

薄膜トランジスタ、アクティブマトリクス基板、およびそれらの製造方法

【課題】材料の選択幅が広く、生産性が高いTFT、アクティブマトリクス基板、およびそれらの製造方法を提供すること。

【解決手段】本発明にかかる薄膜トランジスタは、ゲート電極2と、半導体層5と、半導体層5の上に設けられ、半導体層5と電気的に接続されたソース電極7、及びドレイン電極8と、を備えた薄膜トランジスタであって、半導体層5が、透光性半導体膜5aと、透光性半導体膜5a上に配置され、透光性半導体膜5aよりも光透過率の低いオーミック導電膜5bと、を有し、オーミック導電膜5bが、透光性半導体膜5aからはみ出さないように形成され、オーミック導電膜5bが、ソース電極7とドレイン電極8の間のチャネル部9を挟むように分離して形成され、ソース電極7、及びドレイン電極8が、オーミック導電膜bを介して、透光性半導体膜5aに接続されているものである。

(もっと読む)

電力用半導体装置

【課題】高温動作において配線の金属材料と半導体領域に接続する電極との反応が生じにくく、かつ、高温動作において歪みが生じにくい電力用半導体装置を実現する。

【解決手段】第1金属層14は、ゲート電極9とソース電極11との上に形成され、かつ、Pt,Ti,Mo,W,Taのうち少なくとも1種を含んでいる。第2金属層15は、第1金属層14上に形成され、かつ、Mo,W,Cuのうち少なくとも1種を含んでいる。層間絶縁膜10は、p型SiC領域13およびゲート絶縁膜8またはゲート電極9の表面上であってソース電極11が形成された領域以外の領域において形成されている。第1金属層14および第2金属層15は、層間絶縁膜10上に延在している。

(もっと読む)

半導体装置

【課題】半導体装置の高集積化を図り、単位面積あたりの記憶容量を増加させる。

【解決手段】半導体装置は、半導体基板に設けられた第1のトランジスタと、第1のトランジスタ上に設けられた第2のトランジスタとを有する。また、第2のトランジスタの半導体層は、半導体層の上側で配線と接し、下側で第1のトランジスタのゲート電極と接する。このような構造とすることにより、配線及び第1のトランジスタのゲート電極を、第2のトランジスタのソース電極及びドレイン電極として機能させることができる。これにより、半導体装置の占有面積を低減することができる。

(もっと読む)

半導体装置の作製方法、及び半導体装置

【課題】簡単な工程でニッケル含有シリサイドを形成する。

【解決手段】シリコン基板を用いた場合であって、ゲート絶縁膜、ゲート電極、ゲート電極側面のサイドウォールを形成し、不純物イオンをドープしてソース領域及びドレイン領域を形成し、表面酸化膜を除去し、シリコン基板を450℃以上に加熱しながら、ニッケル含有膜を10nm〜100nmの膜厚で形成することにより、ソース領域、ドレイン領域、及びゲート電極上にニッケル含有シリサイドを形成することができる。その後、未反応のニッケルを除去する。

(もっと読む)

チャネルエッチ型薄膜トランジスタとその製造方法

【課題】半導体層の膜厚均一性を向上させたチャネルエッチ型TFTとその製造方法を提供する。

【解決手段】酸化物半導体からなるチャネル層4を形成した後、該チャネル層4の上にIn、Zn、Gaを含む酸化物からなり、上記酸化物半導体よりもエッチングレートが速く、抵抗率が3.38×107Ωcm以下である犠牲層5を形成し、その上にソース電極6及びドレイン電極7を形成して、該ソース電極6とドレイン電極7の間に露出した犠牲層5をウェットエッチング除去することにより、半導体層膜厚の均一性を向上させ、TFT特性とその均一性と、をより向上させることができる。

(もっと読む)

半導体装置

【課題】本発明は、高電界での耐圧を確保でき、かつ絶縁破壊を抑制できる終端構造を有する半導体装置の提供を目的とする。

【解決手段】本発明にかかる半導体装置は、ドリフト領域2表面において、平面視でSBD電極5を囲むように形成された、リセス構造3と、リセス構造3底面内に形成され、SBD電極5と接続された、ガードリング注入層4と、リセス構造3に沿って、少なくともリセス構造3を覆って形成された、保護膜7と、保護膜7に沿って、保護膜7上に形成された、半絶縁膜20とを備え、半絶縁膜20は、リセス構造3が囲む領域の内側においてSBD電極5と接続される接続部21と、リセス構造3が囲む領域の外側においてドリフト領域2と接続される接続部22とを備える。

(もっと読む)

半導体装置の製造方法

【課題】炭化珪素の半導体層の表面に発生するステップバンチングを抑制する。

【解決手段】半導体装置の製造方法は、炭化珪素のエピタキシャル層14にドーパントを導入するドーパント導入工程と、PLD、FCVA法又はECRスパッタ法を利用してエピタキシャル層14の表面にカーボン膜24を形成するカーボン膜形成工程と、カーボン膜24が残存した状態でエピタキシャル層14をアニール処理するアニール処理工程とを備える。

(もっと読む)

炭化ケイ素金属半導体電界効果トランジスタ及び炭化ケイ素の金属半導体電界効果トランジスタを製造する方法

【課題】深いレベルのドーパントがほとんど存在しない半絶縁性のSiC基板上にMESFETを形成することにより、バックゲート効果が減少された、SiCのMESFETを提供する。

【解決手段】半絶縁性の基板上10に選択的にドープされたP型の炭化珪素の層13、及びN型のエピタキシャル層14を積層し、背面ゲート効果を減少させる。また2つの凹部を有するゲート構造体も備える。これにより、出力コンダクタンスを1/3に減少することができ、また電力のゲインを3db増加することができる。クロム42をショットキーゲート接点として利用することもでき、酸化物−窒化物−酸化物(ONO)の保護層60を利用して、MESFET内の表面効果を減少させる。また、ソース及びドレインのオーム接点をn型チャネル層上に直接形成して、これにより、n+領域を製造する必要がなくなる。

(もっと読む)

炭化珪素半導体装置の製造方法

【課題】Al原子を有するコンタクト電極が用いられる場合に、絶縁膜の絶縁信頼性を向上させることができる炭化珪素半導体装置の製造方法を提供する。

【解決手段】基板面12Bを有する炭化珪素基板10が準備される。基板面12Bの一部を覆うように絶縁膜15が形成される。絶縁膜15に接触するように基板面上にコンタクト電極16が形成される。コンタクト電極16はAl、TiおよびSi原子を含有する。コンタクト電極16は、Si原子およびTi原子の少なくともいずれかと、Al原子とを含有する合金から作られた合金膜50を含む。炭化珪素基板10とコンタクト電極16とがオーミックに接続されるようにコンタクト電極16がアニールされる。

(もっと読む)

241 - 260 / 1,500

[ Back to top ]