Fターム[4M104BB28]の内容

半導体の電極 (138,591) | 電極材料 (41,517) | 遷移金属のシリサイド (5,826) | 高融点金属のシリサイド (2,215) | WSi (591)

Fターム[4M104BB28]に分類される特許

141 - 160 / 591

半導体素子の製造方法

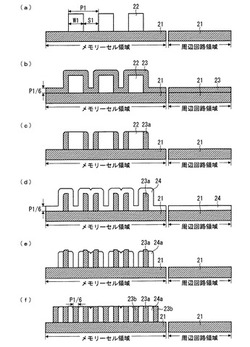

【課題】パターニングされた被エッチング膜のシリサイド化を簡便に行うことのできる半導体素子の製造方法を提供する。

【解決手段】本発明の半導体素子の製造方法は、ポリシリコン膜21上にSiO2 膜22をパターンニングし、SiO2 膜22を覆うようにポリシリコン膜23を堆積した後、SiO2 膜22の側壁部分にポリシリコン電極23aを形成する。次いで、SiO2 膜22を除去した後、堆積したSiO2 膜24をエッチバックして電極23aの側壁部にSiO2 からなるサイドウォール24aを形成する。次いで、サイドウォール24aの間にポリシリコンを埋め込むことによってポリシリコン電極23bを形成し、サイドウォール24aを除去して、ポリシリコン膜21およびポリシリコン電極23a,23bをエッチバックすることでポリシリコン膜21をパターンニングする。

(もっと読む)

半導体装置の製造方法

【課題】簡易な工程で、自己整合シリサイドプロセスを用いた、ポリ抵抗を有する半導体装置を得ることができる製造方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板10に素子分離層20を形成する工程と、素子分離層の上方に抵抗層110を形成する工程と、抵抗層を覆う第1絶縁層120を形成する工程と、半導体基板の上方であって、素子分離層で区画された領域に、ゲート酸化膜220を形成する工程と、ゲート酸化膜の上方にゲート電極210を形成する工程と、ゲート電極の側壁にサイドウォール240を形成する工程と、半導体基板の露出した領域に不純物を注入して、ソースおよびドレイン領域を形成する工程と、第1絶縁層をパターニングすることによって、抵抗層を露出する工程と、抵抗層の露出した領域と、ゲート電極の上と、ソースおよびドレイン領域の上と、にシリサイド層30を形成する工程とを含む。

(もっと読む)

半導体装置及びその製造方法

【課題】SRAMにおいてNMOS及びPMOSトランジスタのバランスを確保して、PMOSトランジスタの閾値電圧を高くできる半導体装置及びその製造方法を提供する。

【解決手段】メモリ領域において、基板の第1半導体領域(12,13)の第1チャネル形成領域上に第1ゲート絶縁膜(20,21)を介して第1ゲート電極が形成され、第1半導体領域に第1ソースドレイン領域(16,17)が形成されて第1トランジスタが形成され、ロジック領域において、基板の第2半導体領域(14,15)の第2チャネル形成領域上に第2ゲート絶縁膜(22,23)を介して第2ゲート電極が形成され、第2半導体領域に第2ソースドレイン領域(18,19)が形成されて第2トランジスタが形成され、第1ゲート電極の第1ゲート絶縁膜に接する部分が金属(40,41)からなり、第2ゲート電極の第2ゲート絶縁膜に接する部分が半導体(26,27)からなる。

(もっと読む)

半導体装置ならびに半導体装置の製造方法

【課題】ゲート絶縁膜上のゲート電極の仕事関数を増大させることができ、低い閾値電圧の半導体装置を提供する。

【解決手段】半導体装置1は、基板(シリコン基板2)と、シリコン基板2上に設けられたゲート絶縁膜4と、ゲート絶縁膜4上に設けられたゲート電極(Pt含有Ni3Si電極19)を備え、Pt含有Ni3Si電極19が、ゲート絶縁膜4とPt含有Ni3Si電極19との接する部分に、第一金属を含む第一金属シリサイド、および第二金属を含む第二金属シリサイドまたは第二金属を含み、第二金属を含む第二金属シリサイドが、第二金属を含む第二金属シリサイド中のシリコンに対する第二金属の組成比が1より大きい金属リッチシリサイドであることを特徴とする。

(もっと読む)

金属シリサイド形成のための方法および装置

本明細書で述べられる実施形態は、無拡散アニールプロセスを使用して金属シリサイド層を形成する方法を包含する。一実施形態では、基板上に金属シリサイド材料を形成するための方法が、提供される。その方法は、基板のシリコン含有表面を覆って金属材料を堆積させるステップと、金属材料を覆って金属窒化物材料を堆積させるステップと、金属窒化物材料を覆って金属接点材料を堆積させるステップと、基板を無拡散アニールプロセスにさらして金属シリサイド材料を形成するステップとを含む。無拡散アニールプロセスの短い時間枠は、窒素がシリコン含有界面に拡散して窒化シリコンを形成する時間を低減し、それ故に界面抵抗を最小限にする。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】ゲート電極における寸法ばらつきの発生を抑制し、且つ寸法の細いゲート電極を形成し得る半導体装置の製造方法を提供する。

【解決手段】基板5にゲート電極膜60を形成する工程と、前記ゲート電極膜表面に反射防止膜8を形成する工程と、前記反射防止膜の表面にレジストパターン7を形成する工程と、前記レジストパターンにおけるエッチングレートが100Å/分以下となるようにプラズマ中のイオンを引き込むための電極にバイアスパワーを印加し、且つ前記レジストパターンとは非反応性のガスを用いてプラズマを発生させて前記レジストパターンに照射する工程と、前記レジストパターンをマスクとして、前記反射防止膜および前記ゲート電極をエッチングする工程と、前記レジストパターンおよび反射防止膜を除去する工程と、を有する。

(もっと読む)

固体撮像装置、その製造方法および撮像装置

【課題】本発明は、画素部のMOSトランジスタ上で異なる2層のシリサイドブロック膜の一部が重なるように形成して、白傷、暗電流を低減することを可能にする。

【解決手段】半導体基板11に、光電変換部21を備えた画素部12とその周辺に形成された周辺回路部13を有し、画素部12のゲート電極32の側壁にサイドウォール形成膜で形成された第1サイドウォール33と、周辺回路部13のゲート電極52の側壁にサイドウォール形成膜で形成された第2サイドウォール53と、光電変換部21上および画素部12のMOSトランジスタ30の一部上にサイドウォール形成膜で形成された第1シリサイドブロック膜71と、画素部12のMOSトランジスタ30上に、第1シリサイドブロック膜71の一部上に重なる第2シリサイドブロック膜72を有し、第1、第2シリサイドブロック膜71、72で画素部12のMOSトランジスタ30上が被覆されている。

(もっと読む)

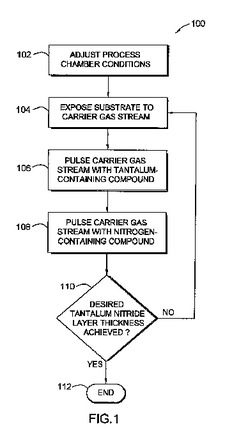

インサイチュチャンバ処理および堆積プロセス

本発明の実施形態は、原子層堆積(ALD)または化学気相堆積(CVD)などの気相堆積プロセス中に、プロセッシングチャンバの内面を処理し、材料を堆積させる方法を提供する。一実施形態では、前処理プロセス中に、プロセッシングチャンバの内面および基板を、水素化配位子化合物などの試薬にさらすことができる。この水素化配位子化合物は、次の堆積プロセス中に使用される有機金属前駆体から形成される遊離配位子と同じ配位子とすることができる。この遊離配位子は、堆積プロセス中に、通常、水素化または熱分解によって形成される。一例では、プロセッシングチャンバおよび基板は、ペンタキス(ジメチルアミノ)タンタル(PDMAT)などのアルキルアミノ配位子を有する有機金属化学前駆体を利用した気相堆積プロセスを行う前に、前処理プロセス中に、アルキルアミン化合物(例えば、ジメチルアミン)にさらされる。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート酸化膜やゲート酸化膜と半導体基板の界面にダメージを与えることなく、界面準位の低減を図る。

【解決手段】シリコン酸化膜6で覆われたゲート電極4にポリシリコン膜8aとタングステンシリサイド膜8bの積層膜からなり、弗素を含んだ弗素含有膜8を形成する。この場合、先ず、シリコン酸化膜6で覆われたゲート電極4上にポリシリコン膜8aを形成し、ポリシリコン膜8a上にWF6とSiH4を原料ガスとしてLPCVD法によりタングステンシリサイド膜8bを形成する。この場合、WF6中の弗素はSiH4中の水素と反応し、大半は弗化水素(HF)ガスとして排気され、タングステンシリサイド膜8bを形成する反応が継続するが、弗素の一部はタングステンシリサイド膜8bの中に取り込まれる。その後、タングステンシリサイド膜8bの弗素をゲート酸化膜3中に熱拡散させるための熱処理が施される。

(もっと読む)

半導体装置及びその製造方法

【課題】均一な厚さの金属シリサイド膜からなるゲート電極を備える半導体装置及びその製造方法を提供すること。

【解決手段】本発明の半導体装置及びその製造方法は、基板上に絶縁膜を形成するステップと、前記絶縁膜上に金属の拡散を防止する拡散防止膜を形成するステップと、前記拡散防止膜上にゲート電極用膜を形成するステップと、前記ゲート電極用膜上に金属膜を形成するステップと、前記金属膜を含む結果物に対して熱処理工程を行うことにより、均一な厚さの金属シリサイド膜を形成するステップと、を含む。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】簡易なプロセスで抵抗層上の所定領域を選択的にサリサイド化することができ、かつ、抵抗の占有面積を小さくすることができる半導体装置の製造方法を提供する。

【解決手段】第1素子形成領域1と第2素子形成領域2とを有し、第2素子形成領域2に第1抵抗層30を形成し、その上に第1絶縁層40と導電層を形成し、第2素子形成領域2の導電層を高抵抗化し、導電層の一部を除去して、第1素子形成領域1にゲート電極50を形成すると同時に、第2素子形成領域2に第2抵抗層52を形成し、第2素子形成領域2の第2抵抗層52の上方に第2絶縁層90を形成し、第1素子形成領域1の半導体基板10に不純物を注入して、ソース領域およびドレイン領域70a,70bを形成し、ソース領域およびドレイン領域70a,70bの上と、第2素子形成領域2の第1抵抗層30および第2抵抗層52の上と、にシリサイド層80を形成する。

(もっと読む)

電界効果トランジスタおよび電界効果トランジスタの製造方法

【課題】オン抵抗が低く、耐圧性及びチャネル移動度が高い電界効果トランジスタ及び電界効果トランジスタの製造方法を提供すること。

【解決手段】MOS構造を有し、窒化物系化合物半導体からなる電界効果トランジスタであって、基板上に形成された所定の導電型を有する半導体層と、エピタキシャル成長によって前記半導体層とソース電極およびドレイン電極のそれぞれとの間に形成された、前記所定の導電型とは反対の導電型を有するコンタクト層と、エピタキシャル成長によって前記ドレイン電極側のコンタクト層と前記半導体層との間にゲート絶縁膜を介してゲート電極と重畳するように形成された、前記所定の導電型とは反対の導電型を有するとともに該コンタクト層よりもキャリア濃度が低い電界緩和層と、を備える。

(もっと読む)

化合物半導体装置およびその製造方法

【課題】耐湿性を向上することのできる化合物半導体装置およびその製造方法を提供する。

【解決手段】化合物半導体装置は、オーミック電極OMEa〜OMEdと、絶縁膜ILと、金を含む配線IC1a〜IC1dと、金を含む配線IC2a〜IC2dとを備えている。絶縁膜ILはオーミック電極OMEa〜OMEdの一部上に形成されている。配線IC1a〜IC1dは、オーミック電極OMEa〜OMEd上で絶縁膜ILが形成されていない部分であって、絶縁膜ILの側面に接触する位置に形成されている。配線IC2a〜IC2dは、絶縁膜IL上および配線IC1a〜IC1d上に形成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】互いに異なる金属膜厚からなるゲート電極を有するn型及びp型MISトランジスタを備えた半導体装置において、ゲートリークによる劣化を抑制する。

【解決手段】半導体装置は、第1のMISトランジスタと第2のMISトランジスタとを備える。第1のMISトランジスタは、第1の活性領域12a上に形成された第1のゲート絶縁膜13aと、第1のゲート絶縁膜13a上に形成された第1の金属膜14a、及び、第1の金属膜14a上に形成された第1のシリコン膜17aを含む第1のゲート電極24Aとを備える。第2のMISトランジスタは、第2の活性領域12b上に形成された第2のゲート絶縁膜13bと、第2のゲート絶縁膜上に形成された第1の金属膜14b、第1の金属膜14b上に形成された第2の金属膜15b、及び、第2の金属膜15bの上に形成された第2のシリコン膜17bを含む第2のゲート電極24Bとを備えている。

(もっと読む)

ヘテロ接合バイポーラトランジスタ

【課題】自己発熱および高電流密度動作下においても劣化を生じにくく、高電流密度まで安定して通電可能な高信頼電極を有し、より高い信頼度を達成可能なヘテロ接合バイポーラトランジスタを提供すること。

【解決手段】半導体基板1上に、サブコレクタ層2、コレクタ層3、ベース層4、エミッタ層5およびエミッタコンタクト層6が順次積層されたヘテロ接合バイポーラトランジスタにおいて、エミッタコンタクト層6とエミッタ電極7との間に、Moの融点以上の融点を有する単体金属または合金からなるバリア金属層13−2(図2に示す)を有するバリア複合層13が介在することを特徴とするヘテロ接合バイポーラトランジスタを構成する。

(もっと読む)

半導体装置

【課題】高周波デバイスを形成する複数の素子を一つのチップに形成できる技術を提供する。

【解決手段】

基板1上にて抵抗素子および容量素子の下部電極を同一の多結晶シリコン膜から形成し、前記多結晶シリコン膜とは異なる同一の多結晶シリコン膜およびWSi膜からパワーMISFETのゲート電極、容量素子の上部電極、nチャネル型MISFETのゲート電極およびpチャネル型MISFETのゲート電極を形成し、領域MIMにおいては基板1上に堆積された酸化シリコン膜30上に形成された配線を下部電極とし酸化シリコン膜34上に形成された配線を上部電極とする容量素子MIMCを形成し、酸化シリコン膜34上に堆積された酸化シリコン膜37上に堆積された同一のアルミニウム合金膜を用い領域INDにて配線39Aからなるスパイラルコイルを形成し、領域PADでは配線39Bからなるボンディングパッドを形成する。

(もっと読む)

半導体装置、及びその製造方法

【課題】 金属層と半導体層との接続抵抗の上昇を抑えた積層ゲート電極を有する半導体装置、及びその製造方法を提供する。

【解決手段】 半導体装置10は、半導体基板11に形成された第1導電型のソース領域及びドレイン領域14と、ソース領域とドレイン領域との間に形成されたチャネル領域16と、チャネル領域上に形成されたゲート絶縁膜21とを有する。半導体装置10は更に、ゲート絶縁膜上に形成された金属ゲート電極層22と、金属ゲート電極層上に形成された、第1導電型とは逆の導電型である第2導電型の半導体ゲート電極層23とを有する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】半導体装置の動作不良を防止し、半導体装置の製造工程を簡略化する。

【解決手段】本発明の例に関わる半導体装置は、半導体基板1と、半導体基板1内に設けられる一対の不純物拡散層2A,2Bと、不純物拡散層2A,2B間の半導体基板上に設けられるゲート絶縁膜3と、ゲート絶縁膜3上に設けられるゲート電極4と、一対の不純物拡散層2A,2B上にそれぞれ設けられる2つのコンタクト5A,5Bとを具備し、ゲート電極4とコンタクト5A,5Bは、同じ材料から構成され、ゲート電極4上端およびコンタクト5A,5B上端は、半導体基板1表面からの高さが一致する。

(もっと読む)

半導体装置の製造方法および固体撮像装置の製造方法

【課題】本発明は、コンタクト抵抗の安定性を確保して、コンタクト抵抗にばらつきを抑えることを可能にする。

【解決手段】基板11のシリコン領域12上に第1金属シリサイド層13を形成する工程と、前記基板11上に前記第1金属シリサイド層13を被覆する絶縁膜14を形成する工程と、前記絶縁膜14に前記第1金属シリサイド層13に通じるコンタクトホール15を形成する工程と、前記コンタクトホール15の内面および前記絶縁膜14上にシリサイド化される第2金属層16を形成する工程と、前記第2金属層16と前記コンタクトホール15の底部のシリコンとを反応させて前記第1金属シリサイド層13上に第2金属シリサイド層17を形成する工程とを有する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】チャネル部に対して効果的に応力を印加することが可能で、これによりキャリア移動度の向上を図ることが可能で高機能化が達成された半導体装置を提供する。

【解決手段】半導体基板3の表面を掘り下げた凹部3a内にゲート絶縁膜5を介して設けられたゲート電極7と、ゲート電極7の両脇における半導体基板3の表面側に設けられたソース/ドレイン拡散層11と、ソース/ドレイン拡散層11の表面を覆う状態で半導体基板3の表面よりも深く設けられたシリサイド膜(応力印加層)13とを備えた半導体装置1-1である。半導体基板3の表面に対するチャネル部chの深さ位置d2は、シリサイド膜(応力印加層)13の深さd1位置よりも浅い。

(もっと読む)

141 - 160 / 591

[ Back to top ]