Fターム[4M104BB28]の内容

半導体の電極 (138,591) | 電極材料 (41,517) | 遷移金属のシリサイド (5,826) | 高融点金属のシリサイド (2,215) | WSi (591)

Fターム[4M104BB28]に分類される特許

101 - 120 / 591

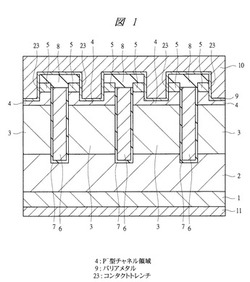

半導体装置およびその製造方法ならびにそれを用いたDC−DCコンバータ

【課題】内蔵ダイオードを有するトレンチMOSFETのしきい値電圧を向上させると共に、ドレインリーク電流の発生を低減させる。

【解決手段】内蔵ダイオードを有するトレンチMOSFETにおいて、コンタクトトレンチ23の下部におけるP−型チャネル領域4の厚さを200nm以下とし、バリアメタル9とP−型チャネル領域4をショットキー接合させてショットキーバリアダイオードを備えることにより、しきい値電圧を向上させ、ドレインリーク電流の発生を低減させることができる。

(もっと読む)

半導体装置の洗浄方法

【課題】ゲートメタル材料の溶解抑制と良好なコンタクト抵抗取得とを両立可能な半導体装置の洗浄方法を提供する。

【解決手段】半導体装置の洗浄方法は、以下の工程を備えている。シリコンを含み、かつ主表面MSを有する半導体基板SBが準備される。主表面MSの上にメタル層GMとシリコン層GPとを下から順に積層した積層ゲートGE2が形成される。主表面MSとシリコン層GP表面との各々にシリサイド層SCLが形成される。主表面MSと積層ゲートGE2表面との各々のシリサイド層SCLの上に絶縁層ILが形成される。半導体基板SBの主表面MSと積層ゲートGE2の表面との各々のシリサイド層SCLが絶縁層ILから露出するようにシェアードコンタクトホールSC2が絶縁層ILに形成される。シェアードコンタクトホールSC2に硫酸洗浄、過酸化水素水洗浄およびAPM洗浄をそれぞれ別工程で行うことによりシェアードコンタクトホールSC2に形成された変質層ALが除去される。

(もっと読む)

半導体装置の製造方法

【課題】新規な半導体装置の製造方法を提供する。

【解決手段】SiN層にPおよびOを注入する工程と、前記SiN層に注入されたPおよびOをH2Oと反応させ、前記SiN層をエッチングする工程とを有する方法により、半導体装置を製造する。特に、半導体装置を形成するにあたり、狭スペースで高アスペクト比の溝サイドウォールを形成する工程や、埋め込み型ビット線を形成する工程に、上記のようにSiN層をエッチングすることができる。

(もっと読む)

電界効果トランジスタおよびその製造方法

【課題】良質な半導体−酸化物界面を有する電界効果トランジスタおよびその製造方法を提供する。

【解決手段】電界効果トランジスタ100は、半導体基板101と、半導体基板101上に形成されたチャネル層102と、チャネル層102上に形成された電子供給層103と、電子供給層103内に形成され、Ptを含む半導体層106と、半導体層106上に形成され、ゲート絶縁膜として機能するペロブスカイト型酸化物層107と、ペロブスカイト型酸化物層107上に形成されたゲート電極108とを備える。

(もっと読む)

半導体装置の製造方法

【課題】フォトリソグラフィーのプロセスマージンを確保すると共に、ゲート電極とコンタクトプラグとの短絡が生じにくい半導体装置の製造方法を実現できるようにする。

【解決手段】半導体装置の製造方法は、層間絶縁膜114の上に第1の下部開口部115aを有する第1のマスク層115を形成する工程と、第1のマスク層115の上に第1の下部開口部115aを通して層間絶縁膜114を露出する第1の上部開口部116aを有する第2のマスク層116を形成する工程とを備えている。第1の下部開口部115aは、隣接するゲート電極102同士の間に形成され、ゲート電極102と平行な方向に延びる長辺と、ゲート電極102と交差する方向に延びる短辺とを有する平面方形状である。第1の上部開口部116aは、各辺の長さが第1の下部開口部115aの短辺よりも長い平面方形状である。

(もっと読む)

半導体装置およびその作製方法

【課題】高開口率な表示装置を提供する。

【解決手段】薄膜トランジスタと、保持容量とが設けられた画素と、走査線と、走査線に直交して設けられた信号線と、を有し、走査線の上方には、薄膜トランジスタのソース領域、ドレイン領域、及びチャネル形成領域が形成される部分と保持容量の下部電極となる部分とを有する半導体膜が設けられ、半導体膜上には絶縁膜が設けられ、半導体膜のチャネル形成領域となる部分の上方には、絶縁膜を介して走査線と電気的に接続されたゲート電極が設けられ、半導体膜の下部電極となる部分の上方には、絶縁膜を介して保持容量の上部電極が設けられ、半導体膜は、基板に平行であり、ゲート電極は、保持容量の上部電極より半導体膜を基準に高い場所に設けられ、ゲート電極及び上部電極の上方には、信号線が設けられている表示装置。

(もっと読む)

半導体装置の製造方法

【課題】ポリシリコン・ゲート電極作成のためのエッチング処理時に、クランプによって覆われていたポリサイド層上の層間絶縁膜の膜剥がれが起こりにくい半導体装置の製造方法を提供する。

【解決手段】半導体基板110上に、ポリシリコン膜220及びタングステン・シリサイド膜210をこの順に積層してポリサイド・ゲート電極230を形成する。ポリサイド・ゲート電極230を含む半導体基板110上に、B濃度が高濃度の下層BPSG膜140を第1の成膜速度v1で形成する。下層BPSG膜140の上に、B濃度が下層BPSG膜140より低い低濃度の上層BPSG膜120を第2の成膜速度v2で形成する。第2の成膜速度は前記第1の成膜速度未満である。

(もっと読む)

半導体装置およびその製造方法

【課題】メタルゲート電極を有するpチャネル型電界効果トランジスタにおいて、所望するしきい値電圧を安定して得ることのできる技術を提供する。

【解決手段】半導体基板1上に形成されたHfSiON膜からなるゲート絶縁膜5h上に、Me−O−Al−O−Me結合を含むMe1−xAlxOy(0.2≦x≦0.75、0.2≦y≦1.5)組成の導電性膜を一部に有するメタルゲート電極6、またはMe−O−Al−N−Me結合を含むMe1−xAlxN1−zOz(0.2≦x≦0.75、0.1≦z≦0.9)組成の導電性膜を一部に有するメタルゲート電極6を形成する。

(もっと読む)

半導体装置の製造方法

【課題】ハーフピッチサイズが32nm以下のCMISデバイスを有する半導体装置において、nチャネル型電界効果トランジスタおよびpチャネル型電界効果トランジスタのそれぞれの閾値電圧を適切に設定することのできる技術を提供する。

【解決手段】pMIS形成領域に、主としてAlが拡散した高誘電体膜5h(例えばHfO2膜)により構成されるゲート絶縁膜5ならびに下層メタルゲート電極6Dと上層メタルゲート電極6Uとの積層膜からなるメタルゲート電極6を有するpMIS100pを形成し、nMIS形成領域に、主としてLa(ランタン)が拡散した高誘電体膜5h(例えばHfO2膜)により構成されるゲート絶縁膜11ならびに上層メタルゲート電極6Uからなるメタルゲート電極12を有するnMIS100nを形成する。

(もっと読む)

非対称型半導体デバイス及び製造方法

【課題】 非対称型半導体デバイス、及びその製造の際にスペーサ・スキームを用いる方法を提供する

【解決手段】 高kゲート誘電体の表面上に配置された非対称型ゲート・スタックを含む半構造体が提供される。非対称型ゲート・スタックは、第1の部分と第2の部分とを含み、第1の部分は、第2の部分とは異なる閾値電圧を有する。本発明の非対称型ゲート・スタックの第1の部分は、下から上に、閾値電圧調整材料及び少なくとも第1の導電性スペーサを含み、本発明の非対称型ゲート・スタックの第2の部分は、ゲート誘電体の上の少なくとも第2の導電性スペーサを含む。幾つかの実施形態において、第2の導電性スペーサは、下にある高kゲート誘電体と直接接触しており、他の実施形態においては、第1及び第2の導電性スペーサは、前記閾値電圧調整材料と直接接触している。

(もっと読む)

半導体装置の製造方法

【課題】 トランジスタのスイッチング速度低下を防止することが可能な半導体装置の製造方法を提供する。

【解決手段】 本発明では、半導体基板100上にゲート絶縁膜104を形成する工程と、ゲート絶縁膜104上に金属膜107を形成する工程と、金属膜107上に金属シリコン化合物膜108を連続して堆積する工程と、金属シリコン化合物膜108上にシリコン膜110を形成する工程と、金属膜107、金属シリコン化合物膜108及びシリコン膜110を加工する工程と、を備える。

(もっと読む)

半導体装置およびその製造方法

【課題】電力増幅モジュールの放熱特性を向上させる。

【解決手段】電力増幅モジュールに用いられる電力増幅回路用のLDMOSFET素子が形成された半導体チップにおいて、LDMOSFET素子用の複数のソース領域、複数のドレイン領域および複数のゲート電極39が形成されたLDMOSFET形成領域上に、ソース用バンプ電極BPSを配置する。ソース用バンプ電極BPSは、アルミニウムを主体とするソース用パッドM3S上に、ソース用パッドM3Sよりも厚くかつ銅を主体とするソース用導体層CNDSを介して形成する。ソース用バンプ電極BPSとソース用導体層CNDSの間には樹脂膜は介在していない。

(もっと読む)

半導体装置の作製方法

【課題】TFTを用いた半導体装置において、TFT中の汚染不純物を低減し、信頼性のあるTFTを得ることを課題とする。

【解決手段】ガラス基板上のTFTの被膜に存在する汚染不純物を、フッ素を含有する酸性溶液を被膜表面に接触させ、酸性溶液を一定方向に流すことにより、被膜表面の汚染不純物を除去することにより、信頼性のあるTFTを得ることができる。なお、酸性溶液は、フッ酸とフッ化アンモニウムの混合比が体積比で1:50のバッファードフッ酸を用いる。

(もっと読む)

半導体装置およびその製造方法

【課題】製造工程の増加を抑えて、通常のコンタクトとシェアードコンタクトとをそれぞれ良好なコンタクト特性を有するようにする。

【解決手段】半導体装置100は、第1の不純物拡散領域106aに接続するとともに、第1のゲート電極112aとは接続しないように形成された第1のコンタクト124と、第2のゲート電極112bおよび第2の不純物拡散領域106bに共通して接続するように形成された第2のコンタクト126とを含む。第1のコンタクト124および第2のコンタクト126は、それぞれ、層間絶縁膜122の表面から基板101に向かう途中の位置でテーパー角度が小さくなるように変化する形状を有し、第2のコンタクト126においてテーパー角度が変化する位置が、第1のコンタクト124においてテーパー角度が変化する位置よりも基板101に近い。

(もっと読む)

半導体装置

【課題】ゲート配線として耐熱性の導電性材料であるタングステン層を用いた場合に、タングステン層の比抵抗を低くすることによって、配線抵抗を十分に低減することを目的とする。

【解決手段】半導体層と、ゲート配線と、前記半導体層と前記ゲート配線との間に挟まれたゲート絶縁層とを有し、前記ゲート配線はタングステン層を有し、前記タングステン層中の酸素濃度を30ppm以下とすることによって、配線抵抗を十分に低減することができる。

(もっと読む)

ヘテロ接合バイポーラトランジスタの製造方法

【課題】アスペクト比の高いサブミクロンサイズのエミッタ電極パタンを線幅制御性良く形成することを可能とするヘテロ接合バイポーラトランジスタの製造方法を提供すること。

【解決手段】エミッタコンタクト層6上にTi層(図示せず)、エッチングストッパー用のW層7、Au層8、エッチングマスク用W層9、フォトレジストパタン10を形成し、フォトレジストパタン10をマスクとしてエッチングマスク用W層9を選択的に除去することによってWパタン9とし、Wパタン9をマスクとして、Au層8を、酸素ガスを含有する混合ガスを用いる反応性イオンエッチング法により選択的に除去し、Wパタン9をマスクとして、エッチングストッパー用のW層7、Ti層を選択的に除去することを特徴とするヘテロ接合バイポーラトランジスタの製造方法を構成する。

(もっと読む)

補償型ゲートMISFET及びその製造方法

低いゲートリークを有する例えばGaNトランジスタなどのMISFETが提供される。一実施形態において、ゲートコンタクトの下且つバリア層の上に、補償型のGaN層を有することで、ゲートリークが低減される。他の一実施形態において、ゲートコンタクトの下且つバリア層の上に半絶縁性の層を用いることによって、ゲートリークが低減される。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】微細化に対応可能であり、不純物拡散領域上に形成したコンタクトプラグが近傍の導電材料とショートすることを防止する配線構造を有する半導体装置を提供する。

【解決手段】半導体基板内の不純物拡散領域22上に選択エピタキシャル成長法により、第1の層16aを形成する工程と、第1の層16a上に、選択エピタキシャル成長法により第2の層18を形成する工程と、第2の層18上に導電材料を充填することにより、コンタクトプラグ21を形成する工程と、を有する。

(もっと読む)

W含有膜の製造方法および電気光学装置の製造方法

【課題】WSi膜上にSiO2膜を形成し、SiO2膜を緻密化するため成膜温度より高い温度でアニールを行った場合、SiO2膜中にクラックが入る欠陥が生じる場合がある。このクラックの発生を抑えるために、アニール時の温度変化速度を抑え、急激な熱膨張/熱収縮を避けているが、クラック欠陥を十分抑えられないという課題がある。

【解決手段】WSi膜を用いた、走査線前駆体11cをスパッタリングにより200nmの膜厚に堆積させる。そして、無機絶縁膜100としてSiO2膜を堆積する。そして、約700℃で熱処理を行う。そして、無機絶縁膜100を除去する。走査線前駆体11cの改質に伴い、無機絶縁膜100との間には応力が掛かっている。ここで、無機絶縁膜100を除去することで、走査線前駆体11cの改質に伴う応力を開放することが可能となり、クラック欠陥の発生を抑えることが可能となる。

(もっと読む)

W含有膜の製造方法および電気光学装置の製造方法

【課題】WSi膜上にSiO2膜を形成し、SiO2膜を緻密化するため成膜温度より高い温度でアニールを行った場合、SiO2膜中にクラックが入る欠陥が生じる場合がある。このクラックの発生を抑えるために、アニール時の温度変化速度を抑え、急激な熱膨張/熱収縮を避けているが、クラック欠陥を十分抑えられないという課題がある。

【解決手段】WSi膜を用いた、走査線前駆体11cをスパッタリングにより200nmの膜厚に堆積させる。そして、パターニング後、無機絶縁膜100としてSiO2膜を堆積する。そして、約700℃で熱処理を行う。そして、無機絶縁膜100を除去する。走査線前駆体11cの改質に伴い、無機絶縁膜100との間には応力が掛かっている。ここで、無機絶縁膜100を除去することで、走査線前駆体11cの改質に伴う応力をパターン側面を含めて開放することが可能となり、クラック欠陥の発生を抑えることが可能となる。

(もっと読む)

101 - 120 / 591

[ Back to top ]