Fターム[4M104BB28]の内容

半導体の電極 (138,591) | 電極材料 (41,517) | 遷移金属のシリサイド (5,826) | 高融点金属のシリサイド (2,215) | WSi (591)

Fターム[4M104BB28]に分類される特許

81 - 100 / 591

半導体装置の製造方法

【課題】最近の多層メタルスパッタリング成膜プロセスにおいては、従来のマルチチャンバ型の装置に代わって、単一チャンバ&マルチ成膜サイト型の装置が広く使用されるようになっている。しかし、本願発明者が検討したところによると、このような単一チャンバ&マルチ成膜サイト型スパッタリング成膜装置は、磁性メタル膜と非磁性メタル膜を積層形成する場合は、被処理ウエハを別の成膜サイトに移送して成膜する必要があり、スループットを大きく低下させていることが明らかとなった。

【解決手段】本願発明は、単一チャンバ&マルチ成膜サイト型多層スパッタリング成膜装置を用いた半導体装置の製造方法において、少なくとも一つの成膜サイトにおいて、磁性および非磁性ターゲットの両方を切り替えて用い、磁性および非磁性膜の両方の膜を成膜するものである。

(もっと読む)

半導体装置およびその製造方法

【課題】配線として用いられる金属シリサイド層の断線の発生を抑えつつ、微細化を可能にする半導体装置及びその製造方法を提供する。

【解決手段】半導体装置は、半導体基板と、半導体基板のタップ領域40、トランジスタ領域36、及びシリサイド配線領域38に形成された活性領域と、シリサイド配線領域38上からトランジスタ領域36上に亘って形成されたゲート電極21と、活性領域上に設けられた金属シリサイド層44aとを備えている。シリサイド配線領域38の少なくとも一部上におけるゲート電極21と金属シリサイド層44aとの距離は、トランジスタ領域36上におけるゲート電極と金属シリサイド層44aとの距離よりも小さい。

(もっと読む)

半導体装置およびその作製方法

【課題】新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】半導体材料を含む基板に設けられたチャネル形成領域と、不純物領域と、第1のゲート絶縁層と、第1のゲート電極と、第1のソース電極および第1のドレイン電極と、を有する第1のトランジスタと、半導体材料を含む基板上の酸化物半導体層と、第2のソース電極および第2のドレイン電極と、第2のゲート絶縁層と、第2のゲート電極と、を有する第2のトランジスタと、を有し、第2のソース電極および第2のドレイン電極は、その側面が酸化された酸化領域を有し、第1のゲート電極、第1のソース電極、または第1のドレイン電極のいずれかは、第2のゲート電極、第2のソース電極、または第2のドレイン電極のいずれかと電気的に接続されている半導体装置である。

(もっと読む)

半導体装置およびその製造方法

【課題】本発明は、高速動作を具現することができる埋込型ビットラインを備える半導体装置、およびその製造方法を提供する。

【解決手段】このための本発明の半導体装置は、トレンチを備える基板と、前記基板内に形成され前記トレンチ側壁に接する金属シリサイド膜と前記トレンチ側壁に形成され前記金属シリサイド膜と接する金属性膜からなる埋込型ビットラインとを備えており、上述した本発明によれば、金属シリサイド膜と金属性膜からなる埋込型ビットラインを提供することによって、従来のシリコン配線形態の埋込型ビットラインに比べて、その抵抗値を顕著に減少させることができるという効果がある。

(もっと読む)

真空成膜装置用部品の製造方法

【課題】成膜工程中に付着する成膜材料の剥離を安定かつ有効に防止することを可能にした真空成膜装置用部品の製造方法を提供する。

【解決手段】真空成膜装置用部品1の製造方法は、部品本体2の表面にWおよびMoから選ばれる高融点金属からなる溶射膜3を形成する工程と、溶射膜3を還元雰囲気中にて1073〜1373Kの温度で加熱し、溶射膜3の表面に存在する酸化被膜を除去しつつ脱ガス処理する工程とを具備する。脱ガス処理後の溶射膜は、ガス残存量が10Torr・cc/g以下とされている。

(もっと読む)

半導体装置及びその製造方法

【課題】 ゲートとドレインの間で生じる電界集中を緩和する半導体装置を提供する。

【解決手段】本発明によれば,半導体基板上にゲート絶縁膜を介して形成された第1のゲート電極と、前記半導体基板上に前記ゲート絶縁膜を介して形成され、かつ、第1のゲート電極の側面に絶縁性のスペーサを介して配置された第2のゲート電極と、第1及び第2のゲート電極を挟むように前記半導体基板上に形成されたソース領域及びドレイン領域と、第1のゲート電極下方における前記半導体基板の一部の領域を挟むように形成され、第2のゲート電極及び前記ソース領域及びドレイン領域と重なるように形成された電界緩和領域と、を備える半導体装置が提供される。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート電極の下部からゲート電極の形成されていない基板上の領域に斜め方向のイオン注入を行って形成される不純物拡散領域を有する半導体装置において、半導体装置のサイズを従来に比して縮小化することができる半導体装置を提供する。

【解決手段】N型半導体層13の表面に形成されるP型のベース領域21と、ベース領域21内に形成されるP+型ソース領域22およびN+型ソース領域23を有するソース領域と、N型半導体層13の表面にベース領域21から離れて形成されるN+型のドレイン領域26と、ソース領域とドレイン領域26との間にゲート絶縁膜41を介して形成されるゲート電極42と、ドレイン領域26からゲート電極42の下部にかけて、ドレイン領域26に隣接して形成されるN型のドリフト領域と、を備え、ゲート電極42とゲート絶縁膜41との積層体のソース領域側側面の高さが、ドレイン領域側側面の高さよりも高く形成される。

(もっと読む)

コンタクトプラグ、配線、半導体装置およびコンタクトプラグ形成方法

【課題】薄膜であっても銅(Cu)原子の金属シリサイド膜などへの拡散を充分に安定して抑止でき、尚且つ、小さな接触抵抗をもたらす比抵抗の小さな銅(Cu)からコンタクトプラグを形成できるようにする。

【解決手段】 本発明のコンタクトプラグ100は、半導体装置の絶縁膜104に設けられたコンタクトホール105に形成され、コンタクトホール105の底部に形成された金属シリサイド膜103と、コンタクトホール105内で金属シリサイド膜103上に形成された酸化マンガン膜106と、酸化マンガン膜106上に、コンタクトホール105を埋め込むように形成された銅プラグ層107と、を備え、酸化マンガン膜は非晶質からなる膜である、ことを特徴としている。

(もっと読む)

半導体装置の作製方法

【課題】 信頼性の高いTFT構造を用いた半導体装置を実現する。

【解決手段】 TFTに利用する絶縁膜、例えばゲート絶縁膜、保護膜、下地膜、層間絶縁膜等として、ボロンを含む窒化酸化珪素膜(SiNX BY OZ )をスパッタ法で形成する。その結果、この膜の内部応力は、代表的には−5×1010dyn/cm2 〜5×1010dyn/cm2 、好ましくは−1010dyn/cm2 〜1010dyn/cm2 となり、高い熱伝導性を有するため、TFTのオン動作時に発生する熱による劣化を防ぐことが可能となった。

(もっと読む)

III族窒化物半導体デバイス及びその製造方法

III族窒化物トランジスタ・デバイスを形成する方法は、III族窒化物半導体層上に保護層を形成するステップと、III族窒化物半導体の一部を露出するように保護層を貫通するビアホールを形成するステップと、保護層上にマスキングゲートを形成するステップとを含む。マスキングゲートは、ビアホールの幅より大きい幅を有する上部を含み、ビアホールの中に延びる下部を有する。この方法はさらに、マスキングゲートを注入マスクとして用いて、III族窒化物層内にソース/ドレイン領域を注入するステップを含む。 (もっと読む)

半導体装置

【課題】窒化物半導体を用いたノーマリオフ型のトランジスタを備えた半導体装置において、駆動時のゲート電流を低減しつつ、トランジスタの過渡応答特性を安定させる。

【解決手段】半導体装置は、基板101と、基板101の上に積層された複数の窒化物半導体層からなり、且つチャネル領域を含む第1の窒化物半導体層104Sと、第1の窒化物半導体層104Sの上に形成され、且つチャネル領域と逆導電型の第2の半導体層105と、第2の半導体層105に接するように形成され、金属層107からなる導電層と、導電層の上に形成された絶縁体層110と、絶縁体層110の上に形成されたゲート電極111と、第2の半導体層105の両側方に形成されたソース電極108及びドレイン電極109とを備えている。

(もっと読む)

窒化物半導体装置及びその製造方法

【課題】ゲート電極にバイアス方向バイアスを印加した際におけるゲートリーク電流を低減した窒化物半導体装置を実現できるようにする。

【解決手段】窒化物半導体装置は、基板101の上に順次形成された第1の窒化物半導体層104及び第2の窒化物半導体層105を含む半導体層積層体103を有している。半導体層積層体103の上には、p型の第3の窒化物半導体層108が選択的に形成されており、第3の窒化物半導体層108の上にはゲート電極109が形成されている。半導体層積層体103の上における第3の窒化物半導体層108の両側方には、それぞれ第1のオーミック電極106及び第2のオーミック電極107が形成されている。第1のゲート電極109は第3の窒化物半導体108とショットキー接触している。

(もっと読む)

半導体装置及びその作製方法

【課題】トランジスタを構成する各部材の抵抗を小さくし、トランジスタのオン電流の向上を図り、集積回路の高性能化を図ることを課題の一とする。

【解決手段】単結晶半導体基板上に絶縁層を介して設けられ、素子分離絶縁層によって素子分離されたn型FET及びp型FETを有する半導体装置であって、それぞれのFETは、半導体材料を含むチャネル形成領域と、チャネル形成領域に接し、半導体材料を含む導電性領域と、導電性領域に接する金属領域と、チャネル形成領域に接するゲート絶縁層と、ゲート絶縁層に接するゲート電極と、金属領域を一部に含むソース電極またはドレイン電極と、を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体基板上に容易なプロセスにより、微細で、高速なSOI構造の縦型のMISFETを得ること。

【解決手段】半導体基板1上に酸化膜2を介して、下部に配線層3を有する自己整合の横及び縦方向エピタキシャル半導体層からなる凸状構造の半導体層6が設けられ、凸状構造の半導体層6は素子分離領域埋め込み絶縁膜4及び酸化膜2により島状に絶縁分離されている。凸状構造の半導体層6の上部には高濃度及び低濃度ドレイン領域10、9が設けられ、下部には高濃度及び低濃度ソース領域7、8が設けられ、側面にはゲート酸化膜11を介してゲート電極12が設けられ、高濃度ドレイン領域10、下層配線3を介した高濃度ソース領域7及びゲート電極12には、それぞれバリアメタル18を有する導電プラグ19を介してバリアメタル21を有するCu配線22が接続されている自己整合連続縦横エピタキシャル成長法によるMISFET。

(もっと読む)

半導体装置及びその作製方法

【課題】トランジスタを構成する各部材の抵抗を小さくし、トランジスタのオン電流の向上を図り、集積回路の高性能化を図ることを課題の一とする。

【解決手段】単結晶半導体基板上に絶縁層を介して設けられ、素子分離絶縁層によって素子分離されたn型FET及びp型FETを有する半導体装置であって、それぞれのFETは、半導体材料を含むチャネル形成領域と、チャネル形成領域に接し、半導体材料を含む導電性領域と、導電性領域に接する金属領域と、チャネル形成領域に接するゲート絶縁層と、ゲート絶縁層に接するゲート電極と、金属領域を一部に含むソース電極またはドレイン電極と、を有する。

(もっと読む)

半導体装置の製造方法

【課題】 半導体装置の製造方法に関し、シリサイドを構成する金属のサイドウォールの直下への潜り込みの影響を低減する。

【解決手段】 シリコン基板上にゲート電極を形成する工程と、ゲート電極の側壁に、第1絶縁膜による第1サイドウォールと、第1サイドウォール上にあって、第1絶縁膜とはエッチング特性の異なる第2絶縁膜による第2サイドウォールを形成する工程と、シリコン基板および第2サイドウォールを含む表面に金属をスパッタリングにより堆積させ、金属の一部をシリコン基板に侵入させる工程と、シリコン基板上に堆積した金属を除去する工程と、金属の除去工程の後に熱処理を行って、スパッタリングによってシリコン基板に侵入した金属とシリコン基板中のシリコン原子とを反応させてシリサイド層を形成する工程とを備える。

(もっと読む)

半導体装置の製造方法

【課題】多層配線を有する半導体装置の信頼性を向上させる。

【解決手段】シリコン基板1上に第1配線用絶縁膜IM1を形成し、第1配線用絶縁膜IM1に配線溝TM1を形成する。その後、配線溝TM1に銅を主体とする導体膜を埋め込むことで配線MW1を形成する。続いて、配線MW1上にキャップ導体膜MC1を形成した後、キャップ導体膜MC1に表面研磨を施す。特に、キャップ導体膜MC1はALD法によって配線MW1上に選択的に形成する。

(もっと読む)

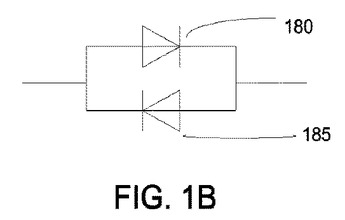

ショットキーダイオードスイッチおよびそれを含むメモリユニット

スイッチング素子は、第1の部分と第2の部分とを有する第1の半導体層と、第1の部分と第2の部分とを有する第2の半導体層と、上記第1の半導体層と上記第2の半導体層との間に配置される絶縁層と、上記第1の半導体層の上記第1の部分と接触して第1の接合部を形成するとともに、上記第2の半導体層の上記第1の部分と接触して第2の接合部を形成する第1の金属コンタクトと、上記第1の半導体層の上記第2の部分と接触して第3の接合部を形成するとともに、上記第2の半導体層の上記第2の部分と接触して第4の接合部を形成する第2の金属コンタクトとを含み、上記第1の接合部と上記第4の接合部とはショットキー接触部であり、上記第2の接合部と上記第3の接合部はオーミック接触部である。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】高誘電率膜のゲート絶縁膜を含むMISFETを有する半導体装置に関し、メタルゲート材料の仕事関数と半導体基板の仕事関数との間の関係によって閾値電圧を容易且つ浅い値に制御しうる半導体装置及びその製造方法を提供する。

【解決手段】半導体基板上に酸化シリコンを主体とする第1の絶縁膜を形成し、第1の絶縁膜上に酸化ハフニウムを主体とする第2の絶縁膜を形成し、熱処理を行い第2の絶縁膜上にシリコンを析出させ、シリコン上にシリコンに対して酸化作用を有する第3の絶縁膜を形成し、第3の絶縁膜上に金属膜のゲート電極を形成し、熱処理を行い第3の絶縁膜の酸化作用によってシリコンを酸化させる。

(もっと読む)

半導体装置の洗浄方法

【課題】ゲートメタル材料の溶解抑制と良好なコンタクト抵抗取得とを両立可能な半導体装置の洗浄方法を提供する。

【解決手段】半導体装置の洗浄方法は、以下の工程を備えている。シリコンを含み、かつ主表面MSを有する半導体基板SBが準備される。主表面MSの上にメタル層GMとシリコン層GPとを下から順に積層した積層ゲートGE2が形成される。主表面MSとシリコン層GP表面との各々にシリサイド層SCLが形成される。主表面MSと積層ゲートGE2表面との各々のシリサイド層SCLの上に絶縁層ILが形成される。半導体基板SBの主表面MSと積層ゲートGE2の表面との各々のシリサイド層SCLが絶縁層ILから露出するようにシェアードコンタクトホールSC2が絶縁層ILに形成される。シェアードコンタクトホールSC2に硫酸洗浄、過酸化水素水洗浄およびAPM洗浄をそれぞれ別工程で行うことによりシェアードコンタクトホールSC2に形成された変質層ALが除去される。

(もっと読む)

81 - 100 / 591

[ Back to top ]