Fターム[4M104BB28]の内容

半導体の電極 (138,591) | 電極材料 (41,517) | 遷移金属のシリサイド (5,826) | 高融点金属のシリサイド (2,215) | WSi (591)

Fターム[4M104BB28]に分類される特許

121 - 140 / 591

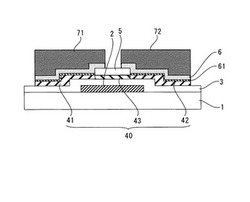

逆スタガ構造の薄膜トランジスタ及びその製造方法

【課題】生産性を向上させ、かつトランジスタ特性が良好な逆スタガ構造の薄膜トランジスタ及びその製造方法を提供すること。

【解決手段】本発明にかかる逆スタガ構造の薄膜トランジスタは、ソース領域41、ドレイン領域42、及びチャネル領域43を有する結晶性半導体膜40を備える。また、薄膜トランジスタは、チャネル領域43上に形成された絶縁膜5と、ソース領域41及びドレイン領域42上に形成されたシリサイド層61とを備える。そして、チャネル領域43は、ソース領域41及びドレイン領域42における結晶粒よりも小さい結晶粒により構成される。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】長期にわたって安定した動作が可能な化合物半導体装置及びその製造方法を提供する。

【解決手段】基板1と、基板1上方に形成された電子走行層2と、電子走行層2上方に形成された電子供給層3と、電子供給層3上方に形成されたソース電極7s、ドレイン電極7d及びゲート電極7gと、が設けられている。ソース電極7sと電子供給層3との間の抵抗は、ゲート電極7gから離間するほど低くなっており、ドレイン電極7dと電子供給層3との間の抵抗は、ゲート電極7gから離間するほど低くなっている。

(もっと読む)

電界効果トランジスタおよび電界効果トランジスタ製造方法

【課題】ゲート電極材料の耐熱上の問題を克服し、ソース抵抗の低減が可能な電界効果トランジスタを提供する。

【解決手段】ゲート電極9を挟んでソース電極8、ドレイン電極10をそれぞれ形成するソース領域3、ドレイン領域6のいずれか一方または双方の領域にイオンを注入し活性化した第1の高濃度キャリア領域6と、ゲート電極9の直下に形成したチャネル領域4と第1の高濃度キャリア領域6との間の領域に、熱処理によりキャリアを拡散させた熱拡散領域7の第2の高濃度キャリア領域とを形成し、第1の高濃度キャリア領域6は、チャネル領域4と互いに隣接して形成される第2の高濃度キャリア領域7と隣接および/または一部重複し、かつ、チャネル領域4以上に深く形成した第2の高濃度キャリア領域7よりも深く形成する。第1の高濃度キャリア領域6のキャリア濃度を、チャネル領域4よりも高濃度の第2の高濃度キャリア領域7よりさらに高くする。

(もっと読む)

半導体装置及びその製造方法

【課題】不純物層が浅く形成された場合にも接合リーク電流の増大を抑制できるようにすると共に、コンタクトホール形成時に位置合わせずれが生じた場合にもコンタクト抵抗の上昇を抑制できるようにする。

【解決手段】基板100上に素子分離領域102及び不純物層103が互いに隣接するように形成されている。不純物層103上にシリサイド層106Bが形成されており、シリサイド層106B上に形成されたコンタクト109が形成されている。不純物層103とシリサイド層106Bとの界面は、素子分離領域102の上面よりも低く、シリサイド層106Bは素子分離領域102の上部コーナーを覆っている。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】n型MOSトランジスタ、p型MOSトランジスタにおいて共通のゲート絶縁膜構造及びゲート電極材料を用いながら、各々のトランジスタのしきい値電圧を適正な値へ設定し、且つゲート絶縁膜における酸素欠損に伴う移動度の低下を抑制する。

【解決手段】メタルゲート電極及び高誘電率ゲート絶縁膜を用いた半導体装置の製造方法であって、n型半導体領域200及びp型半導体領域300上にそれぞれ、シリコン酸化物からなる第1のゲート絶縁膜、La,Al,Oを含む第2のゲート絶縁膜、Hfを含む第3のゲート絶縁膜を積層し、その上に金属膜からなるゲート電極を形成し、次いでp型半導体領域300上の、第1のゲート絶縁膜,第2のゲート絶縁膜,第3のゲート絶縁膜,及びゲート電極の積層構造を、水素拡散防止膜350で被覆した後、水素雰囲気で熱処理を施す。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】寄生容量を低減しつつ、トランジスタが形成される半導体層に歪応力を与える。

【解決手段】半導体層3に形成されたコレクタ層3aの表面および裏面にストレス印加層5を形成し、ストレス印加層5を介して埋め込み絶縁層6上に配置されたベース層9をコレクタ層3aの側壁に選択的に形成し、ベース層9の側壁を絶縁膜10から露出させる開口部12を形成し、開口部12を介してベース層9の側壁に接続されたエミッタ層13aを埋め込み絶縁層6上に形成する。

(もっと読む)

半導体装置

【課題】ゲートパルスストレスによる耐圧劣化およびしきい値電圧の変動を抑制できる半導体装置を提供する。

【解決手段】ゲート電極GEは、ソース領域およびドリフト領域DRに挟まれる領域上に絶縁層FOを介在して形成されている。フィールドプレートFPは、ゲート電極GEおよびドリフト領域DR上を延在し、かつゲート電極GEに電気的に接続されている。ダミー導電層DCは、フィールドプレートFPとドリフト領域DRとの間において絶縁層FO上に形成され、かつソース領域に電気的に接続されている。

(もっと読む)

半導体装置とその製造方法

【課題】

メタルゲートを有するpチャネルMISトランジスタとメタルゲートを有するnチャネルMISトランジスタとを、少ない工程数で形成する。

【解決手段】

半導体装置は、シリコン層を有する半導体基板と、半導体基板に画定されたn型活性領域とp型活性領域と、n型活性領域の上方に形成され、酸化シリコンより高い誘電率を有し、表面にAlを含有する第1高誘電率ゲート絶縁膜と、p型活性領域の上方に形成され、酸化シリコンより高い誘電率を有する第2高誘電率ゲート絶縁膜と、第1高誘電率ゲート絶縁膜および第2高誘電率ゲート絶縁膜の各々の上に形成され、nチャネルトランジスタに適した仕事関数を有する金属又は金属化合物を含む材料で形成された、第1ゲート電極および第2ゲート電極と、を有することを特徴とする。

(もっと読む)

高アスペクト比プラグの充填方法

【課題】高アスペクト比を有するプラグを充填する方法を提供する。

【解決手段】高アスペクト比を有するプラグを充填する本発明の方法においては、核形成層を、バイアの側壁上ではなく、バイアの底に形成する。プラグ充填はバイアの底からトップへの方向であり、側壁から内側へではない。得られるプラグは、無ボイドであり、継ぎ目無しである。

(もっと読む)

半導体装置

【課題】薄膜トランジスタにおいて、ソース/ドレイン領域へのコンタクトの方法を改良することにより、配線抵抗を減らす。

【解決手段】酸化珪素膜上の第1及び第2のシリサイド、チャネル形成領域、ソース領域及びドレイン領域を有する結晶性珪素膜と、チャネル形成領域上のゲイト絶縁膜と、ゲイト絶縁膜上のゲイト電極と、ゲイト電極の側面に設けられた側壁と、第1のシリサイドに接して設けられた第1の金属配線と、第2のシリサイドに接して設けられた第2の金属配線と、を有し、第1のシリサイドは、ソース領域の上面の一部及び側面に設けられ、第2のシリサイドは、ドレイン領域の上面の一部及び側面に設けられ、第1の金属配線と第2の金属配線は同一金属膜をエッチングして形成された構造であり、第1及び第2のシリサイドは、金属膜に用いられる金属を用いて形成されたシリサイドである。

(もっと読む)

半導体装置の製造方法

【課題】段差上に被覆された被エッチング膜を大幅にオーバーエッチングすることなく、エッチング残渣を除去することができるとともに、下地酸化膜を薄膜化することができる半導体装置の製造方法を提供する。

【解決手段】配線パターンが形成された半導体基板上に酸化膜を被覆する工程と、酸化膜上に導電材料の被エッチング膜を被覆する工程と、炭素を含まず硫黄を含む化合物を添加して、被エッチング膜を酸化膜に対して選択性を持たせつつプラズマエッチングしてパターニングする工程とを含む。

(もっと読む)

電界効果トランジスタ

【課題】低いゲートリーク電流と低オン抵抗との同時に実現する。

【解決手段】InGaAsを主要な材料とするチャネル層と、AlGaAsを主要な材料とするショットキー層と、InGaPを主要な材料とするストッパ層と、ショットキー層の表面を露出するリセスを挟んで配置された第1領域と第2領域とを含むキャップ層と、キャップ層の上に設けられたソース/ドレイン電極と、リセスによって露出されたショットキー層の表面に設けられたゲート電極とを具備する電界効果トランジスタを構成する。ここで、キャップ層は、Si不純物を含む第1SiドープGaAsキャップ層と、第1SiドープGaAsキャップ層よりも低濃度のSi不純物を含む第2SiドープGaAsキャップ層と、第2SiドープGaAsキャップ層とストッパ層との間の層に設けられ、ポテンシャルバリアの上昇を抑制するバリア上昇抑制領域を備えるものとする。

(もっと読む)

ヘテロ接合電界効果トランジスタおよびその製造方法

【課題】ソース電極およびドレイン電極のn+層領域と2DEGチャネルとの接触抵抗を低減したヘテロ接合電界効果トランジスタを提供する。

【解決手段】基板上に設けられた電子走行層と、電子走行層の上に設けられた電子供給層と、ソース電極およびドレイン電極のそれぞれに対応して電子供給層に設けられたトレンチと、を有し、トレンチの底面が電子走行層と電子供給層の界面であるヘテロ接合から所定の距離だけ離れている構成である。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の絶縁膜の上に形成される金属配線または金属電極の接着力を向上させる。

【解決手段】窒化タングステン6bをタングステン6cの側面にまで設けて、タングステン6cと窒化タングステン6bとが接触している面積を増やす。ゲート絶縁膜2上に、ゲート絶縁膜2との接着力が強いポリシリコンサイドウォール5を配置する。タングステン6cの側面にある窒化タングステン6bにはポリシリコンサイドウォール5を密着させる。

(もっと読む)

半導体装置及びその製造方法

【課題】配線層間の正常な電気的導通が取れている半導体装置を提供することを課題とする。

【解決手段】基板上又は基板の表面層に少なくとも2層の配線層を備え、前記2層の配線層の内、下層配線層がシリコンからなる際に、前記下層配線層と上層配線層間に炭化珪素層を備えたことを特徴とする半導体装置により上記課題を解決する。

(もっと読む)

半導体装置およびその製造方法

【課題】ショットキー障壁の高さおよび幅を容易に制御でき、短チャネル効果を効果的に抑制できる半導体装置を提供する。

【解決手段】シリコン基板1と接してショットキー接合を形成するソース領域10,ドレイン領域11と、上記シリコン基板1とソース領域10との境界が露出する部分およびシリコン基板1とドレイン領域11との境界が露出する部分を被覆するように設けられた絶縁層を備える。上記絶縁層は、シリコン基板1とソース領域10との境界およびシリコン基板1とドレイン領域11との境界を跨ぐように、シリコン基板1とソース領域10に接すると共にシリコン基板1とドレイン領域11に接する固定電荷を含む領域8を有する。上記固定電荷は、熱平衡状態において荷電している。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】導電層が基板の内部深くにまで達することを回避して、浅いソース・ドレイン領域を形成することを可能とし、微細化に適した半導体装置及びその製造方法を得る。

【解決手段】シリコン基板1の上面内にエクステンション5を形成した後、シリコン酸化膜30を全面に堆積し、シリコン酸化膜30上にシリコン窒化膜31を、シリコン窒化膜31上にシリコン酸化膜32をそれぞれ堆積し、シリコン酸化膜32、シリコン窒化膜31及びシリコン酸化膜30をこの順にエッチングしてサイドウォール36を形成する。不純物領域13を形成し、シリコン酸化膜に対して選択性を有する条件下でシリコン成長を行うことにより、シリコン成長層15,16,37を形成する。コバルト17を全面に堆積した後、熱処理を行うことにより、コバルトシリサイドを形成する。その後、未反応のコバルト17を除去する。

(もっと読む)

集積回路

【課題】従来構造において二酸化シリコンのごく薄い層で起こる問題を回避しながら、特徴サイズを小さくして、集積化/極小化を増加させるような、ゲート誘電体構造とその製造方法を提供する。

【解決手段】基板とゲート電極との間に形成された、誘電体材料層を有するゲートスタック構造と、その製造方法を提供し、この誘電体材料層は、2.5nm以下の電気的厚さを有し、そして二酸化シリコン以外の、少なくとも1つの層を有する。基板上に誘電体材料層を堆積し、この誘電体材料層の上に直接導電層を堆積することにより形成する。

(もっと読む)

電界効果型トランジスタ

【課題】ドレイン電極からのホールリークが防止された横型のFETを提供することを課題とする。

【解決手段】基板の表面上に形成された第1導電型のチャネル層と、前記チャネル層上に形成されたソース電極、ドレイン電極及びゲート電極とを備え、前記ソース電極及びドレイン電極を前記チャネル層とオーミックコンタクトさせて電界効果型トランジスタを構成し、前記ドレイン電極の下部の前記チャネル層に第1導電型の拡散領域を備え、前記拡散領域が、式(1)Ns≧ε×Vmax/(q×t)(式中、εは前記チャネル層の誘電率[F/m]、Vmaxは前記電界効果型トランジスタの仕様最大電圧[V]、qは電荷量(1.609×10-19)[C]、tは前記基板の表面から前記拡散領域の底面までの距離[m]である)で表されるシート不純物濃度Ns[cm-2]を有していることを特徴とする電界効果型トランジスタにより上記課題を解決する。

(もっと読む)

半導体装置

【課題】熱的安定性がある一方、密着性が悪くならない程度の仕事関数を有する金属膜または金属化合物よりなる膜をゲート電極として使用した場合に、しきい値電圧を低く抑制できる半導体装置を提供する。

【解決手段】n型MIS素子とp型MIS素子を備えるCMIS素子において、n型MIS素子には、ハフニウムアルミネート膜よりなるゲート絶縁膜9上にケイ窒化タンタル膜よりなるゲート電極10を形成する。一方、p型MIS素子には、ハフニウムアルミネート膜よりなるゲート絶縁膜9上に、酸化アルミニウム膜よりなるしきい値調整膜7を形成する。そして、このしきい値調整膜7上に、ケイ窒化タンタル膜よりなるゲート電極11を形成する。

(もっと読む)

121 - 140 / 591

[ Back to top ]