Fターム[4M104DD06]の内容

半導体の電極 (138,591) | 製造方法(特徴のあるもの) (30,582) | コンタクトホール又は電極析出部の形成 (4,254)

Fターム[4M104DD06]の下位に属するFターム

孔開け、又は絶縁膜の除去方法 (1,213)

テーパ付け (105)

段差付け (31)

孔開け、又は除去する絶縁膜の材料 (2,744)

Fターム[4M104DD06]に分類される特許

121 - 140 / 161

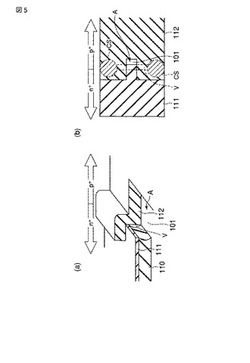

半導体装置及びその製造方法

【課題】ボイドによるコンタクトホール間のショート不良を防止する半導体装置及びその製造方法を提供すること。

【解決手段】本発明の一形態の半導体装置は、半導体基板(101)上に形成された第1及び第2のMOSFETと、前記第1のMOSFET上に形成された第1の応力膜(110)と、前記第2のMOSFET上に形成されるとともに、前記第1の応力膜の端部に積層され、前記第1の応力膜の側面との間にボイド(V)を有するように形成された第2の応力膜(112)と、前記第1の応力膜及び前記第2の応力膜上に形成される絶縁膜と、を備え、前記第1の応力膜と前記第2の応力膜との境界部に、前記第1の応力膜と前記第2の応力膜のどちらにも覆われていない領域(A)を有し、前記領域及び前記ボイドの少なくとも一部に前記絶縁膜が埋め込まれている。

(もっと読む)

リフトオフ加工方法およびリフトオフ加工装置

【課題】 加圧することにより溶剤を被加工試料に強制的に浸透せしめるリフトオフ加工方法およびリフトオフ加工装置を提供することで、従来の技法では不可能であった微細構造においてもリフトオフ加工の実施を可能とする。

【解決手段】 被加工試料Wを溶剤Gに浸し、加圧することのできる密閉容器1と、該密閉容器1内を加圧する加圧手段2とを備えてなり、被加工試料Wが溶剤Gに浸した状態で密閉容器1内に入れられ、加圧手段2を用いて加圧されるようにして、常圧では浸透できない被加工試料Wの狭隘な隙間まで溶剤Gが押し込まれ、リフトオフ試料物であるレジストマスクを膨潤させることができるようにし、微小なパターンでもリフトオフが可能となるようにしている。

(もっと読む)

半導体素子の微細パターンの形成方法

【課題】露光装備の解像限界を超えてコンタクトホールを形成する際に、ウェハ上の位置に関係なくコンタクトホールの大きさが均一になるパターン形成方法を提供する。

【解決手段】半導体素子の微細コンタクトホールを形成する際に、1)半導体基板に形成された被食刻層の上部に化学増幅型のフォトレジスト膜を形成したあと、フォトリソグラフィ工程により第1フォトレジストパターンを形成する段階と、2)前記第1フォトレジストパターンを露光マスクが取り除かれた状態で全面露光したあとベークする段階と、3)前記第1フォトレジストパターンにレジストをフロー工程に適用し、第2フォトレジストパターンを得る。

(もっと読む)

接続部構造及びその製造方法

【課題】シリサイド上に接続孔を形成する際のエッチングで、高抵抗の変質層が発生することを防止する。

【解決手段】 基板中もしくは基板上に導電層を形成する。次に、導電層上を含む基板上に第1の金属膜を形成する。次に、基板に対して熱処理を行なって第1の金属膜と導電層とを反応させ、導電層上に選択的にシリサイド膜を形成する。次に、選択CVD法によりシリサイド膜上のみに第2の金属膜を形成する。次に、第2の金属膜上を含む基板上に絶縁膜を形成する。次に、絶縁膜の所定領域を開口して、第2の金属膜に到達するコンタクトホールを形成する。次に、コンタクトホール内を洗浄して、コンタクトホール底面における第2の金属膜表面に形成された変質層を除去する。

(もっと読む)

炭化珪素ディンプル基板

第1主表面と、第1主表面に対向した第2主表面とを有する、高熱伝導性の基板を含むディンプル基板およびその製造方法。活性エピタキシャル層が、基板の第1主表面の上に形成される。ディンプルが、第2主表面から基板中を第1主表面に向かって延びるように形成される。低抵抗材料からなる電気コンタクトが、第2主表面の上とディンプルの中に形成される。低抵抗で低損失のバックコンタクトがこのように、基板を効果的なヒートシンクとして維持しながら形成される。  (もっと読む)

(もっと読む)

異なる高さのコンタクト線を有する高密度MOSFET回路を製造するための構造および方法

【課題】異なる高さのコンタクト線を有する高密度MOSFET回路を製造するための構造、方法などを提示すること。

【解決手段】このMOSFET回路は、コンタクト線(500、1300)と、コンタクト線(500、1300)の近くに位置するゲート(310、1210)とを含む。コンタクト線(500、1300)は、ゲート(310、1210)の高さよりも低い高さを含む。このMOSFET回路はさらに、ゲート(310、1210)の近くに位置するゲート・スペーサ(710、715、1610、1615)を含み、コンタクト線(500、1300)とゲート(310、1210)との間のコンタクト線(500、1300)の近くに位置するコンタクト線スペーサを含まない。

(もっと読む)

表示装置とその製造方法

【課題】TFT基板に形成する薄膜トランジスタのゲート絶縁膜を高誘電率材料を用いた厚膜とし、かつ十分なイオンをドーピングする。

【解決手段】膜厚が厚い高誘電率材料からなるゲート絶縁膜3にコンタクトホール7aを形成した後でイオンドーピングしてn+領域7を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】FUSI化されたゲート電極を有する半導体装置においても、ストレッサ膜を有効に形成できるようにして、半導体装置の電気的特性を向上できるようにする。

【解決手段】半導体装置は、半導体基板1の上に形成され、ニッケルによりフルシリサイド化されたフルシリサイドゲート電極24Aを有するn型MISトランジスタ100Aと、ニッケルによりフルシリサイド化されたフルシリサイドゲート電極24Bを有するp型MISトランジスタ100Bとを有している。半導体基板1上には、該半導体基板1におけるフルシリサイドゲート電極24Aの下側部分のチャネル領域に応力歪みを生じさせるストレッサ膜である第2の下地絶縁膜17が、少なくともフルシリサイドゲート電極24Aを覆うように形成されている。

(もっと読む)

半導体デバイス用の自己整合ショットキー接合の形成方法

半導体デバイスに対し、自己整合ショットキー接合(29)を形成する方法である。ゲートエッチング及びスペーサ形成の後、接合領域を画成する凹所を半導体基板(10)に形成し、そこに、SiGe層(22)を選択的に成長させる。その後、誘電体層(24)をゲート(14)及びSiGe層(22)の上に設け、コンタクトエッチングを行って、コンタクトホール(26)を形成してから、SiGeの材料(22)を除去して、接合領域にキャビティ(28)を作成する。最後に、キャビティ(28)を金属で満たして、接合(29)を形成する。このようにして、抵抗率が比較的低く、形状及び位置を良好に制御することができる、ショットキー接合を自己整合で形成する方法が提供される。  (もっと読む)

(もっと読む)

多層構造の形成方法

基板に電気化学エッチングまたは電気めっきを施すことにより多層構造を形成する方法。基板上にシード層を形成し、その上に主電極を形成する。主電極は、基板から複数の電気化学セルを形成するためのパターン層を有する。電圧が印加され、シード層がエッチングされて、またはシード層に材料がめっきされて形成された構造(8)の間に誘電体(9)が堆積される。誘電体層は下層構造を露出するために平坦化され、別の構造層が第1の構造層上に形成される。または、誘電体層は2層の厚さで形成され、下層構造の上端部を選択的に露出するために選択的にエッチングされる。また、複数の構造層を1工程で形成しても良い。 (もっと読む)

逆ソース/ドレイン金属コンタクトを有する電界効果トランジスタ(FET)及びその製造方法

【課題】 コンタクト間隔及び寄生容量の問題に対する解決策を提供する、改善されたFET設計を構築する。

【解決手段】 本発明は、下方の第1の誘電体層内に配置された下部と上方の第2の誘電体層内に配置された上部とを有する逆ソース/ドレイン金属コンタクトを含む電界効果トランジスタ(FET)に関する。逆ソース/ドレイン金属コンタクトの下部は、上部より大きい断面積を有する。好ましくは、逆ソース/ドレイン金属コンタクトの下部は、約0.03μm2から約3.15μm2の範囲の断面積を有し、こうした逆ソース/ドレイン金属コンタクトは、約0.001μmから約5μmの範囲の距離だけ、FETのゲート電極から間隔を空けて配置される。

(もっと読む)

自己整合パターンの製造方法およびそれを用いた半導体装置

【課題】ウエハに形成された位置合わせ用マークの位置を高精度に計測するのではなく、自己整合的に位置合わせが可能なパターン作製方法を提供すること。

【解決手段】段差を有する下地の表面に下地と異なる種類の膜を成膜する工程;形成した膜を、段差の平面部に下地の表面が露出する一方で段差の側壁部に膜が残存するようにエッチングする工程;下地及び残存する膜の全面にレジスト膜を形成し、そのレジスト膜を、開口の縁が残存する膜上に位置するように開口させる工程;及び、得られるレジスト膜の開口と残存する膜とを利用して前記下地に自己整合的にパターンを形成する工程を有することを特徴とする自己整合パターンの製造方法が提供される。

(もっと読む)

密集コンタクトホールを有する半導体デバイス

【課題】特別なエッチング工程を必要とせずに、短軸側のボーイングした個所で隣接するホールとショートするおそれのない楕円断面の密集コンタクトを有する半導体デバイスを提供する。

【解決手段】なるべく長軸21側の側面に近い方に最小分離幅26が配置され、短軸22側の側面が最小分離幅とならず、短軸22側の側面と短軸22側の側面が重ならないように、2種類の傾斜角度のホール20が4つのホール20が1セットとなった繰り返しパターンで構成されており、ボーイングの大きい短軸22側の分離間隔が大きく取られている。

(もっと読む)

半導体装置

【課題】コンタクトホールのゲート幅方向の長さを調整することで、トランジスタを被覆する応力膜の応力を調整して、工程数を増加することなく、例えばpチャネルトランジスタの移動度を低下させることなくnチャネルトランジスタの移動度の向上を可能とする。

【解決手段】半導体基板11に形成されたpチャネルトランジスタ1とnチャネルトランジスタ2とを被覆する引張応力を有する応力膜15とを備えた半導体装置3であって、pチャネルトランジスタ1のソース・ドレイン27、28領域上の応力膜15に形成された第1コンタクトホール35、36がゲート幅方向に電気的導通がとれる最小限の長さよりも長い孔で形成されて、nチャネルトランジスタ2のソース・ドレイン領域47、48上の応力膜15に形成された第2コンタクトホール55、56がゲート幅方向の長さが最小限の孔で形成されているものである。

(もっと読む)

半導体装置およびその製造方法

【課題】従来の半導体装置は、コンタクトホールの底部に段差部があり、これにより、コンタクトホール内で配線金属が分断してしまうという問題があった。

【解決手段】本発明の半導体装置は、コンタクトホールの底部にもっとも近い部分の層間膜の開口径より半導体層の開口径が大きく、その開口径の差で生じる層間膜と半導体層との間の段差部を絶縁膜で埋める構成を有している。このような構成によって、コンタクトホールの内壁の縦端面と絶縁膜の表面とが段差のない連続したなめらかな曲面を形成し、コンタクトホール内での配線金属の分断を防止する。

(もっと読む)

洗浄方法および半導体装置の製造方法

【課題】金属化合物からなるエッチング残渣または研磨残渣を、配線材料に対して選択的に除去することができる洗浄方法および半導体装置の製造方法を提供する。

【解決手段】下層配線18が設けられた基板上に、低誘電率絶縁膜20、低誘電率絶縁膜22を含む層間絶縁膜を成膜する。次いで、エッチングにより、層間絶縁膜をエッチングして、コンタクトホール24を形成するとともに、このコンタクトホール24の上部に連通する配線溝25を形成し、コンタクトホール24の底部に下層配線18を露出させる。続いて、トリアリルアミンおよびトリス(3−アミノプロピル)アミンの少なくとも1種を含有する超臨界二酸化炭素流体を、この状態の基板の表面に供給して洗浄することで、下層配線18からの金属化合物18’を含むエッチング残渣を除去する洗浄方法および半導体装置の製造方法である。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置を微細化するとともに、ゲート電極と不純物拡散領域とを接続する共通コンタクトにおける電流リークを抑制する。

【解決手段】半導体装置100は、第1のゲート電極108と、第4のソース・ドレイン領域114bと、これらを電気的に接続する共通コンタクト112と、を含む。ゲート長方向の断面において、第1のゲート電極108と第4のソース・ドレイン領域114bとが離間して設けられるとともにこれらの間の半導体基板160表面全面に素子分離絶縁膜102が形成され、第1のゲート電極108と第4のソース・ドレイン領域114bとの間の距離が、ゲート長方向の他の断面における第1のゲート電極108側壁に形成されたサイドウォールの幅と実質的に等しい。

(もっと読む)

電気光学装置、電子機器

【課題】層間を電気的に接続するために形成されるコンタクトホールを、コンタクトホールの下層に形成された端部上に形成するに際し、コンタクトホールの形成に起因する層間の電気的な接続の切断を確実に防止できる構造を有する電気光学装置を提供する。

【解決手段】TFT基板10に成膜されるとともに、スペースh1を有する段部150が少なくとも一部に形成された走査線11と、走査線11上に積層された下地絶縁膜12と、下地絶縁膜12上に積層された半導体膜1と、半導体膜1上に積層された層間絶縁膜41と、層間絶縁膜41の段部150の上方に、層間絶縁膜41を貫通するよう形成されたコンタクトホール81と、を具備し、コンタクトホール81は、段部150の端部11tから、平面的に下地絶縁膜12の膜厚以上離間した段部150のスペースh1の位置上に形成されていることを特徴とする。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】電界効果型トランジスタが形成される半導体層の結晶性の劣化を抑制しつつ、電界効果型トランジスタが形成される半導体層下に低抵抗化されたバックゲート電極を配置する。

【解決手段】単結晶半導体基板11上には埋め込み酸化膜12が形成され、埋め込み酸化膜12上には、バックゲート電極を構成する第1単結晶半導体層13が形成されている。さらに、第1単結晶半導体層13上には埋め込み酸化膜14が形成され、埋め込み酸化膜14上には、メサ分離された第2単結晶半導体層15a、15bが積層され、第2単結晶半導体層15a、15bの膜厚は第1単結晶半導体層13の膜厚よりも厚くするとともに、第2単結晶半導体層15a、15bにSOIトランジスタを形成する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】チップサイズの増大を抑制しつつ、絶縁体上に配置された導電型の異なる電界効果型トランジスタ下にフィールドプレートを形成する。

【解決手段】素子分離絶縁層7aにまたがるように配置されたゲート電極10aをゲート絶縁膜8a、9aをそれぞれ介して単結晶半導体層5a、6a上に形成し、ゲート電極10aを挟み込むように配置されたP型ソース層11aおよびP型ドレイン層12aを単結晶半導体層5aに形成し、ゲート電極10aを挟み込むように配置されたN型ソース層13aおよびN型ドレイン層14aを単結晶半導体層6aに形成し、ゲート電極10a、素子分離絶縁層7aおよび絶縁層4aを貫通して半導体層3aに接続された埋め込み電極15aを形成する。

(もっと読む)

121 - 140 / 161

[ Back to top ]