Fターム[4M104DD06]の内容

半導体の電極 (138,591) | 製造方法(特徴のあるもの) (30,582) | コンタクトホール又は電極析出部の形成 (4,254)

Fターム[4M104DD06]の下位に属するFターム

孔開け、又は絶縁膜の除去方法 (1,213)

テーパ付け (105)

段差付け (31)

孔開け、又は除去する絶縁膜の材料 (2,744)

Fターム[4M104DD06]に分類される特許

41 - 60 / 161

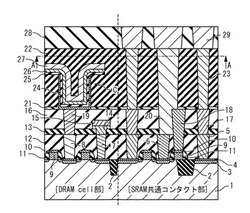

半導体装置の製造方法

【課題】ゲート電極と拡散層に接続する共通コンタクトにおけるリークを防ぐ。

【解決手段】半導体装置は、拡散層が形成された基板と、基板上に形成されたゲート電極と、基板上にゲート電極よりも高い位置まで形成された第1絶縁層と、拡散層に電気的に接続され、第1絶縁層を貫通する第1コンタクトと、ゲート電極と電気的に接続された第2コンタクトと、第1絶縁層の上に形成された第2絶縁層とを備える。第1コンタクトと第2コンタクトとは第1絶縁層の上面以上の高さにおいて電気的に接続する。ゲート電極上と拡散層上は異なるコンタクトで形成されているため、ゲート電極のサイドウォールが減少することなく、リークを防ぐことができる。

(もっと読む)

半導体装置およびその製造方法

【課題】3Dピラートランジスタにおいて、ゲートコンタクトとシリコン基板との間のショートを抑制した半導体装置及びその製造方法を得るという課題があった。

【解決手段】半導体からなる基板1と、一面1aから突出され、前記半導体からなる第1の突出部2と、一面1aに設けられた溝部1cに充填された第1の絶縁体3と、第1の突出部2に隣接して一面3aから突出され、第1の絶縁体3からなる第2の突出部4と、第1の突出部2の側面を覆うゲート絶縁膜5と、ゲート絶縁膜5を覆うゲート電極6と、第1の突出部2に設けられた上部拡散層13と、下部拡散層14と、第2の突出部4の側面を覆うとともにゲート電極6に接続された連結電極60と、第1の突出部2及び第2の突出部4を覆う層間絶縁膜と、前記層間絶縁膜を貫通して連結電極60に接するゲートコンタクト10と、を有する半導体装置及びその製造方法を用いることにより、上記課題を解決できる。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】酸化物半導体層を用いた、表示装置に代表される半導体装置において、画面サイズの大型化や高精細化に対応し、表示品質が良く、安定して動作する信頼性のよい半導体装置を提供することを課題の一つとする。

【解決手段】引き回し距離の長い配線にCuを含む導電層を用いることで、配線抵抗の増大を抑える。また、Cuを含む導電層を、TFTのチャネル領域が形成される酸化物半導体層と重ならないようにし、窒化珪素を含む絶縁層で包むことで、Cuの拡散を防ぐことができ、信頼性の良い半導体装置を作製することができる。特に、半導体装置の一態様である表示装置を大型化または高精細化しても、表示品質が良く、安定して動作させることができる。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート電極とプラグとの接続信頼性を向上することができる技術を提供する。

【解決手段】本発明では、MISFETのゲート電極G1を金属膜MF2とポリシリコン膜PF1の積層膜から構成するMIPS電極を前提とする。そして、このMIPS電極から構成されるゲート電極G1のゲート長に比べて、ゲートコンタクトホールGCNT1の開口径を大きく形成する第1特徴点と、ゲート電極G1を構成する金属膜MF2の側面に凹部CP1を形成する第2特徴点により、さらなるゲート抵抗(寄生抵抗)の低減と、ゲート電極G1とゲートプラグGPLG1との接続信頼性を向上することができる。

(もっと読む)

半導体装置及びその製造方法

【課題】フィンの下部に適切に不純物が導入された半導体装置及びその製造方法を提供する。

【解決手段】半導体装置としてのFinFET1は、基体としての半導体基板10と、半導体基板10上に形成された複数のフィン20とを有し、複数のフィン20は、第1の間隔と第1の間隔よりも間隔が狭い第2の間隔とを繰り返して形成され、第1の間隔を形成する側に面した第1の側面221の下部の不純物濃度が、第2の間隔を形成する側に面した第2の側面222の下部の不純物濃度よりも高い半導体領域を有する。

(もっと読む)

ショットキーダイオードの製造方法

【課題】所望の逆耐圧を容易に設定できるショットキーダイオードの製造方法を提供することを課題とする。

【解決手段】

本発明はショットキーダイオードの製造方法において、半導体基板を準備する工程と;前記半導体基板上に第1導電型埋め込み酸化膜及び第1導電型エピタキシャル層を形成する工程と;前記第1導電型エピタキシャル層内に、前記第1導電型埋め込み酸化膜に接続された第1導電型拡散層を形成する工程と;前記第1導電型エピタキシャル層上に絶縁膜を形成する工程と;前記絶縁膜をマスクとしたイオン注入により、ショットキーダイオード端部の電界集中を緩和する第2導電型拡散層を形成する工程と;前記第2導電型拡散層の上部に、シリサイド層(金属層)を形成する工程と;前記絶縁層内に、前記第1導電型拡散層に接続されるコンタクトを形成する工程と;前記絶縁層上に前記コンタクトと接続される配線層を形成する工程とを含むことを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の製造過程において生じるウエハ外周部分からのパーティクルの発生を防止し、十分な歩留りを実現する。

【解決手段】ウエハにゲート電極となる導電膜4、5を形成する第一工程と、導電膜4、5の中の、ウエハの外周部分に形成された導電膜4、5の上に選択的に保護膜7を形成する第二工程と、導電膜4、5の上に第一レジストパターンを形成し、前記第一レジストパターンをマスクとして導電膜4、5をエッチングすることにより、ゲート電極を形成する第三工程と、前記ゲート電極を覆う層間絶縁膜を形成する第四工程と、前記層間絶縁膜の上に第二レジストパターンを形成し、前記第二レジストパターンをマスクとして前記層間絶縁膜をエッチングすることにより、コンタクトホールを形成する第五工程と、を有する半導体装置の製造方法を提供する。

(もっと読む)

半導体装置

【課題】 DCBLストレスによるオフ耐圧性能を向上させた高耐圧LDMOSを提供する。

【解決手段】 半導体基板に形成され、トレンチにより素子分離され、ソース領域がドレイン領域で挟まれたMOSトランジスタであり、ゲート電極に接続されたメタル層ゲート配線がP型ドリフト層上を通過するように前記トレンチ外に引き出されている高耐圧LDMOS。

(もっと読む)

半導体装置の製造方法

【課題】低コストで微細パターンを形成可能な半導体装置の製造方法を提供する。

【解決手段】本発明の半導体装置の製造方法は、被加工体10上に第1のレジスト11を形成し、第1のレジスト11をパターニングする工程と、第1のレジスト11のパターニングの後、被加工体10上に第2のレジスト12を形成し、第2のレジスト12に対する選択的露光、ベーク及び現像を行い、その現像時に被加工体10上に残っている第1のレジスト11を除去するとともに、第2のレジスト12の一部を選択的に除去して、第2のレジスト12をパターニングする工程と、パターニングされた第2のレジスト12をマスクにして被加工体10を加工する工程と、を備える。

(もっと読む)

電気光学装置の製造方法、電子機器の製造方法、電気光学装置および電子機器

【課題】工程数の低減が可能な電気光学装置の製造方法および電気光学装置を提供する。

【解決手段】本発明に係る電気光学装置の製造方法は、基板の上方に、第1導電性膜を形成する工程と、第1導電性膜上に、第1導電性膜を露出する第1凹部(C2)と、平面視において第1凹部を取り囲むよう配置された第2凹部(G2)と、を有する層間絶縁膜(R1,R2)を形成する工程と、第2凹部の底面をエッチングし、第2凹部より大きい開口部を有する第3凹部(G3)を形成することにより、第2凹部の下方にオーバーハング部(OH)を形成する工程と、第1、第2および第3凹部内を含む前記層間絶縁膜上に第2導電性膜を堆積することにより、第1導電性膜と電気的に接続され、第2導電性膜よりなる画素電極を形成するとともに、第3凹部(G3)によって画素電極(PE)とその外周の第2導電性膜(30b)とを電気的に分離する工程と、を有する。

(もっと読む)

薄膜トランジスタおよび画像表示装置

【課題】本発明は、ゲート電極とソース電極間の絶縁性を向上させ、ゲート電極とソース電極間のリーク電流を低減させることにより、確実に動作する薄膜トランジスタおよび画像表示装置を提供する。

【解決手段】基板と、前記基板上に形成されたゲート電極と、ゲート絶縁膜と、前記ゲート絶縁膜上に形成された半導体層と、前記半導体層および前記ゲート絶縁膜上に形成され、前記半導体層の直上に離間して形成された第1の開口部および第2の開口部を有する保護膜と、前記保護膜上に形成され、前記保護膜の第1の開口部で前記半導体層と電気的に接続されたソース電極と、前記保護膜上に形成され、前記保護膜の第2の開口部で前記半導体層と電気的に接続されたドレイン電極を備える薄膜トランジスタにすることにより、ゲート電極とソース電極との間の絶縁膜の膜厚が実質的に増すこととなり、絶縁性を向上させることができる。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極とのコンタクトを簡便に得ることが可能な半導体装置及びその製造方法を提供すること。

【解決手段】本発明にかかる半導体装置は、縦型MOSFET50を有する半導体装置であって、半導体基板に形成され、ゲート絶縁膜3を介して縦型MOSFET50のゲート電極4aが埋め込まれている第1トレンチ(トレンチ2a)と、第1トレンチとつながって形成され、第1トレンチよりトレンチ幅の広い第2トレンチ(トレンチ2b)と、ゲート電極4aとつながって形成され、ゲート絶縁膜3を介して第2トレンチの側面に形成されたゲートパッド(ゲート電極4b)と、ゲートパッドの側面と接続するように形成され、ゲートパッドを介してゲート電極4aと電気的に接続するゲート配線11と、を備えるものである。

(もっと読む)

ショットキーバリアダイオード

【課題】 ショットキーバリアダイオードのアノード電極にワイヤボンディングする時の荷重と超音波振動による機械的ダメージにより、ダイオード特性が劣化するなどの問題が発生していた

【解決手段】 ショットキーバリアダイオードの少なくとも外部接続手段を固着する領域の下方に開口部を有する絶縁膜を設けショットキー金属層を形成し、例えばアルミニウムからなるアノード電極とアルミニウムワイヤの接合時の機械的ダメージによるダイオード特性の劣化を防止することができる。

(もっと読む)

半導体装置およびその製造方法

【課題】SiCを素材として採用することで本来得られる特性をより確実に得ることが可能な半導体装置およびその製造方法を提供する。

【解決手段】JFET1は、少なくとも上部表面14Aが炭化珪素からなるウェハ10と、上部表面14A上に形成されたゲートコンタクト電極21とを備える。ウェハ10は、上部表面14Aを含むように形成されたイオン注入領域である第1のp型領域16を含む。第1のp型領域16は、上部表面14Aを含むように配置されるベース領域16Aと、突出領域16Bとを含む。ベース領域16Aは、上部表面14Aに沿った方向における幅w1が、突出領域16Bの幅w2よりも広い。ゲートコンタクト電極21は、平面的に見てその全体が第1のp型領域16に重なるように、第1のp型領域16に接触して配置されている。

(もっと読む)

薄膜トランジスタアクティブ基板、薄膜トランジスタアクティブ基板の製造方法および電気泳動ディスプレイ

【課題】活性層を保護するとともに、ドレイン電極と画素電極との電気的導通がとれるように保護層を設けた有機トランジスタアクティブ基板を提供する。

【解決手段】薄膜トランジスタアクティブ基板は、基板107上に、ゲート電極101、ゲート絶縁膜108、ソース電極102、ドレイン電極103、活性層109が形成されてなる薄膜トランジスタ上に、保護層としての層間絶縁膜110および画素電極104が形成されてなる。トランジスタ部と上部電極(画素電極104)は層間絶縁膜110に設けられたスルーホール111を介して電気的に導通されてなる。層間絶縁膜110は、樹脂と無機または有機フィラーとを含有し、これらの樹脂と無機または有機フィラーは、EG(エチレングリコール)に、あるいはEGとアルコール溶剤とを組み合わせてなる溶剤に、溶解または分散が可能な樹脂またはフィラーである。

(もっと読む)

Ti膜の成膜方法および成膜装置、ならびに記憶媒体

【課題】CVDによりTi膜を成膜する際に、より低抵抗でかつ抵抗のばらつきが小さいTi膜を成膜することができ、プラズマダメージを小さくすることができるTi膜の成膜方法を提供すること。

【解決手段】チャンバ内にシリコンウエハを配置し、TiCl4ガスおよびH2ガスを含む処理ガスを導入しつつチャンバ内にプラズマを生成し、そのプラズマにより処理ガスの反応を促進してシリコンウエハ上にTi膜を成膜するにあたり、チャンバ内にシリコンウエハが配置された状態でTiCl4ガスを導入した後、チャンバ内にプラズマを生成する。

(もっと読む)

表示装置及びその製造方法

【課題】CVD装置への出し入れ回数を減らした表示装置の製造方法および表示装置を提供すること。

【解決手段】本発明にかかる表示装置の製造方法は、絶縁基板上に第1の電極膜と第2の電極膜とを含む導電層、第1の絶縁層、半導体膜、第2の絶縁層および保護層を形成する工程と、半導体膜の上方の第1の領域に配置される所定の厚さの第1のレジスト膜と、第2の電極膜の上方の第2の領域に配置される開口部と、それら以外の領域に配置される厚い第2のレジスト膜と、を保護層上に形成する工程と、第2の領域下をエッチングする工程と、第1のレジスト膜をアッシングにより除去する工程と、第1の領域下に半導体膜に達する第1の孔を形成し、かつ第2の領域下に第2の電極膜に達する第2の孔を形成する工程と、第2のレジスト膜を除去する工程と、半導体膜および第2の電極膜と接続される配線を形成する工程と、を含む。

(もっと読む)

ハードマスク及び二重露光により形成される半導体デバイスのコンタクト及びビア

【解決手段】

コンタクト要素がハードマスク(233)に基いて形成されてよく、ハードマスク(233)は、第1のレジストマスク(210)に基いて及び第2のレジストマスク(211)に基いて、コンタクト要素の最終的な設計寸法を代表し得る適切な交差区域(234)を画定するようにパターニングされてよい。その結果、横方向寸法の少なくとも一方は2つのレジストマスクの各々における非臨界的寸法として選択され得るので、それほど制限的ではない制約を伴うフォトリソグラフィプロセスに基いてレジストマスクの各々を形成することができる。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】ゲート絶縁膜破壊が抑制された半導体装置を提供する。

【解決手段】ゲート電極給電用シリコンピラー5の表面を覆うゲート電極8と重なる位置に設けられたコンタクトホール13を備え、コンタクトホール13には、コンタクトホール13の底部から少なくともゲート電極8の上面よりも上方まで充填されたゲートリフトポリシリコン14と、ゲートリフトポリシリコン14上に配置されたゲートコンタクト15とが設けられていることを特徴とする半導体装置を採用する。

(もっと読む)

成膜方法

【課題】結晶粒径が均一な金属シリサイド膜、特にチタンシリサイド膜を形成することができる成膜方法を提供すること。

【解決手段】被処理体1のSi含有部分上の自然酸化膜を除去する工程と、被処理体1の自然酸化膜が除去されたSi含有部分上に金属シリサイド膜4を形成する工程とを具備し、金属シリサイド膜4を形成する工程は、最初にプラズマを生成せずに、成膜しようとする金属シリサイド中の金属を含有する金属含有原料ガスを所定時間供給して金属−シリコン結合を生じさせ(ii)、次いで金属含有原料ガスを供給しつつプラズマを生成して当該金属からなる金属膜を成膜し、その際の金属膜とSi含有部分との反応により金属シリサイド膜を形成する(iii)。

(もっと読む)

41 - 60 / 161

[ Back to top ]