Fターム[4M104DD06]の内容

半導体の電極 (138,591) | 製造方法(特徴のあるもの) (30,582) | コンタクトホール又は電極析出部の形成 (4,254)

Fターム[4M104DD06]の下位に属するFターム

孔開け、又は絶縁膜の除去方法 (1,213)

テーパ付け (105)

段差付け (31)

孔開け、又は除去する絶縁膜の材料 (2,744)

Fターム[4M104DD06]に分類される特許

141 - 160 / 161

半導体装置およびその製造方法

【課題】 1.5以上の高アスペクト比である微細ホールに対しても、金属配線膜を埋め込むことができるように、ホールへの金属配線膜の埋め込み性を従来よりも向上させる。

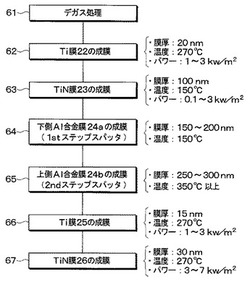

【解決手段】 TiN膜の成膜工程63で、スパッタにより、ホールの内壁に沿ってTiN膜を成膜する。このとき、成膜温度を、従来よりも低温の150℃とすることで、アモルファス構造のTiN膜を形成する。その後、スパッタ工程64、65で、アモルファス構造のTiN膜の表面上にAl合金膜を形成することで、TiN膜を下地とした状態で、Al合金膜をコンタクトホールの内部に埋め込む。このように、Al合金膜の下地となるTiN膜をアモルファス構造にすることで、TiN膜の表面エネルギーを大きくし、TiN膜のAl合金膜に対する濡れ性を従来よりも向上させることができ、ホールへのAl合金膜の埋め込み性を従来よりも向上させることができる。

(もっと読む)

半導体装置

【課題】 キャリアの移動度特性を良化させたまま応力付与膜に対してホールを設けることができるようにする。

【解決手段】 nMOSトランジスタTrのソース/ドレイン領域5を覆うように応力付与膜7が形成されている。この応力付与膜7には、開口部4が設けられている。この開口部は、ソース/ドレイン領域5に対する電気的な接続領域(コンタクトプラグの形成領域)に対してnMOSトランジスタTrのチャネル領域内を移動するキャリアの伝播方向に平行な方向に対して長く形成されている。

(もっと読む)

半導体装置の製造方法

【課題】 特性や信頼性に優れた半導体装置を作製することが可能な製造方法を提供する。

【解決手段】 Si基板上のゲート形成予定領域にダミーゲートを形成する工程と、このダミーゲートの両側に対応する領域のSi基板内に不純物を導入し熱処理によってこの不純物を活性化することによりソース・ドレイン領域23、25を形成する工程と、ダミーゲートの側壁を取り囲む絶縁膜24、26を形成する工程と、ダミーゲートを除去して開口部を22a形成する工程と、この開口部が形成された領域又はその下部領域にSiGe層28を形成する工程と、開口部に露出しているSiGe層上にゲート絶縁膜29を介してゲート電極30、31を形成する工程とを有する。

(もっと読む)

膜パターンの形成方法、半導体装置、電気光学装置、及び電子機器

【課題】 バンクに撥液化処理を行う際の、機能膜へのダメージを解消した膜パターンの形成方法と、これによって得られた膜パターンを備えた半導体装置、電気光学装置、及び電子機器を提供する。

【解決手段】 基板Pに設けられたゲート絶縁膜28(機能膜)上に機能液を配置して膜パターンを形成する方法である。基板Pにゲート絶縁膜28を設け、ゲート絶縁膜28上にポリシラザン液、ポリシラン液またはポリシロキサン液のいずれかを塗布し乾燥してバンク膜31を形成する。そして、マスクMを用いてバンク膜31を選択的に露光し、バンク膜31に撥液処理を施す。バンク膜31を現像処理することでゲート絶縁膜28を露出させ、パターン形成領域を区画するバンクを形成する。パターン形成領域に前記機能液を配置し、膜パターンを形成する。少なくとも、バンク膜31に撥液処理を施す工程は、バンク膜31を現像処理しバンクを形成する工程より前の工程で行う。

(もっと読む)

半導体装置およびその製造方法

【課題】 容量素子と拡散層との接続安定性を向上させる。

【解決手段】 半導体装置100は、DRAM部102を含み、DRAM部102に、シリコン基板101内に形成された第1拡散層108と、メタル上部電極128と、容量絶縁膜126と、メタル下部電極124とからなり、シリコン基板101上に形成されたMIM容量122と、第1拡散層108と、メタル下部電極124とを電気的に接続する第1の接続プラグと、を含む。第1の接続プラグは、第1シリコンプラグ112と、第1シリコンプラグ112の上部に接して設けられた第1シリサイド層146とから構成されるとともに、上面がメタル下部電極124に接して設けられ、MIM容量122に接続されている。

(もっと読む)

薄膜トランジスタの製造方法、薄膜トランジスタ、集積回路、および液晶表示装置

【課題】 レジストを完全に貫通するコンタクトホールを形成することにある。

【解決手段】 薄膜トランジスタの製造方法は、いずれも、光源からの光線をマスクを介してガラス基板のレジストに照射した後、該レジストを現像して前記レジストにコンタクトホールを形成することを含み、前記光線としてi線を用いる。

(もっと読む)

薄膜トランジスタを用いた液晶表示装置及びその製造方法

【課題】薄膜トランジスタを用いた液晶表示装置及びその製造方法において、生産工程を簡素化すると共に、ソース配線とゲート配線の配線抵抗の増加を防ぐ。

【解決手段】絶縁基板11上に形成された第1の光透過型感光性樹脂12の開口部に、ゲート電極13とソース配線201’と画素コンタクト層21’とを形成する。これらの上にゲート絶縁膜14と半導体層15とオーミックコンタクト層(n+半導体層)16と保護膜17を形成する。さらに、第2の光透過型感光性樹脂12’の開口部に、ソース電極19とドレイン電極19’と画素電極21とを形成する。また、第2の光透過型感光性樹脂の開口部に形成されるクロス部接続配線は、ソース配線又はゲート配線と同じく、インクジェット塗布された銀微粒子を含有するインクが焼成されてできた焼成銀である。

(もっと読む)

接触形成前に実施する表面の下処理法

【課題】熱伝導性に優れた半導体材料を使用可能で、生産性に優れた半導体デバイスの製造方法を提供する。

【解決手段】リン化インジウム材料に高濃度のシリコンをドーピングしたサブコレクタ層12上にパッシベーション層14が形成される。パッシベーション層14の一部をエッチングにより除去して接触領域を露出させる。露出させた接触領域にエネルギー照射を行い、エネルギー照射を行った部分に低抵抗のオーム接触金属51を堆積する。その後、フォトレジスト21、22を、フォトレジスト22上に堆積した金属51と共に除去する。エネルギー照射としては、不活性材料を使用したスパッタリング処理、化学的に活性を有するイオンを使用したスパッタリング処理、イオンミリング、及びプラズマエッチングのうちのいずれかを利用できる。

(もっと読む)

炭化珪素においてビアを形成する方法、及び得られるデバイスと回路

望ましくないインダクタンスを引き起こし得るワイヤーボンディングを排除する、炭化珪素基板上で集積回路を作製する方法。該方法は、炭化珪素基板の表面上のエピタキシャル層において半導体デバイスを作成し、該エピタキシャル層の最上位表面上においてデバイスのための少なくとも1つの金属コンタクトを作製することを含む。次に、実質的に透明になるまで、基板の反対側の表面を研削及び研磨する。次に、該方法は、炭化珪素基板の該研磨された表面をマスキングして、エピタキシャル層の最上位表面上にあるデバイス金属コンタクトとは反対側に存在する少なくとも1つのビアのために所定の位置を画成する工程;所望のビアをエッチングする工程を含む。第1のエッチング工程は、エッチングがエピタキシャル層に達するまで、所望のマスキングされた場所の炭化珪素基板を貫通させてエッチングする。第2のエッチング工程は、エピタキシャル層を貫通させてデバイスコンタクトまでエッチングする。最後に、ビアをメタライズして、基板の第一表面から、金属コンタクト及び基板の第二表面上にあるデバイスに至る導電経路を提供する。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】 半導体装置製造においてにおいて、界面準位を低減するための手段として、水素を含む雰囲気中での熱処理が採用されているが、金属配線のバリアメタル層にチタンを使用した場合、チタンが水素を吸着するために、水素熱処理を行っても界面準位が低減しない問題があった。本発明では、バリアメタルにチタンを含む膜を使用した場合であっても、界面準位を低減することができる半導体装置の製造方法を提案する。

【解決手段】 シリコン基板上に、層間絶縁膜を形成する工程と、バリアメタル層にチタンを含む金属配線を形成する工程有する半導体装置の製造方法において、前記層間絶縁膜を形成する工程の後で、かつ前記バリアメタル層にチタンを含む金属配線を形成する工程の前に、水素を含む雰囲気での熱処理を行うこととした。

(もっと読む)

ヘテロ接合半導体装置及びその製造方法

【課題】 半導体層間の接合の端面におけるリーク電流を抑え、かつ、水分の侵入や放熱不足の問題を解消できるパッシベーション膜を備えたヘテロ接合半導体装置及びその製造方法を提供すること。

【解決手段】 半絶縁性基板1の上にメサ構造に加工した半導体層2〜6を形成する。エミッタメサおよびベース・コレクタメサの端部に凹部11および12を形成し、これらの凹部にそれぞれ絶縁性有機膜13および14を形成して、エミッタ層5の端面とベース層4との界面、およびベース層4とコレクタ層3との界面を絶縁性有機膜で被覆する。さらに、半導体層2〜6を被覆する緻密な無機パッシベーション膜15を、例えばプラズマCVD法による窒化シリコン膜によって形成し、開口部に電極7〜9を形成する。HBT10では、接合の端面が絶縁性有機膜13および14によって被覆されているので、接合部にプラズマダメージが生じることはない。

(もっと読む)

薄膜パターン形成方法、半導体装置、電気光学装置、及び電子機器

【課題】 薄膜形成領域の断面全域に機能液を充填することにより、形成される薄膜の機能を実現するために充分な断面積と必要な断面形状を有する薄膜を形成することができる、薄膜パターン形成方法、半導体装置、電気光学装置、及び電子機器を実現する。

【解決手段】 薄膜パターン形成方法は、第1の薄膜を構成する材料を含む機能液に対して親液性を有する第2の薄膜を形成するステップと、第2の薄膜の表面に、機能液に対する撥液性を付与する処理を行うステップと、第2の薄膜の一部を取り除いて、第1の薄膜のパターン形状を規定する凹部を形成するステップと、凹部に向けて機能液を吐出するステップと、凹部に吐出された機能液を乾燥させて第1の薄膜を形成するステップとを有する。半導体装置の回路配線は、上記薄膜パターン形成方法を用いて形成されており、電気光学装置は当該半導体装置を備え、電子機器は上記電気光学装置を備える。

(もっと読む)

半導体装置及びその製造方法

【課題】ボイドに起因するコンタクトプラグ同士の短絡を防止し、且つコンタクト抵抗の上昇や接触不良を抑制する。

【解決手段】半導体基板11に接続されたコンタクトプラグ13を収容する層間絶縁膜12上に形成された配線層15a,15bの側壁を覆うサイドウォール絶縁膜16、配線層及びサイドウォール絶縁膜16を覆う層間絶縁膜17上に容量素子31、層間絶縁膜17を貫通し、コンタクトプラグ13と容量素子の電極を接続するコンタクトプラグ29とを備えた半導体装置10において、プラグ29を、少なくとも一部の側壁がサイドウォール絶縁膜16と自己整合的に形成されたコンタクトホール19内に、プラグ13上に順次に堆積された第1と第2の導電膜20,22で構成し、第1の導電膜をコンタクトホール19の側壁と接して形成するとともに、第2の導電膜をコンタクトホール19の側壁上に形成されたサイドウォール絶縁膜21の内部に形成する。

(もっと読む)

半導体装置の製造方法

【課題】 ゲート電極上に形成するコンタクトホールの底面の金属膜の表面が酸化されるのを抑制する。

【解決手段】 基板上コンタクトホール19a、19bと、底面に金属膜7aを露出させたゲート電極上コンタクトホール19cとを形成した後、基板上コンタクトホール19a、19bの底面に露出したシリコン基板1にそれぞれ不純物を注入してN型イオン注入層21、P型イオン注入層23を形成する。その後、基板上コンタクトホール19a、19bおよびゲート電極上コンタクトホール19cが埋め込まれない膜厚で、これらのコンタクトホールの内面に金属酸化防止膜24を形成する。そして、熱処理により不純物を活性化させた後に、それぞれのコンタクトホールの底面の金属酸化防止膜24を除去する。

このように形成することにより、上記熱処理において金属膜7aの表面が酸化されるのを抑制することができる。

(もっと読む)

半導体デバイスの製造方法およびこのような方法で得られる半導体デバイス

本発明は、半導体ボディ(1)と基板(2)とを有し、少なくとも1つの半導体素子(3)を備える半導体デバイス(10)の製造に関し、この半導体デバイスは、少なくとも1つの接続領域(4)と、接続領域に接続された、上に位置する帯状の接続導体(5)と、を備え、この接続領域および接続導体は、両方とも誘電体に凹設され、第1材料の誘電体領域(6)が、半導体ボディ(1)の、接続領域(4)が形成される位置に設けられ、その後、誘電体領域(6)は、第1材料とは異なる第2材料の誘電体層(7)で被覆され、この誘電体層には、帯状の接続導体(5)が形成される位置に帯状の凹部(7A)が設けられ、この凹部は、誘電体領域(6)に重なり、かつ前記誘電体領域まで延び、凹部(7A)の形成と誘電体領域(6)の除去の後、接続領域(4)が、誘電体領域(6)の除去により作られた空間(6A)に導電性材料を堆積することにより形成され、接続導体(5)が、凹部(7A)に導電性材料を堆積することにより形成される。本発明によると、第1材料には、有機材料が用いられ、第2材料には、この有機材料より高い分解温度を有する材料が用いられ、誘電体領域(6)は、有機材料の分解温度より高く、第2材料の分解温度よりは低い温度で加熱することにより除去される。本発明に係る方法は、非常にシンプルであり、第2材料を任意に選択することにより、得られるデバイス(10)に高い平面性をもたらすことができる。誘電体領域(4)には、好ましくはフォトレジストが用いられ、誘電体層(7)には、好ましくはSILKまたはSOG材料などの液体材料が用いられ、これは、加熱により固体状に変換することができる。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】ボディコンタクトを有するSOIデバイスにおいて、ボディコンタクトとボディ領域との間に所望の抵抗値を持たせると共に、当該抵抗値のばらつきを抑制する。

【解決手段】SOI層3におけるコンタクト61との接続部分(即ち、素子分離絶縁膜41の下)に、不純物濃度の高いP+領域を形成せずに、SOI層3とボディコンタクト61とをショットキー接合させる。また、ボディコンタクト61の表面にはバリアメタル61aが形成されており、ボディコンタクト61とSOI層3との間に、バリアメタル61aとSOI層3とが反応したシリサイド70が形成される。

(もっと読む)

半導体装置におけるセルフアラインドコンタクトを形成する製造方法

【課題】半導体装置におけるセルフアラインドコンタクトを形成する製造方法であって、基板のコアエリアとターミネーションエリアの一部分まで拡張してトレンチをエッチングで形成する方法を提供する。

【解決手段】第一の酸化物はトレンチの壁部に隣接した前記基板上に生成される。ポリシリコン層は前記コアエリアと前記ターミネーションエリアに蒸着される。このポリシリコン層は、前記コアエリアの前記トレンチの一部分にゲート領域を形成するように選択的にエッチングされる。このポリシリコン層のエッチングは、また、前記ゲートインターコネクト領域の第一部分を前記ターミネーションエリアの前記トレンチ部分に形成し、ゲートインターコネクト領域の第二部分を前記ターミネーションエリアにおける前記トレンチの外側に形成する。

(もっと読む)

電気的な構成要素と該構成要素の電気的な接続導体とを有するシステム並びに該システムを製造する方法

本発明は、少なくとも1つの電気的な接触面(20)を有する少なくとも1つの電気的な構成要素(2)と、該構成要素(2)の前記接触面(20)を電気的に接触させるための少なくとも1つの電気的な接続導体(3)と、前記構成要素(2)の上に配置された少なくとも1つの絶縁層(4)とを有し、該絶縁層(4)が該絶縁層(4)の厚さ方向でこれを貫通する少なくとも1つの開口(42)を有し、該開口(42)が前記構成要素(2)の接触面(20)に向き合って配置されており、前記絶縁層(4)が前記開口(42)を制限する側面(43)を有し、前記電気的な接続導体(3)が前記側面(43)に配置された少なくとも1つの金属化層(30)を有しているシステムに関する。該システムは、前記金属化層(30)が前記接触面(20)に対し斜めに配向されていることを特徴としている。斜めに配向された金属化層によっては、前記絶縁層の上に配置された前記接続導体の区分と前記絶縁層と前記構成要素とが互いに機械的にかなり結合される。有利には金属化層は数μmの厚さを有している。機械的な減結合によって、前記接続導体と前記絶縁体と前記構成要素とは、熱的な膨張係数の異なる材料から成っていることができる。本発明は特に、出力半導体構成要素を大きな面積で電気的に接触させるために使用される。  (もっと読む)

(もっと読む)

配線基板の製造方法、半導体装置及びめっき装置

【課題】 導体層の研磨中に導体層の剥がれを防止できる配線基板の製造方法を提供することを目的とする。

【解決手段】 基板10の一方の面10aに少なくとも孔10bを形成する工程と、基板10の一方の面10a上、他方の面10e上及び側面10f上と、孔10bの内面上とに、めっき給電層14を形成する工程と、電解めっきにより、めっき給電層14を介して、基板10の一方の面10a上、他方の面10e上及び側面10f上に形成され、かつ孔10bを埋め込む金属層18を形成する工程と、金属層18を研磨することにより、孔10bに金属層18が埋め込まれた金属層のパターン17a,17bを形成する工程とを有する。

(もっと読む)

半導体装置とその製造方法

【課題】 微細トランジスタと高耐圧トランジスタの線幅バラツキを低減する。

【解決手段】 P型の半導体基板1上の段差部を境にしてP型ウエル2及びN型ウエル3が形成されたものにおいて、段差低部に形成される前記P型ウエル2上に第1線幅を有する第1のトランジスタ(微細トランジスタ)が形成され、段差高部に形成される前記N型ウエル3上に第1のトランジスタよりも線幅の太い第2線幅を有する第2のトランジスタ(高耐圧トランジスタ)が形成されていることを特徴とする。

(もっと読む)

141 - 160 / 161

[ Back to top ]