Fターム[4M104DD16]の内容

半導体の電極 (138,591) | 製造方法(特徴のあるもの) (30,582) | コンタクトホール又は電極析出部の形成 (4,254) | 孔開け、又は除去する絶縁膜の材料 (2,744) | 酸化Si (1,154)

Fターム[4M104DD16]に分類される特許

21 - 40 / 1,154

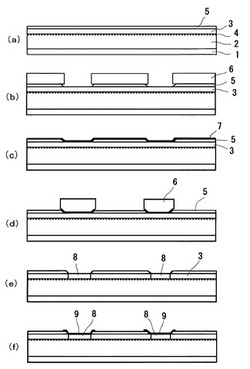

窒化物半導体装置の製造方法

【課題】低温の加熱処理によって、コンタクト抵抗の低いオーミック電極を形成することができる方法を提供する。

【解決手段】窒化物半導体層のオーミック電極形成領域に、インジウムあるいはゲルマニウムのような低融点金属7を積層し、低融点金属の融点近傍の低温で加熱処理することにより、窒化物半導体層中に低融点金属が拡散させ、合金層8を形成することによりオーミック接触を形成する。窒化物半導体層表面に残るインジウムあるいはゲルマニウムを除去した後、配線のための金属層9を形成する。

(もっと読む)

半導体装置およびその作製方法

【課題】酸化物半導体を含み、高速動作が可能なトランジスタを提供する。または、該トランジスタを含む信頼性の高い半導体装置を提供する。

【解決手段】下地絶縁層の溝に埋め込まれた電極層上に、一対の低抵抗領域及びチャネル形成領域を含む酸化物半導体層を設ける。チャネル形成領域は、サイドウォールを側壁に有するゲート電極層と重なる位置に形成される。溝は、深い領域と浅い領域を有し、サイドウォールは、浅い領域と重なり、配線との接続は、深い領域と重なる。

(もっと読む)

半導体装置の製造方法

【課題】電気的特性が良好な半導体装置の製造方法を提供する。

【解決手段】実施形態に係る半導体装置の製造方法は、シリコン基板の上面に、第1方向に延びる複数の凹部を形成する工程と、前記凹部が形成された前記シリコン基板を、弗素又は弗化物を含むガス中でプラズマ処理する工程と、前記プラズマ処理する工程の後で、前記シリコン基板を、水素を含むガス中で熱処理する工程と、前記熱処理する工程の後で、前記凹部の内面上に絶縁膜を形成する工程と、前記絶縁膜上に導電膜を形成する工程と、を備える。

(もっと読む)

半導体装置の作製方法及び半導体装置

【課題】微細な構造であっても高い電気特性を有するトランジスタを歩留まりよく提供する。該トランジスタを含む半導体装置においても、高性能化、高信頼性化、及び高生産化を達成する。

【解決手段】酸化物半導体層と電気的に接続するソース電極層及びドレイン電極層を、酸化物半導体層上のゲート絶縁層及び絶縁層の開口を埋め込むように設ける。ソース電極層を設けるための開口とドレイン電極層を設けるための開口は、それぞれ異なるマスクを用いた個別のエッチング処理によって形成される。これにより、ソース電極層(またはドレイン電極層)と酸化物半導体層が接する領域と、ゲート電極層との距離を十分に縮小することができる。また、酸化物半導体層の下に第1の電極層および第2の電極層を設けてコンタクト抵抗の低減を図る。

(もっと読む)

半導体装置およびその作製方法

【課題】ノーマリーオフの電気特性を有し、オン電流の高い、酸化物半導体膜を用いたトランジスタを提供する。また、該トランジスタを用いた高速動作が可能な半導体装置を提供する。

【解決手段】下地絶縁膜と、下地絶縁膜上に設けられた酸化物半導体膜と、酸化物半導体膜上に設けられたゲート絶縁膜と、ゲート絶縁膜を介して酸化物半導体膜と重畳して設けられたゲート電極と、少なくともゲート電極を覆って設けられた、開口部を有する層間絶縁膜と、層間絶縁膜上に設けられ、開口部を介して酸化物半導体膜と接する配線と、を有し、少なくとも酸化物半導体膜と配線とが接する領域の、下地絶縁膜および酸化物半導体膜の間に、絶縁膜および絶縁膜上に設けられたバッファ層を有する半導体装置である。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】Cu配線内における空孔の集中を抑制することでCu配線内でのボイドの形成を抑え、例えば2層間配線系におけるビア接続部等における、いわゆるストレスマイグレーションと呼ばれる断線等の配線不良の発生が抑制される半導体装置の製造方法を提供する。

【解決手段】ダマシン配線構造を有する半導体装置の製造方法において、配線形成後に被処理基板を加熱および除熱する熱サイクル工程を行う、半導体装置の製造方法が提供される。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】信頼性の高い半導体装置を提供する。半導体装置を歩留まりよく作製し、高生産化を達成する。

【解決手段】ゲート電極層、ゲート絶縁膜、インジウムを含む酸化物半導体膜、ゲート電極層と重畳する酸化物半導体膜上に接する絶縁層が順に積層され、酸化物半導体膜及び絶縁層に接するソース電極層及びドレイン電極層が設けられたトランジスタを有する半導体装置において、絶縁層表面における塩素濃度を1×1019/cm3以下とし、かつインジウム濃度を2×1019/cm3以下とする。

(もっと読む)

半導体装置

【課題】微細化しても高いオン電流を得ることができるトランジスタを用いた、半導体装置。

【解決手段】トランジスタが、絶縁表面上の一対の第1導電膜と、一対の第1導電膜上の半導体膜と、一対の第1導電膜にそれぞれ接続されている一対の第2導電膜と、半導体膜上の絶縁膜と、絶縁膜上において、半導体膜と重なる位置に設けられた第3導電膜とを有する。また、半導体膜上における第3導電膜の端部と、一対の第2導電膜が設けられた領域とは、離隔している。

(もっと読む)

低順方向電圧降下過渡電圧サプレッサーおよび製造方法

【課題】一般にショットキー整流器は定格逆電圧での逆漏れが高く、一方PN構造ダイオードは逆漏れがすくない。両者を並列接続し、低順方向電圧降下を与えると共に、両端で逆サージを保護する。

【解決手段】低逆電圧定格化PNダイオード、および独立集積回路素子におけるPNダイオードに電気的に並列接続した高逆電圧定格化ショットキー整流器からなる低順方向電圧降下過渡電圧サプレッサー。

(もっと読む)

半導体装置及びその製造方法

【課題】プラグが微細化しても埋め込み不良が生じることなく、低コストで形成することができ、さらに種々の半導体装置に適用可能であるプラグ及びその形成技術を提供する。

【解決手段】本発明の実施形態にかかる半導体装置の製造方法は、半導体基板上に酸化シリコン膜を形成し、酸化シリコン膜にビアを形成し、ビア内側に密着層を形成し、密着層上にシリコン層を形成し、タングステンを含むガスをシリコン層と反応させることにより、ビアに埋め込まれたタングステン膜を形成する。

(もっと読む)

半導体装置およびその作製方法

【課題】酸化物半導体膜と金属膜との接触抵抗を低減する。オン特性の優れた酸化物半導体膜を用いたトランジスタを提供する。高速動作が可能な半導体装置を提供する。

【解決手段】酸化物半導体膜を用いたトランジスタにおいて、酸化物半導体膜に窒素プラズマ処理を行うことで酸化物半導体膜を構成する酸素の一部が窒素に置換された酸窒化領域を形成し、該酸窒化領域に接して金属膜を形成する。該酸窒化領域は酸化物半導体膜の他の領域と比べ低抵抗となり、また、接触する金属膜との界面に高抵抗の金属酸化物を形成しにくい。

(もっと読む)

半導体装置およびその製造方法

【課題】閾値電圧を制度良く制御することが可能な半導体装置及びその製造方法を提供する。

【解決手段】基板10上に、窒化物半導体からなるチャネル層14と、チャネル層14よりもバンドギャップエネルギーの大きい第1窒化物半導体層16と、を順次形成する工程と、第1窒化物半導体層16上であって、ゲート電極26を形成すべき領域にダミーゲートを形成する工程と、ダミーゲートを形成した後、第1窒化物半導体層16上のダミーゲート以外の領域に、チャネル層14のバンドギャップエネルギー以上の大きさのバンドギャップエネルギーを有する第2窒化物半導体層18を再成長する工程と、ダミーゲートを除去した後、ダミーゲートを除去した領域の第1窒化物半導体層16上にゲート電極26を形成する工程と、を有する半導体装置の製造方法。

(もっと読む)

化合物半導体装置の製造方法

【課題】化合物半導体積層構造上の絶縁膜に所期の微細な開口を形成するも、リーク電流を抑止した信頼性の高い高耐圧の化合物半導体装置を実現する。

【解決手段】化合物半導体積層構造2上にパッシベーション膜6を形成し、パッシベーション膜6の電極形成予定位置をドライエッチングにより薄化し、パッシベーション膜6の薄化された部位6aをウェットエッチングにより貫通して開口6bを形成し、この開口6bを電極材料で埋め込むように、パッシベーション膜6上にゲート電極7を形成する。

(もっと読む)

半導体装置および半導体装置の作製方法

【課題】半導体装置の特性を損なうことがない半導体装置およびその作製方法を提供する。

【解決手段】酸化物半導体層を含むトランジスタ(半導体装置)において、電極層を酸化物半導体層の下部に接して形成し、不純物を添加する処理により酸化物半導体層に自己整合的にチャネル形成領域と、チャネル形成領域を挟むように一対の低抵抗領域を形成する。また、電極層および低抵抗領域と電気的に接続する配線層を絶縁層の開口を介して設ける。

(もっと読む)

半導体装置

【課題】トランジスタのオン特性を向上させて、半導体装置の高速応答、高速駆動を実現する際に、信頼性の高い構成を提供する。

【解決手段】ソース電極層405a及びドレイン電極層405bの端部と、ゲート電極層401の端部とを重畳させ、更に酸化物半導体層403のチャネル形成領域となる領域に対して、ゲート電極層401を確実に重畳させることで、トランジスタのオン特性を向上させる。また、絶縁層491中に埋め込み導電層を形成し、埋め込み導電層481a,481bと、ソース電極層405a及びドレイン電極層405bとの接触面積を大きくとることで、トランジスタのコンタクト抵抗を低減する。ゲート絶縁層402のカバレッジ不良を抑制することで、酸化物半導体層403を薄膜化し、トランジスタの微細化を実現する。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】電極と化合物半導体層との界面に電極材料が到達することを抑止し、ゲート特性の劣化を防止した信頼性の高い高耐圧の化合物半導体装置を提供する。

【解決手段】化合物半導体積層構造2と、化合物半導体積層構造2上に形成され、貫通口6aを有するパッシベーション膜6と、貫通口6aを埋め込むようにパッシベーション膜6上に形成されたゲート電極7とを有しており、ゲート電極7は、相異なる結晶配列の結晶粒界101が形成されており、結晶粒界101の起点が貫通口6aから離間したパッシベーション膜6の平坦面上に位置する。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極膜に注入したイオンがチャネル領域に達してMISFETの電気特性に影響を与えていた。

【解決手段】半導体基板の主面上にゲート絶縁膜を介して形成されるとともに、第1導電型となる不純物を含んだシリコンを主体とする第1ゲート電極膜と、前記第1ゲート電極膜上に形成されるとともに、酸素及び窒素のうち一方又は両方を含んだシリコンを主体とする介在層と、前記第1ゲート電極膜上に前記介在層を介して形成されるとともに、前記第1導電型となる不純物を含んだシリコンを主体とする第2ゲート電極膜と、を含む電界効果トランジスタを有する。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】オン抵抗を増加させることなく、ノーマリーオフとなる半導体装置を提供する。

【解決手段】基板11の上に、第1の半導体層14、第2の半導体層15及びp型の不純物元素が含まれている半導体キャップ層16を順次形成する工程と、前記半導体キャップ層を形成した後、開口部を有する誘電体層21を形成する工程と、前記開口部において露出している前記半導体キャップ層の上に、p型の不純物元素が含まれている第3の半導体層17を形成する工程と、前記第3の半導体層の上にゲート電極31を形成する工程と、を有することを特徴とする半導体装置の製造方法により上記課題を解決する。

(もっと読む)

窒化物半導体装置およびその製造方法

【課題】窒化物半導体層とオーミック電極とのコンタクト抵抗を低減できる窒化物半導体装置を提供する。

【解決手段】Si基板10上に形成されたアンドープGaN層1,アンドープAlGaN層2と、アンドープGaN層1,アンドープAlGaN層2上に形成されたTi/Al/TiNからなるオーミック電極(ソース電極11,ドレイン電極12)とを備える。上記オーミック電極中の窒素濃度を1×1016cm−3以上かつ1×1020cm−3以下とする。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】動作電圧の高電圧化を図るも、デバイス特性の劣化(化学的・物理的変化)を確実に抑止し、高耐圧及び高出力を実現する信頼性の高い化合物半導体装置を得る。

【解決手段】本発明による化合物半導体装置では、化合物半導体層2上を均質な同一材料(ここではSiN)からなり誘電率が一様な第1の保護膜6が覆い、第1の保護膜6の開口6aの一端部分に酸素を含有する保護部、ここでは当該一端部分を覆う酸化膜である第2の保護膜7aが形成されており、開口6aを埋め込み第2の保護膜7aを包含するオーバーハング形状のゲート電極8が形成される。

(もっと読む)

21 - 40 / 1,154

[ Back to top ]