Fターム[4M104DD16]の内容

半導体の電極 (138,591) | 製造方法(特徴のあるもの) (30,582) | コンタクトホール又は電極析出部の形成 (4,254) | 孔開け、又は除去する絶縁膜の材料 (2,744) | 酸化Si (1,154)

Fターム[4M104DD16]に分類される特許

161 - 180 / 1,154

半導体装置の作製方法

【課題】不良を抑制しつつ微細化を達成する半導体装置の作製方法を提供することを目的の一とする。

【解決手段】絶縁表面上に、酸化物半導体層と、酸化物半導体層と接するソース電極およびドレイン電極と、を形成し、ソース電極上およびドレイン電極上にそれぞれ絶縁層を形成し、酸化物半導体層、ソース電極、ドレイン電極および絶縁層上にゲート絶縁層を形成し、ゲート絶縁層上に導電層を形成し、導電層を覆うように絶縁膜を形成し、導電層におけるソース電極またはドレイン電極と重畳する領域の少なくとも一部が露出するように絶縁膜を加工し、導電層の露出した領域をエッチングして、ソース電極とドレイン電極に挟まれた領域の少なくとも一部と重畳するゲート電極を自己整合的に形成する半導体装置の作製方法である。

(もっと読む)

半導体装置の製造方法

【課題】基板に形成される第1の膜と第2の膜との重なり量を精度良く算出する。

【解決手段】半導体装置の製造方法は、基板の第1の領域及び第2の領域に第1の膜を形成する工程と、第2の領域の第1の膜の幅を測定する工程と、基板の第2の領域及び第3の領域に第2の膜を形成する工程と、第2の領域の第2の膜の幅及び第2の領域の第1の膜と第2の膜との距離を測定する工程と、第2の領域における第1の膜の幅の測定値、第2の膜の幅の測定値、第1の膜と第2の膜との距離の測定値及び第1の膜と第2の膜とに関する設計値に基づいて、第1の領域における第1の膜と第3の領域における第2の膜との重なり量を算出する工程と、を備える。

(もっと読む)

半導体装置及びその製造方法

【課題】トランジスタの耐圧を向上し得る半導体装置及びその製造方法を提供する。

【解決手段】半導体基板10上にゲート絶縁膜16を介して形成されたゲート電極18cと、ゲート電極の一方の側の半導体基板に形成された第1導電型のドレイン領域54aと、ゲート電極の他方の側の半導体基板に形成された第1導電型のソース領域54bと、ドレイン領域からゲート電極の直下に達する第1導電型の第1の不純物領域56と、ソース領域と第1の不純物領域との間に形成された、第1導電型と反対の第2導電型の第2の不純物領域58とを有し、ゲート電極は、第1導電型の第1の部分48aと、第1の部分の一方の側に位置する第2導電型の第2の部分48bとを含み、ゲート電極の第2の部分内に、下端がゲート絶縁膜に接する絶縁層24が埋め込まれている。

(もっと読む)

半導体装置の製造方法

【課題】高誘電率ゲート絶縁膜とメタルゲート電極を有するCMISFETを備えた半導体装置において、nチャネル型MISFETおよびpチャネル型MISFETのしきい値電圧の上昇を防ぐことができる技術を提供する。

【解決手段】CMISFETのしきい値を調整する目的で、高誘電率ゲート絶縁膜であるHf含有絶縁膜5に希土類元素またはアルミニウムを導入する際に、酸素をほとんど含まないランタン膜からなるしきい値調整層8bおよび酸素をほとんど含まないアルミニウム膜からなるしきい値調整層8aをnMIS形成領域1BおよびpMIS形成領域1AのHf含有絶縁膜5上にそれぞれ形成する。これにより、しきい値調整層8aおよびしきい値調整層8bからHf含有絶縁膜5および半導体基板1の主面に酸素が拡散することを防ぐ。

(もっと読む)

半導体装置及びその製造方法

【課題】信頼性の高い半導体装置を高い製造歩留まりで提供し得る半導体装置及びその製造方法を提供する。

【解決手段】第1応力膜38上に第1ストッパ膜39及び第2ストッパ膜40を形成する工程と、第1領域2を覆う第1マスク60をマスクとし、第1ストッパ膜をストッパとして、第2領域4内の第2ストッパ膜をエッチングするとともに、第1領域のうちの第2領域に近接する部分の第2ストッパ膜をサイドエッチングする工程と、第2ストッパ膜とエッチング特性が異なる第2応力膜42を形成する工程と、第2領域を覆い、第1領域側の端面が第2ストッパ膜上に位置する第2マスクとし、第2ストッパ膜をストッパとして、第2応力膜の一部が第1応力膜の一部及び第2ストッパ膜の一部と重なり合うように第2応力膜をエッチングする工程と、第1領域と第2領域との境界部におけるゲート配線20に達するコンタクトホールを形成する工程とを有している。

(もっと読む)

半導体装置及びその製造方法

【課題】ストレッサ膜を有する半導体装置及びその製造方法に関し、ストレッサ膜からの応力を効率よくチャネル領域に印加してMISFETの電流駆動能力を向上しうる半導体装置及びその製造方法を提供する。

【解決手段】半導体基板に、素子領域を画定する素子分離絶縁膜を形成し、素子領域上に、ゲート絶縁膜を介してゲート電極を形成し、ゲート電極の両側の半導体基板内にソース/ドレイン領域を形成し、ゲート電極及びソース/ドレイン領域が形成された半導体基板上に第1の絶縁膜を形成し、素子分離絶縁膜の端部に生じた窪み内に第1の絶縁膜が残存するように第1の絶縁膜をエッチバックし、半導体基板上に、半導体基板の表面に平行な方向に応力を印加する第2の絶縁膜を形成する。

(もっと読む)

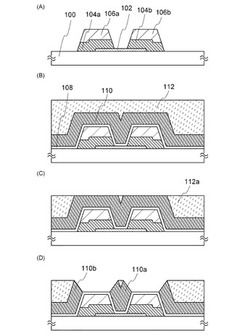

トップゲート型薄膜トランジスタ及びこれを備えた表示装置

【課題】酸化物半導体層のチャネル領域の、水素拡散による低抵抗化を抑制するトップゲート型酸化物半導体TFT及びこれを備えた表示装置を提供する。

【解決手段】基板の上に、ソース電極層と、ドレイン電極層と、酸化物半導体層と、ゲート絶縁層と、In、Ga、Zn、Snの少なくとも1種類の元素を含むアモルファス酸化物半導体からなるゲート電極層と、水素を含む保護層と、を有し、ゲート絶縁層は酸化物半導体層のチャネル領域の上に形成され、ゲート電極層はゲート絶縁層の上に形成され、保護層はゲート電極層の上に形成されていることを特徴とするトップゲート型薄膜トランジスタ。

(もっと読む)

薄膜トランジスタとその製造方法、薄膜トランジスタアレイとその製造方法、及び、ディスプレイ装置

【課題】製造工程において半導体膜の膜質を低下させることなくその性能を維持し、少ない工程数によって、かつ、製造上の歩留まり及びスループットの優れた構造を有する薄膜トランジスタ及びその製造方法等を提供する。

【解決手段】薄膜トランジスタ100は、酸化物半導体膜120を有し、当該酸化物半導体膜120は、各薄膜半導体毎に、ゲート電極160下及び隣接された薄膜トランジスタ間とにそれぞれ形成された第1領域121及び122と、ソース電極140及びドレイン電極150下であって第1領域121の前記水平方向におけるそれぞれの両端に並設されており、ソース電極140及びドレイン電極150にそれぞれ電気的に接続され、かつ、非駆動時に前記第1領域121及び122より低抵抗である第2領域123及び124と、を有している。

(もっと読む)

半導体装置およびその製造方法

【課題】素子面積の増大を抑制しつつ、信頼性に優れた構造を有する半導体装置およびその製造方法を提供する。

【解決手段】半導体装置100は、化合物半導体基板12と、化合物半導体基板12に埋め込まれた埋込電極と、を備え、化合物半導体基板12の主面に溝22、24が設けられており、少なくとも溝22、24の側壁上に設けられた第一の金属膜10a、10bと、少なくとも溝22、24の底面上に設けられており、第一の金属膜10a、10bと異種材料で構成される第二の金属膜9a、9bと、を含む積層体により溝22、24を埋め込むことで、上記埋込電極が構成されており、第一の金属膜10a、10bのフェルミエネルギーは化合物半導体基板12の真性フェルミエネルギーと異なり、第二の金属膜9a、9bのフェルミエネルギーは化合物半導体基板12の真性フェルミエネルギーと異なる。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】接続孔の内壁に絶縁膜を形成することにより、接続孔の径を小さくする場合において、接続孔内に導電膜を十分に埋め込むことができるようにする。

【解決手段】接続孔210,220の内壁上に絶縁性の第1膜300を形成し、接続孔210,220の径を細らせる。次いで、第1膜300が形成された接続孔210,220内に、第2膜50を埋め込む。次いで、絶縁膜200の表層を、CMP法を用いて除去する。次いで、接続孔210,220から第2膜50を除去する。次いで、接続孔210,220の第1膜300上および接続孔210,220の底面上にバリアメタル膜330を形成し、さらに接続孔210,220内に導電膜からなるコンタクト310,320を埋め込む。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の性能を向上させる。

【解決手段】素子分離領域13は、溝11に埋め込まれた酸化シリコン膜からなり、上部が半導体基板1から突出しており、半導体基板1から突出している部分の素子分離領域13の側壁上に、窒化シリコンまたは酸窒化シリコンからなる側壁絶縁膜SW1が形成されている。MISFETのゲート絶縁膜は、ハフニウムと酸素と低しきい値化用の元素とを主成分として含有するHf含有絶縁膜5からなり、メタルゲート電極であるゲート電極GEは、活性領域14、側壁絶縁膜SW1および素子分離領域13上に延在している。低しきい値化用の元素は、nチャネル型MISFETの場合は希土類またはMgであり、pチャネル型MISFETの場合は、Al、TiまたはTaである。

(もっと読む)

半導体装置

【課題】2DEGをチャンネルとして用いる半導体装置において、不純物イオンの侵入による悪影響を排除する。

【解決手段】第1の半導体層である電子走行層11上に、第2の半導体層である電子供給層12が形成されている。これらの界面(ヘテロ接合界面)における電子走行層11側に、2次元電子ガス(2DEG)層13が形成される。ソース電極14からドレイン電極15の間の2DEG層13が形成された領域がこの半導体装置10におけるチャンネル領域となる。このチャンネル領域上の絶縁層17上において、第1のフィールドプレート18が形成されている。すなわち、第1のフィールドプレート18は、2つの主電極のうちの一方から他方に達するチャンネル領域上を覆うように形成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体集積回路の高集積化と機能素子の高性能化とを同時に実現する。

【解決手段】実施形態に係わる半導体装置は、半導体基板1の表面領域に配置されるスイッチ素子3,4と、下面がスイッチ素子3,4に接続されるコンタクトプラグ6と、コンタクトプラグ6の上面の直上に配置される機能素子7とを備える。コンタクトプラグ6の上面の最大表面粗さは、0.2nm以下である。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】異なるチャネル長のトランジスタを有し、かつ、コンタクト抵抗の増加およびオン電流の減少を防止できる半導体装置の提供。

【解決手段】ピラートランジスタTr1と、前記ピラートランジスタTr1の下部拡散層7aへ信号または電源を供給するとともに、ポリシリコン層10aからの固相拡散し、下部拡散層7aを形成することにより、前記ピラートランジスタTr1のチャネル長d1を厚みにより制御する前記ポリシリコン層10aと、を具備してなることを特徴とする。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】CMOS回路を構成するnチャネルMISFETとpチャネルMISFETの両者において、キャリア移動度を高めて高い性能を実現する半導体装置を提供する。

【解決手段】半導体基板の第1領域及び第2領域において第1ゲート絶縁膜及び第1ゲート電極(16,17)を形成し、第1ゲート電極の両側部における半導体基板中にソースドレイン領域を形成し、ソースドレイン領域の導電性不純物を活性化し、第1ゲート電極を被覆して全面に半導体基板に応力を印加するストレスライナー膜(27,28)を形成し、少なくとも第1領域に形成された部分のストレスライナー膜は残しながら第2領域における第1ゲート電極の上部部分のストレスライナー膜を除去し、第2領域における第1ゲート電極の上部を露出させて第1ゲート電極を全て除去して第2ゲート電極形成用溝Tを形成し、第2ゲート電極形成用溝内に第2ゲート電極(31,32)を形成する。

(もっと読む)

パターン形成方法および積層構造体

【課題】所望のパターンが形成でき、製造工程の迅速化を図ることが可能なパターン形成方法を提供する。

【解決手段】本実施形態のパターン形成方法は、下地10の上に第1の膜11を選択的に形成する工程と、前記第1の膜11および前記第1の膜に覆われていない前記下地10の上に、第2の膜13を形成する工程と、前記第2の膜13の平均結晶粒径を前記第2の膜13の膜厚以上に調整する工程と、前記第1の膜11のエッチャントを前記第2の膜13の表面に晒し、前記第1の膜11の上に形成された前記第2の膜13を前記下地上から選択的に除去する工程と、を備える。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】縦型のトランジスタにおいてゲートからシリサイドの位置を精度よく制御できるようにする。

【解決手段】柱状半導体14の中央部には、その周囲を囲むように、ゲート絶縁膜9が形成され、さらに、ゲート絶縁膜9の周囲を囲むように、ゲート層6が形成されている。この柱状半導体14の中央部、ゲート絶縁膜9、ゲート層6により、MIS構造が形成されている。ゲート層6の上下には、第1絶縁膜4が形成されている。第1絶縁膜4は、柱状半導体14にも接している。柱状半導体14の側面には、シリサイド18及びn型拡散層(不純物領域)19が形成されている。シリサイド18は、第1絶縁膜4によってセルフ・アラインされた位置に形成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】サリサイド構造を有するMIS型電界効果トランジスタにおいて、ゲート電極とソース・ドレインコンタクトとの間の短絡を防止する。

【解決手段】ゲート電極175上にはシリサイド層230が形成されている。シリサイド層230の上面は、シリサイド層230の中央から両端に向けて低くなっており、当該両端におけるシリサイド層230の上面の高さは、オフセットスペーサ180の高さ以下である。

(もっと読む)

半導体素子の製造方法

【課題】本発明は、疎水化処理を要することなく、フォトリソグラフィー技術による酸化シリコン膜のパターニングが可能な半導体素子の製造方法を提供することを目的とする。

【解決手段】本発明は、基板上に形成された酸化シリコン膜上に機能層を形成する機能層形成工程と、上記機能層上に第1フォトレジストを塗布し、フォトリソグラフィー法により上記機能層および上記酸化シリコン膜をパターニングし、上記第1フォトレジストを除去する第1パターニング工程と、パターニングされた上記機能層上に第2フォトレジストを塗布し、フォトリソグラフィー法により上記機能層をさらにパターニングし、上記第2フォトレジストを除去する第2パターニング工程とを有し、上記機能層と上記第1フォトレジストおよび上記第2フォトレジストとの接触角が20度以下であることを特徴とする半導体素子の製造方法を提供する。

(もっと読む)

半導体装置の製造方法

【課題】ゲート電極に形成された研磨後のキャップ絶縁膜の厚さを容易に推定できる半導体装置の製造方法を提供する。

【解決手段】半導体装置形成領域に第1の導電膜よりなるゲート電極15、半導体装置非形成領域に絶縁膜形成部16、及び絶縁膜よりなり、ゲート電極の上面及び絶縁膜形成部の上面を覆うキャップ絶縁膜17を形成し、次いで、キャップ絶縁膜を覆う層間絶縁膜28を形成し、次いで、キャップ絶縁膜上に形成された層間絶縁膜にゲート電極の延在方向と交差する方向に延在する溝47を形成すると共に、溝の下方に位置する層間絶縁膜に不純物拡散層を露出するコンタクトホール22,23を形成し、次いで、溝及びコンタクトホールを埋め込む第2の導電膜51を形成し、次いで、CMP法により第2の導電膜を研磨することでコンタクトプラグを形成し、その後、絶縁膜形成部に形成されたキャップ絶縁膜の厚さを測定する。

(もっと読む)

161 - 180 / 1,154

[ Back to top ]