Fターム[4M104DD16]の内容

半導体の電極 (138,591) | 製造方法(特徴のあるもの) (30,582) | コンタクトホール又は電極析出部の形成 (4,254) | 孔開け、又は除去する絶縁膜の材料 (2,744) | 酸化Si (1,154)

Fターム[4M104DD16]に分類される特許

141 - 160 / 1,154

半導体装置の製造方法

【課題】本発明は半導体装置に関する。

【解決手段】本発明は、半導体基板上のセル領域のセルトランジスタ上の層間膜を貫通してコンタクトプラグが形成され、周辺回路領域のトランジスタ上の層間膜を貫通してコンタクトプラグが形成されてなる半導体装置の製造方法であり、セルトランジスタ上の層間膜にコンタクトホールを形成し、その底部側にシリコン膜の下部導電プラグを形成する工程と、その上に金属膜を積層して積層構造のセルコンタクトプラグを形成する工程と、周辺回路用トランジスタ上の層間膜にコンタクトホールを形成し、その内部に金属膜を形成してコンタクトプラグを形成する工程とを具備し、前記セル領域のコンタクトホール内のシリコン膜上に金属膜を形成する工程と前記周辺回路領域のコンタクトホール内に金属膜を形成する工程を同時に行うことを特徴とする。

(もっと読む)

電極規定層を包含する窒化ガリウム材料デバイスおよびその形成方法

【課題】窒化ガリウム材料デバイスおよびその形成方法を提供する。

【解決手段】該デバイスは、電極規定層24を包含する。電極規定層は典型的にはその内部に形成されたビア26を有し、該ビア内に電極18が(少なくとも部分的に)形成される。したがって、ビアは、電極の寸法を(少なくとも部分的に)規定する。いくつかの場合において、電極規定層は、窒化ガリウム材料領域上に形成された不動態化層である。

(もっと読む)

半導体装置の製造方法

【課題】ゲート電極断線の確率を下げる。

【解決手段】半導体装置1の製造方法は、シリコン基板2の主面に絶縁体ピラー6を形成する工程と、絶縁体ピラー6の側面に保護膜12を形成する工程と、シリコン基板2の主面にシリコンピラー4を形成する工程と、シリコンピラー4の側面にゲート絶縁膜10を形成する工程と、それぞれシリコンピラー4及び絶縁体ピラー6の側面を覆い、互いに接する第1及び第2のゲート電極11,13を形成する工程とを備える。本製造方法によれば、ダミーピラーとしての絶縁体ピラー6の側面に保護膜12を形成しているので、チャネル用のシリコンピラー4をトランジスタとして加工する際にダミーピラーが削られてしまうことが防止される。したがって、ゲート電極断線の確率を下げることが可能になる。

(もっと読む)

成膜方法、成膜装置及び半導体装置の製造方法

【課題】熱CVD法によって、M(BH4)4(Mは、Zr又はHfを意味する)を原料としてM/Zr比が適正範囲内で良質なMBx膜(Mは前記と同じ意味を有し、xは1.8〜2.5の数を意味する)を成膜する。

【解決手段】ガス供給源19から、ガス供給配管15aを介してH2ガスを原料容器21内に供給する。原料容器21内では、導入されたH2ガスとの接触によって、固体原料のZr(BH4)4が気化する。そして、成膜ガスとしてのH2ガスとZr(BH4)4ガスの混合ガスが、ガス供給配管15c,15c1、シャワーヘッド11のガス拡散空間12及びガス吐出孔13を介して処理容器1内に導入され、ウエハW上の絶縁膜の表面を覆うように、ZrBx膜の薄膜が形成される。

(もっと読む)

半導体上からホットメルトエッチングレジストを剥離する改良された方法

【課題】シート抵抗率の増大およびアルミニウム電極の腐蝕を抑制する剥離剤配合物を提供する。

【解決手段】ホットメルトエッチングレジストが、半導体ウェハ上の反射防止コーティングもしくは選択的エミッタに選択的に適用される。無機酸含有エッチング剤を用いて、反射防止コーティングおよび選択的エミッタの露出部分がエッチング除去されて、半導体基体を露出させる。このホットメルトエッチングレジストは次いで、半導体の電気的一体性を悪化させないアルカリ剥離剤を用いて半導体から剥離される。次いで、露出した半導体は金属化されて、電流トラックを形成する。

(もっと読む)

薄膜トランジスタ及び液晶表示装置の作製方法

【課題】作製工程を大幅に削減し、低コストで生産性の良い液晶表示装置を提供する。消費電力が少なく、信頼性の高い液晶表示装置を提供する。

【解決手段】ゲート配線上の一部を含む半導体層のエッチングと、画素電極とドレイン電極を接続するためのコンタクトホールの形成を、同一のフォトリソグラフィ工程及びエッチング工程で行うことで、フォトリソグラフィ工程を削減する。これにより露出したゲート配線の一部を絶縁層で覆い、これに液晶層の間隔を維持するスペーサを兼ねさせる。フォトリソグラフィ工程を削減することにより、低コストで生産性の良い液晶表示装置を提供することができる。また、半導体層に酸化物半導体を用いることで、消費電力が低減され、信頼性の高い液晶表示装置を提供することができる。

(もっと読む)

ソース領域の下にp型埋込み層を備えたトランジスタ及びその作製方法

【課題】本発明は、金属半導体電界効果トランジスタ(MESFET)を提供する。

【解決手段】このMESFETは、ソース(13)とドレイン(17)とゲート(24)とを備えている。このゲート(24)を、ソース(13)とドレイン(17)の間及びn導電型チャネル層(18)上に設ける。ドレイン(17)に向かって延びている端部を備えるp導電型領域(14)をソースの下に設ける。このp導電型領域(14)をn導電型チャネル領域(18)から隔ててソース(13)に電気的に結合させる。

(もっと読む)

半導体装置

【課題】逆方向耐圧を向上させることができる半導体装置を提供する。

【解決手段】一導電型の半導体層100と、絶縁体層130と、絶縁体層中に設けられた半導体層210と、半導体層210に設けられた能動素子20と、半導体層100の前記一主面201に設けられた他の導電型の半導体領域112と、半導体領域112内に設けられた他の導電型であって半導体領域112よりも高不純物濃度の半導体領域114と、絶縁体層130に設けられたスルーホール144内に半導体領域144に接続して設けられた導電体154と、絶縁体層130上または中に設けられた導電体214であって、導電体154の周囲に設けられ、外側端部が半導体領域114よりも外側にある導電体214と、導電体154と導電体214とを接続して設けられた導電体192と、半導体層100に接続して設けられた導電体152,120と、を備える。

(もっと読む)

保護層および低損傷陥凹部を備える窒化物ベースのトランジスタならびにその製作方法

【課題】窒化物ベースの半導体チャネル層上に窒化物ベースの半導体バリア層を形成すること、および窒化物ベースの半導体バリア層のゲート領域上に保護層を形成することによって、トランジスタが製作される。

【解決手段】パターニングされたオーム性接触金属領域が、バリア層上に形成され、第1および第2のオーム性接触を形成するためにアニールされる。アニールは、保護層をゲート領域上に載せたままで実施される。バリア層のゲート領域上に、ゲート接点も形成される。ゲート領域内に保護層を有するトランジスタも形成され、バリア層の成長させたままのシート抵抗と実質的に同じシート抵抗をもつバリア層を有するトランジスタも同様である。

(もっと読む)

半導体素子および半導体素子の作製方法

【課題】ノーマリーオフ動作型の半導体素子を複雑な工程を経ることなく作製する方法を提供する。

【解決手段】半導体素子の作製方法が、下地基板の上に、少なくともGaを含む、Inx1Aly1Gaz1N(x1+y1+z1=1)なる組成の第1のIII族窒化物からなるチャネル層を形成する工程と、チャネル層の上に、少なくともAlを含む、Inx2Aly2Gaz2N(x2+y2+z2=1)なる組成の第2のIII族窒化物からなる障壁層を形成する工程と、障壁層の表面の、ソース電極およびドレイン電極の形成予定個所に対し、ソース電極およびドレイン電極を形成する工程と、障壁層の表面の、ゲート電極の形成予定個所に対し、アルゴンプラズマ処理または酸素プラズマ処理を施す工程と、プラズマ処理工程を経たゲート電極の形成予定個所にゲート電極を形成する工程と、を備えるようにする。

(もっと読む)

化合物半導体装置

【課題】窒化物化合物半導体装置において、ゲートリーク電流を抑制する。

【解決手段】化合物半導体装置20は、基板21と、前記基板上方に形成された窒化物半導体よりなるキャリア走行層22を含む半導体積層構造と、前記半導体積層構造上方に形成されたゲート電極26、ソース電極27A、ドレイン電極27Bと、前記半導体積層構造上方であって、ゲート電極とソース電極の間、及び、ゲート電極とドレイン電極との間に形成された絶縁膜28と、前記絶縁膜のうち、ゲート電極とソース電極の間、及びゲート電極とドレイン電極の間に形成された開口と、前記開口に埋め込まれたアルミナ膜29と、を備える。

(もっと読む)

半導体装置およびその製造方法

【課題】コンタクト抵抗を低減する半導体装置およびその製造方法を提供する。

【解決手段】実施の形態の半導体装置は、シリコンを含む半導体基板10上の層間絶縁膜11に形成されたコンタクトホール12の底部14に形成され、コンタクトホール12に形成されるコンタクトプラグ21と電気的に接続するニッケルシリサイド膜18を有する。このニッケルシリサイド膜18は、ニッケルシリサイド膜18とコンタクトプラグ21の界面18aが半導体基板10と層間絶縁膜11の界面10aより高い。

(もっと読む)

窒化物半導体装置およびその製造方法

【課題】窒化物半導体層の表面に形成したオーミック電極のコンタクト抵抗を低減した窒化物半導体装置およびその製造方法を提供すること。

【解決手段】第一の窒化物半導体層3と、第一の窒化物半導体層3の上に形成された第二の窒化物半導体層4と、第二の窒化物半導体層4の表面に形成されるオーミック電極としてのカソード電極6と、を備え、第二の窒化物半導体層4の表面におけるカソード電極6が形成される領域に、凹凸構造を有するコンタクト部4aが形成され、このコンタクト部4aの表面粗さ(RMS)が0.25nm以上5nm以下であり、かつコンタクト部4aの表面の酸素の組成比率が5at.%以下に設定されている。

(もっと読む)

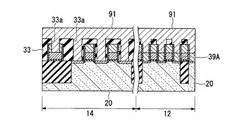

半導体装置の製造方法

【課題】隣接する活性領域の間で横方向に成長するシリコン膜が連結されることを防ぎつつ、活性領域上に十分な厚みのシリコン膜を形成可能とした半導体装置の製造方法を提供する。

【解決手段】ゲート電極6aを挟んだ両側の活性領域5上に第1のシリコン膜12aを選択的にエピタキシャル成長させる工程と、複数のワード配線層WLの各間に第1のシリコン膜12aを覆うのに十分な厚みでマスク絶縁膜を埋め込んだ後、このマスク絶縁膜を第1のシリコン膜12aの表面が露出するまでエッチングにより除去する工程と、第1のシリコン膜12a上に第2のシリコン膜12bを選択的にエピタキシャル成長させる工程とを含む。

(もっと読む)

化合物半導体デバイス

【課題】高温にさらされても、Au配線表面に析出物が発生することを抑制できる半導体デバイスの製造方法を提供する。

【解決手段】化合物半導体基板1上の、Auからなる下部配線層3aと上部配線層3bの上部を覆って、Auより薄膜応力が小さく高融点を有する金属であるタンタルあるいはチタンからなる配線被覆層5と5’をスパッタにより形成する。

(もっと読む)

炭化珪素半導体装置およびその製造方法

【課題】トレンチ内のダメージ除去を行う際に、ソース領域とソース電極とのコンタクト抵抗が増大することを抑制できるようにする。

【解決手段】n+型ソース領域4の第2領域4bについて、最表面からある程度の深さの場所については、高不純物濃度とせず、比較的低不純物濃度となるようにする。これにより、ダメージ除去工程を行ったときに、n+型ソース領域4の第2領域4bのうち比較的低不純物濃度とされる部分が若干残るか、もしくは、この部分が消失して第2領域4bのうちの高不純物濃度の部分が増速酸化されても、比較的低不純物濃度とされる部分の酸化に時間が掛かるため、増速酸化される領域が少なくなるようにできる。したがって、n+型ソース領域4の第2領域4bのうちのソース電極9とのコンタクト部が消失することを防止でき、n+型ソース領域4とソース電極9とのコンタクト抵抗の増大を抑制することが可能となる。

(もっと読む)

半導体装置およびその製造方法

【課題】コンタクト孔に埋め込まれる金属プラグの材料が層間絶縁膜に染み出すのを防止できる半導体装置を提供する。

【解決手段】隣り合う2つのメモリセル1のサイドウォール間の不純物拡散領域に電気的接続されるコンタクトプラグ40が、層間絶縁膜18を貫通して設けられている。コンタクト孔41の側壁は、層間絶縁膜18より緻密なシール膜42で覆われている。コンタクトプラグ40は、シール膜42の表面およびコンタクト孔41の底面部を覆うように形成されたバリアメタル膜43と、バリアメタル膜43に包囲された状態でコンタクト孔41内に埋め込まれた金属プラグ44とを含む。

(もっと読む)

導電材埋め込み方法及び半導体装置の製造方法

【課題】 従来の方法と比較して、短時間で凹部の全体に導電材を埋め込むことができる技術を提供する。

【解決手段】 本願に係る導電材の埋め込み方法は、半導体装置の製造過程において表面に形成される凹部22に導電材を埋め込む方法に関する。この方法は、凹部22の少なくとも底面に露出する下地層10の表面に不純物24aを定着させる不純物定着工程と、不純物24aが定着した下地層10を利用して導電材をVLS成長させて、凹部の全体に導電材を埋め込むVLS成長工程とを有する。この方法では、VLS成長によって凹部22に導電材を埋め込むため、短時間で導電材を埋め込むことができる。

(もっと読む)

半導体装置及びその製造方法

【課題】接続不良の発生を抑制することのできる、信頼性の高い半導体装置及びその製造方法を提供する。

【解決手段】半導体装置は、所定ピッチで所定の幅の素子領域が形成された半導体基板と、半導体基板上に積層された層間絶縁膜と、層間絶縁膜の上面から半導体基板の素子領域にかけて設けられ素子領域に接続される第1コンタクトとを備える。第1コンタクトは、素子領域上の層間絶縁膜に形成された素子領域の幅よりも大きい径を有するコンタクトホールと、コンタクトホールの底部に設けられ、素子領域に達する開口を有するスペーサ膜と、スペーサ膜の開口を介して素子領域に接続されるようにコンタクトホール内に埋め込まれたコンタクトプラグとを有する。

(もっと読む)

相補型金属酸化物半導体(CMOS)構造物

【課題】ゲート誘電体の上に複数のシリサイド金属ゲートが作製される相補型金属酸化物半導体集積化プロセスを提供する。

【解決手段】形成されるシリサイド金属ゲート相の変化を生じさせるポリSiゲートスタック高さの変化という欠点のないCMOSシリサイド金属ゲート集積化手法が提供される。集積化手法は、プロセスの複雑さ最小限に保ち、それによって、CMOSトランジスタの製造コストを増加させない。

(もっと読む)

141 - 160 / 1,154

[ Back to top ]