Fターム[4M104DD16]の内容

半導体の電極 (138,591) | 製造方法(特徴のあるもの) (30,582) | コンタクトホール又は電極析出部の形成 (4,254) | 孔開け、又は除去する絶縁膜の材料 (2,744) | 酸化Si (1,154)

Fターム[4M104DD16]に分類される特許

201 - 220 / 1,154

半導体装置の製造方法

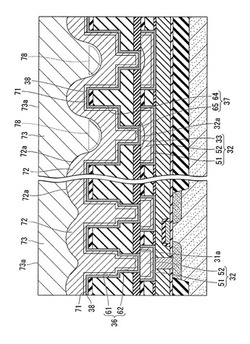

【課題】ボイド、ディッシング、及びエロージョンの発生を抑制することのできる半導体装置の製造方法を提供する。

【解決手段】絶縁膜に幅の異なる複数の開口部36,37を形成し、次いで、絶縁膜の上面、及び幅の異なる複数の開口部内にシード層38を形成し、次いで、第1の成長速度により、シード層の表面を覆う第1のめっき膜71を形成し、次いで、第1の成長速度よりも速く、かつボイドを生じさせない第2の成長速度により、第1のめっき膜の表面に第2のめっき膜72を形成し、次いで、第2の成長速度よりも速い第3の成長速度により、第2のめっき膜上に第3のめっき膜73を形成し、その後、シード層及び第1乃至第3のめっき膜のうち、絶縁膜の上面よりも上方に形成された部分を研磨により除去することで、開口部内に少なくとも第1及び第2のめっき膜よりなる導電部を形成する。

(もっと読む)

化合物半導体装置

【課題】閾値電圧の高い良好なノーマリオフ特性を有する化合物半導体装置を提供する。

【解決手段】キャリア走行層21とキャリア供給層22を有し、二次元キャリアガス層211が形成される化合物半導体層2と、化合物半導体層2上に互いに離間して配置され、二次元キャリアガス層211とオーミック接続する第1の主電極3及び第2の主電極4と、第1の主電極3と第2の主電極4間で、化合物半導体層2上に配置された金属酸化物半導体膜8と、金属酸化物半導体膜8上に配置された、金属酸化物半導体膜8に接するチタン膜又はチタンを含む化合物膜を有する制御電極5とを備える。

(もっと読む)

半導体装置及びその製造方法

【課題】工程数の増加を回避し得る半導体装置及びその製造方法を提供する。

【解決手段】低濃度ドレイン領域28hを形成するためのドーパント不純物が導入される所定領域を除く領域に、所定領域から離間するようにチャネルドープ層22dを形成する工程と、半導体基板10上にゲート絶縁膜24を介してゲート電極26dを形成する工程と、ゲート電極の一方の側の半導体基板内に低濃度ソース領域28gを形成し、ゲート電極の他方の側の半導体基板の所定領域に低濃度ドレイン領域28hを形成する工程とを有している。

(もっと読む)

半導体装置及びその製造方法

【課題】ボイドやシームが発生しにくい構造体とする。

【解決手段】本発明の半導体装置は、半導体基板101に形成された層間絶縁膜103と、層間絶縁膜103に形成されたコンタクト孔104と、コンタクト孔104を埋め込むCu膜107と、コンタクト孔104の内部の側壁に形成され、Cu膜107の下地となる金属含有下地膜13と、を備える。コンタクト孔104の開口に接続している側壁の一部を含む第一の領域11において、金属含有下地膜13は、Cu膜107との界面に金属窒化層106を有する。第一の領域11よりも半導体基板101側の側壁を含む第二の領域12において、金属含有下地膜13は、Cu膜107との界面に金属層105を有する。金属層105の表面におけるCu膜107の成膜速度は、金属窒化層106の表面におけるCu膜107の成膜速度よりも大きい。

(もっと読む)

半導体装置及びその製造方法

【課題】接合リーク電流が低減されるとともに、セル容量への書き込み・読み出しに十分な電流駆動能力を確保することが可能な半導体装置及びその製造方法を提供する。

【解決手段】半導体基板1に形成された複数の埋め込みゲート型MOSトランジスタ2を有し、半導体基板1には素子分離領域と活性領域とが形成されており、ゲートトレンチの内部に形成され、少なくとも一部がワード線として設けられるとともに、その他の残部が、活性領域を複数の素子領域に分離する素子分離として設けられる埋め込みゲート電極31A、31Bと、ソース・ドレイン拡散層15、45とが備えられ、埋め込みゲート電極31A、31Bは、上部電極31aと下部電極31bとの積層構造とされ、且つ、半導体基板1の上面側のソース・ドレイン拡散層15、45側に配置される上部電極31aが、下部電極31bに比べて、仕事関数の低いゲート材料からなる。

(もっと読む)

窒化物半導体装置

【課題】GaN系の窒化物半導体を用いたデバイスのゲートリセス量の制御性を向上することで、閾値電圧の面内均一性を向上することができる窒化物半導体装置を実現できるようにする。

【解決手段】窒化物半導体装置は、基板101上に形成された第1のGaN系半導体からなるバッファ層102と、第2のGaN系半導体からなるキャリア走行層103と、第3のGaN系半導体からなるキャリア供給層104とを備えている。キャリア供給層104の上には第1の絶縁膜105と、アルミニウムを含む第2の絶縁膜106と、第1の絶縁膜105より膜厚が厚い第3の絶縁膜107とが形成されている。ソース電極108及びドレイン電極109は第1の絶縁膜105上に形成されている。ゲート電極110は、リセス構造を含む第2の絶縁膜106及び第3の絶縁膜107上に形成されている。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】初期故障や偶発故障の発生を低減する。

【解決手段】HFET1は、下層のGaN層13およびGaN層13の一部を露出させるトレンチT1が形成された上層のAlGaN層14よりなるIII族窒化物半導体層と、III族窒化物半導体層上に形成されたゲート絶縁膜15と、ゲート絶縁膜15上に形成されたゲート電極16と、を備える。少なくともゲート絶縁膜15と接触するトレンチT1底部のGaN層13上面には、原子層ステップが形成されている。原子層ステップのテラス幅の平均値は、0.2μm以上1μm未満である。

(もっと読む)

半導体装置及びその製造方法

【課題】シェアードコンタクトを備えた半導体装置において、コンタクトホールの開口不良やコンタクト抵抗の増大を防止しつつ、接合リーク電流の発生に起因する歩留まりの低下を防止する。

【解決手段】半導体基板100におけるゲート電極103の両側にソース/ドレイン領域106が形成されている。シェアードコンタクトは、ソース/ドレイン領域106とは接続し且つゲート電極103とは接続しない下層コンタクト113と、下層コンタクト113及びゲート電極103の双方に接続する上層コンタクト118とを有する。

(もっと読む)

電子回路装置

【課題】ノーマリオフ型の炭化珪素接合FETはゲートの特性が、使い勝手が悪いという問題がある。これは、ノーマリオフを実現するためにゲート電圧が0Vでオフしていなければならず、かつ、ゲート・ソース間のpn接合に電流が流れないようにオン状態としてはゲート電圧を2.5V程度に抑える必要があるため、実質的にゲート電圧を0Vから2.5Vの間で制御しなければならないためである。従って、閾値電圧からオン状態のゲート電圧までが1Vから2V程度しかなく、ドレイン電流がゲート電圧の変化に非常に敏感であるため、ゲートの制御が難しい。

【解決手段】本願発明は、ノーマリオフ型の炭化珪素接合FETのゲートに、接合FETのゲート容量と同等か少し小さな容量を持つ素子を接続したものである。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】耐圧の異なるトランジスタが同一半導体基板上に混載されている場合においても、それらのトランジスタの性能が向上するようにストレスライナ膜を構成することが可能な半導体装置及びその製造方法を提供する。

【解決手段】半導体基板1上に混載された低耐圧トランジスタおよび高耐圧トランジスタ上に形成するストレスライナ膜11、12は、互いに膜質を異ならせることができる。ここで、ストレスライナ膜11は、低耐圧トランジスタの性能が効果的に改善され、高耐圧トランジスタの性能があまり改善されないように膜質を設定することができる。また、ストレスライナ膜11は、高耐圧トランジスタの性能が効果的に改善され、低耐圧トランジスタの性能があまり改善されないように膜質を設定することができる。

(もっと読む)

半導体装置の製造方法

【課題】ソース・ドレイン電極と半導体膜とのコンタクト不良を抑制することが可能な半導体装置等を提供する。

【解決手段】両端部30s、30dの膜厚が平坦部30cの膜厚よりも厚い半導体膜30を形成する。ゲート絶縁膜40は、両端部30s、30dが露出されるように形成される。両端部30s、30dには、ソース・ドレイン電極50s、50dとソース・ドレイン領域とを接続する中間電極50s、50dが形成され、この中間電極50s、50dまで開口するコンタクトホールが形成される。

(もっと読む)

電極構造体及びその製造方法、並びに半導体装置

【課題】精度良く形成された小型化された電極を備えた電極構造体及びその製造方法、並びに半導体装置を提供する。

【解決手段】第1の層間絶縁膜13に、第1の方向に延在する複数の第1の溝16を形成し、第1の溝16の対向する2つの側面及び底面を覆うように第1の導電膜32を形成し、第1の導電膜32が形成された複数の第1の溝16を第1の絶縁膜19で充填し、第1の層間絶縁膜13、第1の絶縁膜19、及び第1の導電膜32の上面に、第2の方向に延在する複数の開口部を有したハードマスク層33を形成し、異方性エッチング法により、複数の開口部から露出された部分の第1の絶縁膜19及び第1の導電膜32を除去することで、第1の溝16に第1の導電膜32よりなる電極を形成すると共に、第1の層間絶縁膜13に第1の溝16と交差する第2の溝17を複数形成し、ハードマスク層33を除去した後、第2の溝17を第2の絶縁膜21で充填する。

(もっと読む)

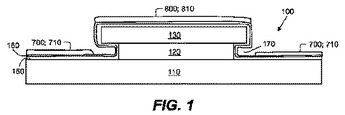

半導体装置及び電子機器

【課題】良好な特性を維持しつつ、微細化を達成した、酸化物半導体を用いた半導体装置を提供することを目的の一とする。

【解決手段】酸化物半導体層と、酸化物半導体層と接するソース電極及びドレイン電極と、酸化物半導体層と重なるゲート電極と、酸化物半導体層とゲート電極との間に設けられたゲート絶縁層と、を有し、ソース電極またはドレイン電極は、第1の導電層と、第1の導電層の端面よりチャネル長方向に伸長した領域を有する第2の導電層と、を含み、第2の導電層の伸長した領域の上に、前記伸長した領域のチャネル長方向の長さより小さいチャネル長方向の長さの底面を有するサイドウォール絶縁層を有する半導体装置である。

(もっと読む)

ショットキーバリアダイオードを備えた炭化珪素半導体装置およびその製造方法

【課題】ショットキーバリアハイトの低減とリーク電流の低減を両立する。

【解決手段】ショットキー電極4とSiCとの界面にSiOXにて構成される界面層が形成されることなく、ショットキー電極4を構成する金属の各粒子がSiCの表面において、原子配列が連続的となった格子整合した状態となるようにする。具体的には、ショットキー電極4を構成する金属の粒子構造が柱状構造ではなく粒状構造となるようにし、柱状構造となっている場合と比較して、粒子間の境界を通じて界面に酸素が取り込まれ難くなるようにすることで、SiOXが形成されないようにしてショットキー電極4を構成する金属をSiCと格子整合させる。

(もっと読む)

半導体装置およびその製造方法

【課題】微細化されたMISFETのゲート電極の加工精度を向上することができる技術を提供する。

【解決手段】シリコン上にニッケルプラチナ合金膜を形成する(S101)。そして、第1加熱処理を実施する(S102)。このとき、第1加熱処理において、加熱温度は250℃〜270℃であり、加熱時間は30秒未満である。続いて、未反応のニッケルプラチナ合金膜を除去する(S103)。その後、第2加熱処理を実施する(S104)。このとき、第2加熱処理において、加熱温度は、450℃〜600℃である。

(もっと読む)

スパッタリング用ターゲットおよび半導体装置の製造方法

【課題】スパッタリング用ターゲットから垂直方向に叩き出されるターゲット原子の個数を増大させる。

【解決手段】薄膜形成に用いられるターゲット原子Pから構成されたターゲット5において、ターゲット5から斜め方向に叩き出されたターゲット原子Pを側壁に衝突させることでターゲット原子Pがターゲット5から放出されるのを遮る凹部5aを表面に形成する。

(もっと読む)

表示装置の作製方法

【課題】液滴吐出法により吐出する液滴の着弾精度を飛躍的に向上させ、微細でかつ精度の高いパターンを基板上に直接形成することを可能にする。もって、基板の大型化に対応できる配線、導電層及び表示装置の作製方法を提供することを課題とする。また、スループットや材料の利用効率を向上させた配線、導電層及び表示装置の作製方法を提供することを課題とする。

【解決手段】液滴吐出法による液滴の吐出直前に、所望のパターンに従い基板表面上の液滴着弾位置に荷電ビームを走査し、そのすぐ後に該荷電ビームと逆符号の電荷を液滴に帯電させて吐出することによって、液滴の着弾位置の制御性を格段に向上させる。

(もっと読む)

電界効果型トランジスタ

【課題】従来の電界効果型トランジスタでは、ソース領域およびドレイン領域に形成する高濃度不純物のイオン注入工程により半導体基板表面がアモルファス化されるため、低濃度不純物拡散領域と高濃度不純物拡散領域との境界部において、活性化熱処理により結晶欠陥を誘発し、電界効果型トランジスタの信頼性を低下させる問題があった。

【解決手段】本発明の電界効果型トランジスタは、ソース領域およびドレイン領域を構成する部分の上部に高濃度不純物を含有する導電性膜を設ける。高濃度不純物のイオン注入を行う必要がないことから、この領域の半導体基板表面がアモルファス化することがない。これにより、低濃度不純物拡散領域と高濃度不純物拡散領域との境界部において、再結晶化による結晶欠陥の発生を防ぐことができる。

(もっと読む)

半導体装置及びその製造方法

【課題】マイクロローディング効果を防止しながら、上層配線となる金属配線のレイアウト制約のない構造を有する半導体装置を提供する。

【解決手段】半導体装置は、半導体基板1上に形成されたゲート絶縁膜3と、ゲート絶縁膜3の上に形成されたゲート電極4と、半導体基板1に形成された拡散層5と、半導体基板1の上に形成された絶縁膜7及び絶縁膜8と、絶縁膜及び絶縁膜8を貫通するホール9Dに埋め込まれ、側面を絶縁膜11で覆われた金属材料からなるプラグ12と、絶縁膜8を貫通しないホール10Bに埋め込まれ、絶縁膜11からなる絶縁体10Cと、絶縁膜8の上に形成され、プラグ12と電気的に接続する金属配線13Bとを備えている。

(もっと読む)

内側にへこんだ形状を含んだトランジスタを製造する方法

トランジスタを製造する方法は、導電材料層と電気絶縁材料層とを順に含んだ基板を準備する工程と、前記電気絶縁材料層上にレジスト材料層を堆積する工程と、前記レジスト材料層をパターニングして、前記電気絶縁材料層の一部を露出させる工程と、露出された前記電気絶縁材料層を除去して、前記導電材料層の一部を露出させる工程と、露出された前記導電材料層を除去し、前記導電材料層及び前記電気絶縁材料層内に凹部形状を作り出す工程と、前記基板と露出された前記電気絶縁材料層及び前記導電材料層とを第2の電気絶縁材料層で共形に被覆する工程と、前記第2の電気絶縁材料層を半導体材料層で共形に被覆する工程と、前記半導体材料層上に導電材料層を指向性堆積する工程とを含む。

(もっと読む)

(もっと読む)

201 - 220 / 1,154

[ Back to top ]