Fターム[4M104DD16]の内容

半導体の電極 (138,591) | 製造方法(特徴のあるもの) (30,582) | コンタクトホール又は電極析出部の形成 (4,254) | 孔開け、又は除去する絶縁膜の材料 (2,744) | 酸化Si (1,154)

Fターム[4M104DD16]に分類される特許

41 - 60 / 1,154

半導体装置及びその製造方法

【課題】薄型化された炭化シリコン基板による低抵抗化が可能な半導体装置及びその製造方法を提供する。

【解決手段】実施形態によれば、半導体装置は、炭化シリコン基板と、半導体層と、絶縁膜と、補強基板と、第1の電極と、第2の電極とを備えている。半導体層は、炭化シリコン基板の第2の面上に設けられ、素子領域と素子領域よりも端部側の周辺領域とを有する。絶縁膜は、半導体層の周辺領域の表面上に設けられている。補強基板は、周辺領域における絶縁膜上に設けられている。第1の電極は、炭化シリコン基板の第1の面に接して設けられている。第2の電極は、素子領域の表面に接して設けられている。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体装置のトランジスタのシリコンピラー上部に活性領域を設ける際に、エピタキシャル成長により前記シリコンピラー上部に形成されるシリコン膜の高さが、前記トランジスタ毎にばらつくことを防ぎ、前記シリコン膜への導電型ドーパントの注入深さを均一にする半導体装置の製造方法を提供する。

【解決手段】基板の主面に柱状のシリコンピラーを形成するシリコンピラー形成工程と、前記シリコンピラーを覆うように第1の絶縁膜を形成する第1絶縁膜形成工程と、前記第1の絶縁膜を上面から除去し、前記シリコンピラー上部の上面及び側面を露出させる第1絶縁膜除去工程と、前記シリコンピラー上部の上面及び側面にエピタキシャル成長法によりシリコン膜を形成するシリコン膜形成工程とを有する。

(もっと読む)

半導体装置及びその製造方法

【課題】高集積化が容易な半導体装置及びその製造方法を提供する。

【解決手段】実施形態に係る半導体装置の製造方法は、第1導電形の半導体基板の上面に複数本のトレンチを形成する工程と、前記トレンチの内面上にゲート絶縁膜を形成する工程と、前記トレンチ内の下部にゲート電極を埋め込む工程と、前記トレンチ内の上部に絶縁部材を埋め込む工程と、前記半導体基板の上層部を除去することにより、前記半導体基板の上面から前記絶縁部材を突出させる工程と、前記突出した絶縁部材を覆うように、マスク膜を形成する工程と、前記マスク膜における前記絶縁部材の側面上に形成された部分をマスクとして、前記半導体基板に不純物を注入することにより、第2導電形のキャリア排出層を形成する工程と、を備える。

(もっと読む)

半導体装置

【課題】オフリーク電流の抑制および駆動電流の増大を図ることが可能な半導体装置を提供する。

【解決手段】実施形態の半導体装置において、ゲート電極は、第1および第2のソース・ドレイン領域の間に設けられた第1リセス内に少なくとも一部がゲート絶縁膜を介して埋め込まれて第1および第2のソース・ドレイン領域よりも深い位置まで形成される。チャネルは、素子領域においてゲート絶縁膜に隣接して第1および第2のソース・ドレイン領域の間に形成される。一対の応力付与部は、素子分離領域において、ゲート電極のゲート幅方向に垂直な面内において第1および第2のソース・ドレイン領域の下部のチャネルと重複する領域に設けられ、素子分離領域の構成材料と異なる絶縁材料からなりチャネルに対してゲート幅方向の両側から応力を付与する。

(もっと読む)

半導体装置およびその製造方法

【課題】実施形態は、一括して形成することが可能なメモリセルを有し、その直下に制御回路を設けた構成を実現する半導体装置およびその製造方法を提供する。

【解決手段】実施形態は、基板上に設けられたメモリアレイと、前記基板と前記メモリアレイとの間の前記基板の表面に設けられた制御回路と、を有する半導体装置の製造方法であって、前記制御回路のp形半導体領域およびn形半導体領域を覆う絶縁層に、前記p形半導体領域に連通する第1のコンタクトホールを形成する工程と、前記第1のコンタクトホールの内部に、前記p形半導体領域に接したコンタクトプラグを形成する工程と、を備える。さらに、前記n形半導体領域に連通する第2のコンタクトホールを前記絶縁層に形成する工程と、前記コンタクトプラグと、前記第2のコンタクトホールの内部に露出した前記n形半導体領域と、に接する配線を形成する工程と、を備える。

(もっと読む)

抵抗変化型不揮発記憶装置、半導体装置及び抵抗変化型不揮発記憶装置の製造方法

【課題】安定したスイッチング動作を低コストで実行する抵抗変化型不揮発性記憶装置を提供する。

【解決手段】抵抗変化型不揮発性記憶装置は、第1配線3と、第1配線3上に形成された層間絶縁層53と、層間絶縁膜53上に形成された第2配線6と、第1配線3と第2配線6との間に形成された抵抗変化型素子11とを具備する。層間絶縁層53は、第1配線3と第2配線6とに挟まれるように形成され、第1配線3の幅以下の幅を有するホール9を備える。抵抗変化型素子11は、第1配線3と接して、ホール9の底部に形成された下部電極13と、下部電極13上に形成された抵抗変化層12と、抵抗変化層12上に形成された上部電極11とを備える。下部電極13、抵抗変化層12及び上部電極11は、ホール9の内部に形成される。第1配線3は銅を含み、下部電極13、13aはルテニウム、タングステン、コバルト、白金、金、ロジウム、イリジウム及びパラジウムからなる群から選択される少なくとも一種の金属を含んでいる。

(もっと読む)

支持されたゲート電極を備えるトランジスタの作製方法およびそれに関連するデバイス

【課題】貫通する開口を備える保護層を基板上に形成し、さらにこの開口の中にゲート電極を形成することによって、トランジスタを作製する。

【解決手段】ゲート電極の第1の部分は、開口の外側に存在する保護層の表面部分で横方向に延在し、ゲート電極の第2の部分は、保護層から間隔を空けて配置され、第1の部分を越えて横方向に延在する。関連したデバイスおよび作製方法も述べられる。

(もっと読む)

半導体素子及びその製造方法

【課題】 この実施の形態は、SiC半導体基板上に形成されたn型半導体領域とp型半導体領域を形成した半導体装置において、n型半導体領域とp型半導体領域の両領域にまたがって、単一の金属電極用いて同時コンタクトを形成することを目的としている。

【解決手段】 この実施の形態の半導体装置は、導電性材料を用いた第1の電極240に、導電型がp型の第1の炭化珪素(SiC)半導体部220と、導電型がn型の第2のSiC半導体部230とが接続され、前記第1の電極と前記第1の界面部において炭素(C)の面密度がピークになるようしている。

(もっと読む)

半導体装置

【課題】窒化ガリウム系半導体で形成された半導体層を有する半導体素子において、消費電力を増大させず、かつ、大型化することなく、半導体素子の電極に電圧をかけたときに発生する電流コラプス現象を抑制する。

【解決手段】窒化ガリウム系半導体が積層されて形成された半導体素子と、半導体素子に対して積層方向に形成され、外部からのエネルギーの入力なしで半導体素子に光を照射する自己発光体とを備える半導体装置を提供する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】ソース領域に3C−SiC構造のSiCを用いて低い寄生抵抗を実現し、高い性能を備える半導体装置を提供する。

【解決手段】実施の形態の半導体装置は、第1のn型炭化珪素層と、第1のn型炭化珪素層よりもn型不物濃度の低い第2のn型炭化珪素層を有する半導体基板と、第2のn型炭化珪素層に形成される第1のp型不純物領域と、第2のn型炭化珪素層に形成される4H−SiC構造の第1のn型不純物領域と、第2のn型炭化珪素層に形成され、第1のn型不純物領域よりも深さの浅い3C−SiC構造の第2のn型不純物領域と、第2のn型炭化珪素層、第1のp型不純物領域、第1のn型不純物領域の表面にまたがるゲート絶縁膜と、ゲート絶縁膜上のゲート電極と、第1のn型不純物領域上に形成され、底面部と側面部を備え、少なくとも側面部で第1のn型不純物領域との間に第2のn型不純物領域を挟む金属シリサイド層と、を備える。

(もっと読む)

半導体装置

【課題】異なる特性の半導体素子を一体に有しつつ、高集積化が実現可能な、新たな構成の半導体装置を提供することを目的の一とする。

【解決手段】第1の半導体材料が用いられた第1のチャネル形成領域と、第1のゲート電極と、を含む第1のトランジスタと、第1のゲート電極と一体に設けられた第2のソース電極および第2のドレイン電極の一方と、第2の半導体材料が用いられ、第2のソース電極および第2のドレイン電極と電気的に接続された第2のチャネル形成領域と、を含む第2のトランジスタと、を備えた半導体装置である。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】半導体装置について、小型化を図りつつ、ドレイン耐圧を向上する。

【解決手段】ゲート電極20と、ゲート電極20と離間するソース電極24と、平面視でゲート電極20からみてソース電極24の反対側に位置し、かつゲート電極20と離間するドレイン電極22と、平面視でゲート電極20とドレイン電極22の間に位置し、絶縁膜26を介して半導体基板10上に設けられ、かつゲート電極20、ソース電極24およびドレイン電極22と離間する少なくとも一つのフィールドプレート電極30と、絶縁膜26中に設けられ、かつフィールドプレート電極30と半導体基板10を接続する少なくとも一つのフィールドプレートコンタクト40と、を備え、平面視でフィールドプレート電極30は、フィールドプレートコンタクト40からソース電極24側またはドレイン電極22側の少なくとも一方に延伸している。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】SiC基板を用いて形成され、金属シリサイド膜と金属電極との密着性の向上する半導体装置を提供する。

【解決手段】実施の形態の半導体装置は、炭化珪素と、炭化珪素上に形成され、第1の層、第1の層よりも低い炭素比率を有する第2の層を備える金属シリサイドと、金属シリサイド上に形成される金属電極を備え、第2の層が第1の層上に形成され、第2の層が金属電極に接し、第2の層中の金属シリサイドの平均粒径が、第1の層中の金属シリサイドの平均粒径よりも大きい。

(もっと読む)

半導体素子の製造方法

【課題】炭化シリコン基板に接するように、オーミック電極となるシリサイド層を形成するに際して、炭化シリコン基板由来の炭素が、オーミック電極内に拡散して表面に析出するのが抑えられ、オーミック電極の上に電極層を密着性良く形成することができる半導体素子の製造方法を提供することを目的とする。

【解決手段】本発明の半導体素子の製造方法は、炭化シリコン基板2のオーミック電極形成領域2aにシリコン層を形成する第1工程と、シリコン層2上に金属層8を形成する第2工程と、熱処理を行うことによって、シリコン層2に含まれるSiと金属層8の構成元素とを反応させ炭化シリコン基板2と接するシリサイド層41を形成する第3工程と、Siと反応せずに残存した金属層8を除去することによって、シリサイド層41を露出させる第4工程とによってオーミック電極4を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】本発明は、製造コストを低減し、さらにゲート電極およびゲートコンタクトの抵抗を低減した半導体装置およびその製造方法を提供することを目的とする。

【解決手段】本発明にかかる半導体装置は、ゲート電極7の少なくとも上層は、第2金属シリサイド膜としてのWSix膜72からなり、第1金属シリサイド膜としてのNiSi2膜18に含まれる第1金属(Ni)とシリコンとの結合エネルギーが、WSix膜72に含まれる第2金属(W)とのシリコンとの結合エネルギーよりも小さく、WSix膜72の組成MSix(Mは第2金属を示す)において、xが1.5以上2.0未満であることを特徴とする。

(もっと読む)

半導体装置

【課題】層間絶縁膜のエッチングの際に半導体層がエッチングされることによるコンタク

ト抵抗の増大を防ぎ、書き込み特性及び電荷保持特性に優れた不揮発性半導体記憶装置及

びその作製方法を提供する。

【解決手段】ソース領域又はドレイン領域とソース配線又はドレイン配線との間に導電層

を設ける。また、該導電層は、制御ゲート電極を形成する導電層と同じ導電層からなる。

また、該導電層を覆うように絶縁膜が設けられており、該絶縁膜は該導電層の一部が露出

するコンタクトホールを有する。また、該ソース配線又はドレイン配線は、該コンタクト

ホールを埋めるように形成されている。

(もっと読む)

半導体装置

【課題】端子部のコンタクトホールのテーパー形状を高い精度で制御する。

【解決手段】酸化物半導体層7a、ソース配線13as、ドレイン電極13adを備えた薄膜トランジスタと、第1接続部3c、第2接続部13cおよび第2接続部上に形成された第3接続部19cを備えた端子部とからなる薄膜トランジスタである。第2接続部は、第1および第2絶縁膜5,9に設けられた第1開口部内で第1接続部と接し、第3接続部19cは、保護膜に設けられた第2開口部内で第2接続部と接する。第1開口部は、第1絶縁膜5および第2絶縁膜9を同時にエッチングすることによって形成、第2開口部は、保護膜15を前記第1および第2絶縁膜とは別個にエッチングすることによって形成される。第2接続部13cは、第1開口部における第1および第2絶縁膜の端面を覆い、かつ、第2開口部における保護膜15の端面を覆っていない。

(もっと読む)

オーミック電極とその形成方法

【課題】コンタクトホールを形成するために用いられたレジスト膜を、硫酸を含むエッチング液を利用して除去することが可能なオーミック電極の形成方法を提供する。

【解決手段】積層電極部2を形成する積層電極部形成工程と、積層電極部2を熱処理するアニール工程と、熱処理後の積層電極部2を被覆部3で被覆して被覆電極部4を形成する被覆電極部形成工程と、被覆電極部4を覆うように半導体層1の表面に絶縁体膜5を形成する絶縁体膜形成工程と、被覆電極部4に対応して開口7が形成されているレジスト膜6を絶縁体膜5の表面にパターニングするレジスト膜形成工程と、レジスト膜6の開口7から露出する絶縁体膜5を除去して被覆電極部4を露出させる露出工程と、硫酸を含むエッチング液を用いてレジスト膜6を除去するレジスト膜除去工程を備えている。被覆部3の材料は、金又は白金である。

(もっと読む)

半導体装置の製造方法及び処理装置

【課題】薬液の除去性能を高く維持することができる半導体装置の製造方法及び処理装置を提供する。

【解決手段】レジストパターン3をマスクとして絶縁膜2をドライエッチングすることにより開口部4を形成する。絶縁膜2のドライエッチングの際に開口部4の内面に付着した反応生成物5に波長が200nm以下の紫外線を照射して、反応生成物5に含まれる有機成分を分解する。薬液を用いて、有機成分の分解後に開口部4の内面に残存している付着物6を除去する。付着物6が除去された開口部4内に導電膜7を形成する。

(もっと読む)

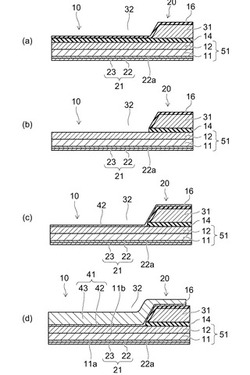

窒化物半導体装置及びその製造方法

【課題】窒化物半導体層上の層間絶縁膜の開口部が、電界の集中が緩和される形状に安定して精度良く形成された窒化物半導体装置及びその製造方法を提供する。

【解決手段】窒化物半導体層30と、窒化物半導体層30上に配置された第1の絶縁膜41と、第1の絶縁膜41上に配置された第2の絶縁膜42と、窒化物半導体層30上に互いに離間して配置された第1及び第2の主電極51,52と、第1及び第2の主電極51,52間で第2の絶縁膜42上に配置され、第1及び第2の絶縁膜に設けられた開口部を介して窒化物半導体層に接続するフィールドプレート60とを備える窒化物半導体装置であって、開口部において、窒化物半導体層30の表面と第1の絶縁膜41の側面とのなす第1の傾斜角が、窒化物半導体層30の表面と第2の絶縁膜42の側面を延長した線とのなす第2の傾斜角よりも小さく形成されている。

(もっと読む)

41 - 60 / 1,154

[ Back to top ]