Fターム[4M104DD39]の内容

半導体の電極 (138,591) | 製造方法(特徴のあるもの) (30,582) | 電極材料の析出 (10,624) | PVD (4,537) | スパッタ (3,176) | 装置 (335)

Fターム[4M104DD39]に分類される特許

121 - 140 / 335

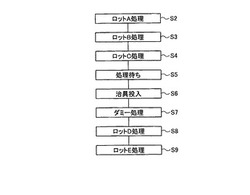

スパッタリング装置及び半導体装置の製造方法

【課題】マルチチャンバーにおけるステージ温度の急激な低下を抑制することによって品質異常を抑制することのできるスパッタリング装置を提供する。

【解決手段】本発明に係るスパッタリング装置は、第1チャンバーと、第2チャンバーと、第3のチャンバーとを具備しており、第3のチャンバーにて処理待ち状態が所定時間経過した後(S5)、ダミー収容室内のダミー基板を第2チャンバー内にて、ダミー基板を加熱しながらダミー基板上に金属膜をスパッタリング成膜し、第2チャンバー内のダミー基板を第3チャンバー内にて、ダミー基板を加熱しないで金属膜上に第2の膜をスパッタリング成膜する(S7)。その後、第3チャンバーにおいて、第2チャンバーによって金属膜が成膜された基板を加熱しない状態で金属膜上に第2の膜をスパッタリング成膜する(S8)。これによって、マルチチャンバーにおけるステージ温度を制御することを特徴とする。

(もっと読む)

金属シリサイド形成のための方法および装置

本明細書で述べられる実施形態は、無拡散アニールプロセスを使用して金属シリサイド層を形成する方法を包含する。一実施形態では、基板上に金属シリサイド材料を形成するための方法が、提供される。その方法は、基板のシリコン含有表面を覆って金属材料を堆積させるステップと、金属材料を覆って金属窒化物材料を堆積させるステップと、金属窒化物材料を覆って金属接点材料を堆積させるステップと、基板を無拡散アニールプロセスにさらして金属シリサイド材料を形成するステップとを含む。無拡散アニールプロセスの短い時間枠は、窒素がシリコン含有界面に拡散して窒化シリコンを形成する時間を低減し、それ故に界面抵抗を最小限にする。  (もっと読む)

(もっと読む)

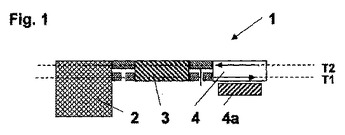

半導体装置およびその製造方法

【課題】良好なオーミック性接触が得られる裏面電極を備えた半導体装置およびその製造方法を提供する。

【解決手段】第1の面11aに半導体素子が形成された半導体基板11と、半導体基板11の第1の面11aと対向する第2の面11bに分散して形成され、金アンチモン合金、または金ガリウム合金を主成分とする第1導電層12と、半導体基板11の第2の面11bに第1導電層12を覆うように形成された第2導電層13と、を具備している。

(もっと読む)

半導体装置及びその作製方法

【課題】電気特性及び信頼性の高い薄膜トランジスタを有する半導体装置、及び該半導体装置を量産高く作製する方法を提案することを課題とする。

【解決手段】半導体層としてIn、Ga、及びZnを含む酸化物半導体膜を用い、半導体層とソース電極層及びドレイン電極層との間に金属酸化物層でなるバッファ層が設けられた逆スタガ型(ボトムゲート構造)の薄膜トランジスタを含むことを要旨とする。ソース電極層及びドレイン電極層と半導体層との間に、バッファ層として金属酸化物層を意図的に設けることによってオーミック性のコンタクトを形成する。

(もっと読む)

真空成膜装置およびそのメンテナンス方法

【課題】真空成膜装置のメンテナンス方法、とりわけ、インライン式スパッタ装置をメンテナンスする場合のシステムベントの方法を必要かつ充分な条件で効率的に行うための手段を提供し、最適な真空成膜装置を提供すること。

【解決手段】真空成膜装置において、真空解除のためのベントガスを導入するにあたり、乾燥ガスと成膜装置設置場所周辺の大気とのいずれかを選択して導入できるようにした。また、装置のシステムベントにおいて成膜装置設置場所周辺の大気の直接導入を行う。

(もっと読む)

成膜装置および成膜方法

【課題】装置コストを増大せずに、良質な薄膜を、高い成膜速度で形成することのできる成膜装置および成膜方法を提供する。

【解決手段】ガスの導入と排気が可能な真空容器と、この真空容器内に配置され、かつ、成膜の材料となるターゲットを保持するバッキングプレートと、前記真空容器内に前記バッキングプレートに対向して配置され、かつ、前記成膜材料の薄膜が形成される成膜用基板を保持する基板ホルダとを有し、前記バッキングプレートは、板状の形状を有し、かつ、焼結により生成する理論上の重さに対する焼結後の実際の重さの比重を表す焼結密度が95%以上であるターゲットよりも熱膨張係数が小さいことにより、前記課題を解決する。

(もっと読む)

大電力パルス化マグネトロンスパッタリング方法および大電力電気エネルギー源

【課題】磁気促進大電力スパッタリング法において、イオン化度を高くし、同時にターゲットの表面から正の電荷を除去し、ターゲットの加熱を防止すると共に、ターゲット材料の利用率を高くすること。

【解決手段】プロセスチャンバ内で、あるシーケンスの複合放電パルスを発生し、スパッタリングガスをイオン化する大電力パルス化マグネトロンスパッタリング法において、この複合放電パルスは、第1のパルス時間(τ1)の間印加される大電力スパッタリングパルス(10)と第2のパルス時間(τ2)の間印加されるターゲット上の電荷を除去する小電力電荷除去パルス(11)とを含み、前記第2パルス時間(τ2)に対する前記第1パルス時間(τ1)の比(τ1/τ2)は最大で0.5である。

(もっと読む)

薄膜電気デバイスを製造するシステム及び方法

薄膜電気デバイスを基板上に製造するシステムを使用する方法が一実施例により与えられる。本システムはチャンバ及び気体ゲートを含む。チャンバはその中に集積装置を含む。集積装置はチャンバ内にて基板の一部分を集めるべく構成される。気体ゲートは、チャンバの圧力領域と第2圧力領域との流体連通を与える。  (もっと読む)

(もっと読む)

半導体素子の電極、これを備える半導体素子、その製造方法

【課題】Gaを含有するn型半導体層に対して低いコンタクト抵抗を実現する。

【解決手段】本発明は、ガリウム(Ga)を含有するn型半導体層201の表面に形成されるn側電極110である。電極110は、Ga含有率が1原子数%以上25原子数%以下の金属層202を有する。金属層202はn型半導体層201に接している。

(もっと読む)

半導体装置の製造方法およびそれに用いる半導体製造装置

【課題】裏面電極を有する半導体装置の信頼性を向上させる。

【解決手段】シリコン基板の表面f1に半導体素子を形成(工程s01)した後、その反対側の裏面f2に、処理装置SP内で以下の工程を施す。まず、第1チャンバch1内でシリコン基板の裏面f2に第1金属膜M1を堆積(工程s03)した後、熱処理を施すことで金属シリサイド膜E1を形成する(工程s04)。続いて、第3チャンバch3内でニッケル膜E3を堆積し(工程s06)、第2チャンバch2内で酸化防止導体膜E4を堆積する(工程s07)。第1金属膜M1とシリコン基板とを合金化するための熱処理(工程s04)は、少なくともニッケル膜E3を堆積する前に施す。そのために、第1チャンバch1は第1金属膜M1を堆積する機構とランプ加熱機構とを有する。

(もっと読む)

銅スパッタリングターゲット材及びスパッタリング方法

【課題】成膜条件(成膜中の圧力、成膜に用いるガス種等)を変更しなくても、成膜された銅膜中の引張残留応力を低減できる銅スパッタリングターゲット材及びスパッタリング方法提供する。

【解決手段】本発明に係る銅スパッタリングターゲット材10は、一の結晶方位面と他の結晶方位面とを有し、銅材からなるスパッタ面12を備え、一の結晶方位面は、加速された所定の不活性ガスイオンの照射により他の結晶方位面から弾き出されるスパッタ粒子のエネルギーより大きいエネルギーのスパッタ粒子を放出し、一の結晶方位面と他の結晶方位面との総和に対する一の結晶方位面の占有割合は、15%以上である。

(もっと読む)

半導体デバイスの電極形成方法

【課題】高価な金(Au)を経済的に使用することができる半導体デバイスの電極形成方法を提供する。

【解決手段】半導体基板の表面に格子状に形成された複数のストリートによって区画された領域にデバイスが形成された半導体ウエーハにおける半導体基板の裏面に電極を形成する半導体デバイスの電極形成方法であって、半導体基板の裏面におけるデバイスの電極領域と対応する領域に開口が形成されたマスク部材を貼着するマスキング工程と、マスキング工程が実施された半導体基板の裏面に金をスパッタリングによって積層し半導体基板の裏面におけるデバイスの電極領域に電極を形成する電極形成工程と、電極形成工程が実施された半導体基板の裏面に貼着されているマスク部材を剥離するマスク部材剥離工程と、マスク部材剥離工程によって剥離されたマスク部材に積層されている金を回収する金回収工程とを含む。

(もっと読む)

マグネトロンスパッタ方法及びマグネトロンスパッタ装置

【課題】マグネトロンスパッタ法において短冊形ターゲットを使用して半導体ウエハにスパッタ成膜を効率的かつ均一に行えるようにする。

【解決手段】被成膜体の半導体ウエハをウエハ配置面P上の円形基準領域Aにぴったり重ねて配置する。そして、円形基準領域Aの中心AOを通る法線を回転中心軸として半導体ウエハを所定の回転数で同軸回転させる。そうすると、半導体ウエハ表面の各部は、一回転毎に、半径R/2よりも内側のウエハ中心部は短冊形堆積領域B1のみを通過する間に短冊形ターゲット10(1)からのスパッタ粒子を浴び、半径R/2よりも外側のウエハ周辺部では両短冊形堆積領域B1,B2を通過する間に両短冊形ターゲット10(1),10(2)からのスパッタ粒子を浴びるという形態のスパッタ成膜処理を受ける。

(もっと読む)

スパッタリング装置、それを用いた太陽電池及び画像表示装置の製造方法

【課題】第一ターゲット17a及び第二ターゲット17bが、それぞれ基板6及び他のターゲットに対して斜めに対向して配置され、基板6を搬送経路15に沿って搬送しながら成膜する連続方式のスパッタリング装置において、高品質の膜が得られるようにすると共に、粒子のチャンバー3内拡散を防止できるようにする。

【解決手段】第一ターゲット17aと第二ターゲット17bとの間の空間の搬送経路15側への延長領域を挟んで、搬送経路15と、第一ターゲット17a及び第二ターゲット17bとの間に、少なくとも基板6の搬送方向に対向するシールド19a,19bを設ける。

(もっと読む)

成膜装置および成膜方法

【課題】はんだ等の低融点金属を含有する合金膜を、含有金属組成のずれを生じることなく、かつ成膜レートを低下させることなく成膜できる成膜装置および成膜方法を提供する。

【解決手段】減圧雰囲気とした空間内に、低融点金属を含有する合金ターゲットを設けたカソード電極と基板を設けたアノード電極とを対向して配置し、前記基板の一方の面に、前記低融点金属を含有する合金膜をスパッタ法により形成する成膜装置であって、前記カソード電極にDCパルス電圧Ekを印加する電源手段を少なくとも備えたことを特徴とする成膜装置。

(もっと読む)

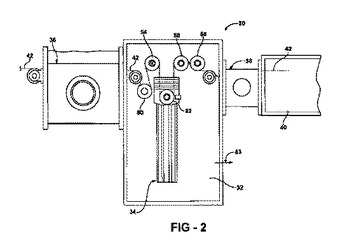

処理システム及び処理システムを運転する方法

コーティングシステム1は、スイングモジュール及びチャンバ配列を含むスイングステーション2を含む。チャンバ配列は、ロックチャンバ3及び第1コーティングチャンバ4を含む。ロックチャンバ3は、結合されたロックイン/ロックアウトチャンバとして構成される。チャンバ配列は、破線で示される第1実質的直線搬送経路T1及び破線で示される第2実質的直線搬送経路T2を有する。経路T1、T2の配置は、デュアルトラックを確立する。システム1は、矢印で示されるように、チャンバ配列3、4を通って、第1搬送経路T1に沿って、及び/又は、第2搬送経路T2に沿って、基板を移動させるための搬送システムを含む。1又は特に両方のチャンバ3、4は、デュアル又はトリプルトラックセクションの横移動によって、第1経路T1から第2経路T2へ、及び/又は、第2経路T2から第1経路T1へ基板/キャリヤを移動させるための移動手段を含む。  (もっと読む)

(もっと読む)

均一蒸着のための装置及び方法

本発明の実施形態は、一般に、基板上のアスペクト比の高い特徴部の底部及び側壁上に材料を均一にスパッタ蒸着させるための装置及び方法に関する。1つの実施形態では、スパッタ蒸着システムが、開口部を有するコリメータを含み、この開口部のアスペクト比が、コリメータの中心領域からコリメータの周辺領域にかけて減少する。1つの実施形態では、内部にねじ山のある留め具と外部にねじ山のある留め具との組み合わせを含むブラケット部材を介して、コリメータが接地されたシールドに結合される。別の実施形態では、コリメータが、接地されたシールドに一体的に取り付けられる。1つの実施形態では、材料をスパッタ蒸着させる方法が、基板支持部上のバイアスを高い値と低い値の間でパルスするステップを含む。 (もっと読む)

多元化合物作製装置

【課題】

本発明は、このような実情に鑑み、従来より高精度の組成比変化にて、多元化合物を一

度の蒸着にて生成できる装置を提供することを目的とする。

【解決手段】

発明1の多元化合物作製装置は、一つの蒸着室内に、蒸着材料を蒸発させる材料蒸発機構と、前記材料蒸発機構からの蒸気により蒸着される基材を保持する基材保持部と、この基材保持部と前記材料蒸発機構との間に配置した蒸気通過用開口部を持つマスクと、このマスクを前記基材の蒸着面に沿って移動させるマスク移動機構とを有する多元化合物作製装置であって、前記マスクと基材に蒸着面との間隔を調整する間隔調整手段が設けてあることを特徴とする。

(もっと読む)

スパッタリング方法及びスパッタリング装置

【課題】成膜速度の大きく低ダメージで、かつ、安定した放電が可能なスパッタリング技術を提供する。

【解決手段】本発明は、平板状のターゲット30を用い、真空中で基板20に対してスパッタリングによって成膜を行うスパッタリング方法であって、ターゲット30の縁部30aが基板20の成膜面20aに対して対向する第1の成膜位置にターゲット30を配置して成膜を行う第1のスパッタリング工程と、ターゲット30の正面部30bが基板20の成膜面20aに対して対向する第2の成膜位置にターゲット30を配置して成膜を行う第2のスパッタリング工程とを有する。

(もっと読む)

スパッタリング装置及びスパッタリング方法

【課題】成膜速度の大きく低ダメージで、かつ、安定した放電が可能なスパッタリング技術を提供する。

【解決手段】本発明は、真空槽2内において基板20を保持して移動可能な基板ホルダー3と、真空槽2内において第1及び第2のカソード部6、7を有するスパッタ源4と、スパッタ粒子40を通過させるための開口部10を有するスリット機構9とを備える。第1のカソード部6は、第1のターゲット21の粒子放出面21aが基板20の成膜面20aに対して対向せず、かつ、第1のターゲット21の粒子放出面21aが基板20の成膜面20aに対して鋭角となるように配置構成され、第2のカソード部7は、第2のターゲット22の粒子放出面22aが基板20の成膜面20aに対して対向するように配置構成され、スリット機構9は開口部10が基板20の成膜面20aに対向する位置で第1のカソード部6の第1のターゲット21から放出される低エネルギーのスパッタ粒子40aの飛翔領域に配置されている。

(もっと読む)

121 - 140 / 335

[ Back to top ]