Fターム[4M104DD65]の内容

半導体の電極 (138,591) | 製造方法(特徴のあるもの) (30,582) | 電極膜のパターニング (4,427) | エッチング (3,048) | ドライエッチ (1,225)

Fターム[4M104DD65]の下位に属するFターム

異方性の利用 (241)

選択比向上用ガス組成 (37)

Fターム[4M104DD65]に分類される特許

201 - 220 / 947

半導体装置の製造方法

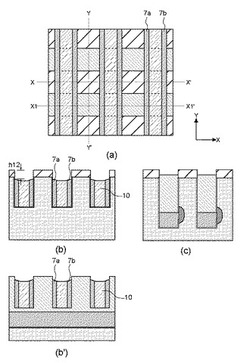

【課題】溝側面に側壁膜を形成する際に、側壁膜表面にエッチングダメージを受けることなく、側壁膜上面の溝開口部からの深さのばらつきを抑制して形成可能な方法を提供する。

【解決手段】半導体基板主表面に形成された溝の側壁に第1の層を形成する工程、溝を保護膜で埋設する工程、保護膜の表面の高さが溝の開口部よりも低い位置になるようにドライエッチング法でエッチバックし、該エッチバックにより露出した第1の層をエッチング除去する工程、とを含む半導体装置の製造方法。

(もっと読む)

窒化物半導体発光素子

【課題】本発明によれば、動作電圧が低く、かつ光取り出し効率が高い窒化物半導体発光素子を提供することができる。

【解決手段】本発明の窒化物半導体発光素子は、n型窒化物半導体層、AlxqInyqGa1-xq-yqN井戸層を備えた発光層、p型窒化物半導体層をこの順に備えた窒化物半導体発光素子であって、p型窒化物半導体層と接するp側窒化物コンタクト層と、p側窒化物コンタクト層と接する透光性電極層とを有し、p側窒化物コンタクト層は、AlxInyGa1-x-yN(0≦x<1、0<y<1)からなり、透光性電極層は、ニオブ、タンタル、モリブデン、ヒ素、アンチモン、アルミニウム、またはタングステンからなる群より選択される元素のうち一種以上がドープされた二酸化チタンからなることを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】 高誘電率ゲート絶縁膜を用い、PMOS、NMOSそれぞれに適した仕事関数を有するCMOSFETを有する半導体装置及びその製造方法を提供する。

【解決手段】 半導体基板の主面に素子分離領域によって、絶縁分離されたP型及びN型領域を形成する工程と、前記第P型及びN型領域上にシリコン酸化膜或いはシリコン酸窒化膜からなる第一の絶縁膜を形成する工程と、前記P型領域上の前記第一の絶縁膜上にランタン酸化膜を形成する工程と、前記P型領域上の前記ランタン酸化膜及び前記N型領域上の前記第一の絶縁膜上にハフニウム或いはジルコニウムを含む第二の絶縁膜を形成する工程と、前記第二の絶縁膜上にTixNyとするとx/y<1を満たすチタンナイトライド膜を形成する工程とを備えることを特徴とする半導体装置の製造方法。

(もっと読む)

金属ゲートトランジスタ、集積回路、システム、およびその製造方法

【課題】金属ゲートトランジスタ、集積回路、システム、およびその製造方法を提供する。

【解決手段】半導体デバイスであって、第1MOS構造は、基板上に配置された第1ゲート誘電体、前記第1ゲート誘電体上に配置された第1仕事関数金属層、および前記第1仕事関数金属層上に配置された第1ケイ化物を含み、且つ第2MOS構造は、前記基板上に配置された第2ゲート誘電体、前記第2ゲート誘電体上に配置された第2仕事関数金属層、および前記第2仕事関数金属層上に配置された第2ケイ化物を含む半導体デバイス。

(もっと読む)

半導体装置の製造方法

【課題】欠陥を内在する炭化珪素半導体を用いても、大面積半導体装置の高歩留りを安定して実現可能な半導体装置の製造方法を提供する。

【解決手段】炭化珪素半導体基板上に炭化珪素半導体層をエピタキシャル成長する工程と、炭化珪素半導体層表面を研磨する工程と、研磨する工程の後に、炭化珪素半導体層に不純物をイオン注入する工程と、不純物を活性化するための熱処理をする工程と、熱処理をする工程の後に、炭化珪素半導体層表面に第1の熱酸化膜を形成する工程と、第1の熱酸化膜を化学的に除去する工程と、炭化珪素半導体層上に電極層を形成する工程と、を有することを特徴とする半導体装置の製造方法。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】半導体装置の開口率を向上させる。

【解決手段】同一基板上に第1の薄膜トランジスタを有する駆動回路及び第2の薄膜トランジスタを有する画素を有し、前記第1の薄膜トランジスタは、第1のゲート電極層と、ゲート絶縁層と、第1の酸化物半導体層と、第1の酸化物導電層及び第2の酸化物導電層と、前記第1の酸化物半導体層の一部に接し、且つ前記第1の酸化物導電層及び前記第2の酸化物導電層の周縁及び側面に接する酸化物絶縁層と、第1のソース電極層と、第1のドレイン電極層と、を有し、前記第2の薄膜トランジスタは、第2のゲート電極層と、第2の酸化物半導体層と、透光性を有する材料により構成された第2のソース電極層及び第2のドレイン電極層と、を有する。

(もっと読む)

半導体装置およびその作製方法

【課題】画素部の開口率を高くしながら、駆動回路部の特性を向上させた半導体装置を提供することを課題とする。または、消費電力の低い半導体装置を提供することを課題とする。または、しきい値電圧を制御できる半導体装置を提供することを課題とする。

【解決手段】絶縁面を有する基板と、基板上に設けられた画素部と、画素部を駆動する駆動回路の少なくとも一部を有し、画素部を構成するトランジスタおよび駆動回路を構成するトランジスタは、トップゲートボトムコンタクト型のトランジスタであって、画素部においては、電極および半導体層が透光性を有し、駆動回路における電極は、画素部のトランジスタが有するいずれの電極よりも低抵抗である半導体装置である。

(もっと読む)

半導体装置の製造方法

【課題】第1導電型の第1の多結晶シリコン膜と第2導電型の第2の多結晶シリコン膜とを同時にエッチング加工する際の加工精度を向上するための製造方法の提供。

【解決手段】第1導電型の不純物を含む第1の多結晶シリコン膜103−1と、第2導電型の不純物を含む第2の多結晶シリコン膜103−2とを形成し、前記第1の多結晶シリコン膜をエッチングし、第1のパターンを形成するとともに、前記第2の多結晶シリコン膜をエッチングし、第2のパターンを形成するパターニング工程とを備える。パターニング工程は、第1のパターン及び第2のパターンのそれぞれの側面を露出させるようにエッチングを行う第1のエッチング工程と、露出した側面を酸化して側面に酸化膜を形成する酸化工程と、側面が酸化膜で保護された状態でエッチングを行い、第1の多結晶シリコン膜及び第2の多結晶シリコン膜のパターニングを完了させる第2のエッチング工程とを含む。

(もっと読む)

半導体装置およびその作製方法

【課題】半導体装置の製造コストを低減することを課題の一とする。半導体装置の開口率を向上することを課題の一とする。半導体装置の表示部を高精細化することを課題の一とする。高速駆動が可能な半導体装置を提供することを課題の一とする。

【解決手段】同一基板上に駆動回路部と表示部とを有し、当該駆動回路部は、ソース電極及びドレイン電極が金属によって構成され、且つチャネル層が酸化物半導体によって構成された駆動回路用TFTと、金属によって構成された駆動回路用配線とを有すればよい。また、当該表示部はソース電極及びドレイン電極が酸化物導電体によって構成され、且つ半導体層が酸化物半導体によって構成された画素用TFTと、酸化物導電体によって構成された表示部用配線とを有すればよい。

(もっと読む)

半導体装置およびその製造方法

【課題】 酸化物半導体においてはイオン注入法による拡散層形成が難しいため、バルクシリコンMOSトランジスタや多結晶シリコンTFTのようなイオン注入法を用いた自己整合プロセスを組むことができない。本願では、リフトオフを用いる場合のような不都合の生じない自己整合プロセスを酸化物半導体において実現することを課題とする。

【解決手段】 裏面露光により製造される薄膜トランジスタ(TFT)において、チャネル層として酸化物半導体を用い、基板上の電極をマスクとして、基板の裏面側から導電膜上のネガレジストを露光し、ネガレジストの露光部分を残し前記ネガレジストを除去し、露光部分をエッチングマスクとする導電膜のエッチングにより、電極を加工する。

(もっと読む)

半導体装置、および半導体装置の製造方法

【課題】ソース/ドレイン領域のPN接合部とコンタクト間のリーク電流を抑制する。

【解決手段】半導体基板(1)と、半導体基板(1)に形成されたSTI(Shallow Trench Isolation)構造(2)と、半導体基板(1)に形成され、STI構造(2)に隣接する拡散領域(12)と、層間絶縁膜(15)を貫通して拡散領域(12)とSTI構造(2)とに到達する接続コンタクト(20)と、拡散領域(12)の側面と拡散領域(12)の下の半導体基板(1)の側面に形成され、接続コンタクト(20)と拡散領域(12)の側面とを電気的に絶縁し、かつ、接続コンタクト(20)と半導体基板(1)の側面とを電気的に絶縁する酸化膜(19)とを具備する半導体装置を構成する。その半導体装置では、STI素子分離とソース/ドレイン領域のPN接合部分の間のみに選択的に絶縁膜(酸化膜)を形成している。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の製造過程において生じるウエハ外周部分からのパーティクルの発生を防止し、十分な歩留りを実現する。

【解決手段】ウエハにゲート電極となる導電膜4、5を形成する第一工程と、導電膜4、5の中の、ウエハの外周部分に形成された導電膜4、5の上に選択的に保護膜7を形成する第二工程と、導電膜4、5の上に第一レジストパターンを形成し、前記第一レジストパターンをマスクとして導電膜4、5をエッチングすることにより、ゲート電極を形成する第三工程と、前記ゲート電極を覆う層間絶縁膜を形成する第四工程と、前記層間絶縁膜の上に第二レジストパターンを形成し、前記第二レジストパターンをマスクとして前記層間絶縁膜をエッチングすることにより、コンタクトホールを形成する第五工程と、を有する半導体装置の製造方法を提供する。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の性能を向上させる。

【解決手段】半導体基板1上に複数のロジック用pチャネル型MISFETQp1と、複数のロジック用nチャネル型MISFETQn1と、複数のメモリ用pチャネル型MISFETQp2と、複数のメモリ用nチャネル型MISFETQn2とが混載されている。複数のロジック用pチャネル型MISFETQp1のうちの少なくとも一部は、シリコンゲルマニウムで構成されたソース・ドレイン領域を有し、複数のロジック用nチャネル型MISFETQn1の全ては、それぞれシリコンで構成されたソース・ドレイン領域を有している。複数のメモリ用pチャネル型MISFETQp2の全ては、それぞれシリコンで構成されたソース・ドレイン領域を有し、複数のメモリ用nチャネル型MISFETQn2の全ては、それぞれシリコンで構成されたソース・ドレイン領域を有している。

(もっと読む)

半導体装置およびその製造方法

【課題】 厚さが異なるゲート電極を含む、互いにチャネルタイプの異なるMISFETの対を形成する際におけるリソグラフィのプロセスマージンの低下を抑制できる半導体装置を提供すること。

【解決手段】 半導体装置は、第1の主面を有する半導体領域を含む第1の領域Pと、第2の主面を有する半導体領域を含む第2の領域Nとを備え、前記第1の主面が前記第2の主面よりも低い、半導体基板100と、第1の領域P内に設けられ、第1のゲート電極108,109を含む第1導電型MISFETと、第2の領域N内に設けられ、第2のゲート電極109を含む第2導電型MISFETであって、第2のゲート電極109の上面と第1のゲート電極108,109の上面とが同じ高さになるように、第2のゲート電極109の厚さは第1のゲート電極108,109の厚さよりも薄くなっている前記第2導電型MISFETとを具備してなることを特徴とする。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】半導体装置の開口率を向上することを課題の一とする。

【解決手段】同一基板上に第1の薄膜トランジスタを有する画素部と第2の薄膜トランジスタを有する駆動回路を有し、画素部の薄膜トランジスタは、ゲート電極層、ゲート絶縁層、膜厚の薄い領域を周縁に有する酸化物半導体層、酸化物半導体層の一部と接する酸化物絶縁層、ソース電極層及びドレイン電極層、及び画素電極層とを有し、第1の薄膜トランジスタのゲート電極層、ゲート絶縁層、酸化物半導体層、ソース電極層、ドレイン電極層、酸化物絶縁層、及び画素電極層は透光性を有し、駆動回路部の薄膜トランジスタのソース電極層及びドレイン電極層は、保護絶縁層で覆われ、画素部のソース電極層及びドレイン電極層よりも低抵抗の導電材料である半導体装置を提供する。

(もっと読む)

半導体装置ならびに半導体装置の製造方法

【課題】ヒロックに対して400℃程度の耐熱性を有するNd添加量2at%のAlNd層を塩素系ガスでプラズマエッチングする場合、フェンスと呼ばれる反応生成物が堆積した領域が生じる。フェンスの存在により、AlNd層をゲート電極としてTFTを形成した場合、ゲート電極脇に電気的に不安定な領域ができることから、TFTの電気的特性が不安定になる場合があるという課題がある。

【解決手段】AlNd層203を層厚0.45μm以上0.8μm以下、Ndの含有量を0.5at%以上1.0at%以下に形成した。この条件範囲であれば、塩素ガスを主としたプラズマエッチングを行ってもフェンスの発生が抑えられる。また、基板温度を500℃まで上げられることから、層間絶縁層211として信頼性が高い酸化シリコン層をAlNd層203にヒロックを発生させることなく形成することができ、信頼性が高いTFT220を提供することが可能となる。

(もっと読む)

半導体装置の製造方法

【課題】

微細化したMOSトランジスタを含む半導体装置において、リーク/ショートの可能性を抑制する。

【解決手段】

半導体装置の製造方法は、活性領域上に、ゲート絶縁膜とシリコン膜とを形成し、シリコン膜上方にゲート電極用レジストパターンを形成し、レジストパターンをマスクとして、シリコン膜を厚さの途中までエッチングしてレジストパターン下方に凸部を残し、レジストパターンを除去した後シリコン膜を覆うダミー膜を形成し、ダミー膜を異方性エッチングして、凸部の側壁にダミー膜を残存させつつ、平坦面上のダミー膜を除去し、ダミー膜をマスクとして、シリコン膜の残りの厚さをエッチングしてゲート電極を形成し、ゲート電極両側の半導体基板に、ソース/ドレイン領域を形成し、シリコン領域にシリサイドを形成する。

(もっと読む)

薄膜トランジスタ基板および表示デバイス

【課題】ソース電極とドレイン電極のドライエッチングレートの低下や、エッチング残さを引き起こすことがなく、半導体層と、ソース電極やドレイン電極といった配線金属の間からバリアメタルを省略することができる薄膜トランジスタ基板および表示デバイスを提供する課題とする。

【解決手段】半導体層1、ソース電極2、ドレイン電極3、透明導電膜4を有する薄膜トランジスタ基板において、ソース電極2とドレイン電極3は、ドライエッチング法によるパターニングで形成されたGe:0.3〜1.2原子%、Ni:0.1〜1.0原子%未満、Laおよび/またはNd:0.1原子%〜1.0 原子%を含有するAl合金薄膜より成り、半導体層1と直接接続している。

(もっと読む)

半導体装置

【課題】画素TFTを作製する工程数を削減して製造コストの低減および歩留まりの向上を実現し、信頼性と生産性を向上させる技術を提供することを課題とする。

【解決手段】画素領域に形成する画素TFTをチャネルエッチ型の逆スタガ型TFTで基板上に形成し、ソース領域及びドレイン領域のパターニングと画素電極のパターニングを同じフォトマスクで行う。また、ソース配線を画素電極と同じ材料である導電膜で覆い、基板全体を外部の静電気等から保護する構造とする。このような構成とすることで、製造工程において製造装置と絶縁体基板との摩擦による静電気の発生を防止することができる。特に、製造工程で行われる液晶配向処理のラビング時に発生する静電気からTFT等を保護することができる。

(もっと読む)

薄膜トランジスタ基板および表示デバイス

【課題】ソース電極とドレイン電極のドライエッチングレートの低下や、エッチング残さを引き起こすことがなく、半導体層と、ソース電極やドレイン電極といった配線金属の間からバリアメタルを省略することができる薄膜トランジスタ基板および表示デバイスを提供する課題とする。

【解決手段】半導体層1、ソース電極2、ドレイン電極3、透明導電膜4を有する薄膜トランジスタ基板において、ソース電極2とドレイン電極3は、ドライエッチング法によるパターニングで形成されたGe:0.3原子%〜1.2原子%、Co:0.05原子%〜2.0原子%、Laおよび/またはNd:0.1原子%〜0.5 原子%を含有するAl合金薄膜より成り、半導体層1と直接接続している。

(もっと読む)

201 - 220 / 947

[ Back to top ]