Fターム[4M104DD65]の内容

半導体の電極 (138,591) | 製造方法(特徴のあるもの) (30,582) | 電極膜のパターニング (4,427) | エッチング (3,048) | ドライエッチ (1,225)

Fターム[4M104DD65]の下位に属するFターム

異方性の利用 (241)

選択比向上用ガス組成 (37)

Fターム[4M104DD65]に分類される特許

141 - 160 / 947

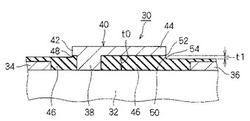

電界効果トランジスタ

【課題】電界効果トランジスタにおいて、フィールドプレート終端での高電界の集中を緩和し、もって高耐圧半導体装置として利用可能とする。

【解決手段】本電界効果トランジスタ30は、GaN系エピタキシャル基板32の電子走行層上に、ゲート電極38を挟んで配置されたソース電極34及びドレイン電極36を備え、ゲート電極38の上部に、ドレイン電極36側及びソース電極34側に庇状に突き出したフィールドプレート40が形成され、基板32の表面層とフィールドプレート40との間に誘電体膜46が形成され、誘電体膜46は、フィールドプレート40のドレイン電極36側及びソース電極34側の終端面と面一状態となるように切れ込み、ドレイン電極36側の下端からドレイン電極36に接続するようにドレイン電極36に向かって延びており、且つ、ソース電極34側の下端からソース電極34に接続するようにソース電極34に向かって延びている。

(もっと読む)

薄膜トランジスタの製造方法

【課題】オーミックコンタクト層の膜厚やドライエッチング時のエッチングレートに依存せず所望のエッチングが可能となる薄膜トランジスタの製造方法を提供する。

【解決手段】絶縁性基板上に、ゲート電極と、ゲート電極を覆うように形成されたゲート絶縁膜と、半導体層と、オーミックコンタクト層と、ソース・ドレイン電極と、を備える薄膜トランジスタの製造方法であって、絶縁性基板上に、ゲート電極と、ゲート絶縁膜と、半導体層と、オーミックコンタクト層と、ソース・ドレイン電極と、がこの順に積層される積層ステップと、積層ステップによって積層されたソース・ドレイン電極とオーミックコンタクト層とがエッチングガスでエッチングされるエッチングステップと、オーミックコンタクト層がエッチングされてゲート絶縁膜が露出し始める点をエッチング終了ポイントとして検知するエッチング終了検知ステップと、を備える薄膜トランジスタの製造方法。

(もっと読む)

化合物半導体装置

【課題】ゲート電極のリーク電流の増大を抑制して、長期間にわたって安定した高電圧動作を実現する。

【解決手段】GaNからなる化合物半導体層100上に形成されたゲート電極102において、GaNからなる化合物半導体層100上でショットキー接合してなるTixW1-xN層(0<x<1)43と、TixW1-xN層43の上方に形成され、Au、Cu及びAlからなる群から選択された1種の金属からなる低抵抗金属層42を設けるようにする。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の性能を向上させる。

【解決手段】半導体基板1の主面にゲート絶縁膜用のHf含有膜4、Al含有膜5及びマスク層6を形成してから、nチャネル型MISFET形成予定領域であるnMIS形成領域1Aのマスク層6とAl含有膜5を選択的に除去する。それから、nMIS形成領域1AのHf含有膜4上とpチャネル型MISFET形成予定領域であるpMIS形成領域1Bのマスク層6上に希土類含有膜7を形成し、熱処理を行って、nMIS形成領域1AのHf含有膜4を希土類含有膜7と反応させ、pMIS形成領域1BのHf含有膜4をAl含有膜5と反応させる。その後、未反応の希土類含有膜7とマスク層6を除去してから、メタルゲート電極を形成する。マスク層6は、窒化チタン又は窒化タンタルからなる窒化金属膜6aと、その上のチタン又はタンタルからなる金属膜6bとの積層構造を有する。

(もっと読む)

金属配線

【課題】従来の、真空装置を用いた形成方法に比べて簡便かつ安価に形成され、しかもインクジェット印刷方法によって形成されるもの比べて、断線等を生じることなしに、より細線化された金属配線を提供する。

【解決手段】Ag粒子、またはAgを50原子%以上含む合金粒子を含む分散液を塗布して塗膜を形成し、乾燥後にパターン形成したのち焼成して形成され、その縁部2における、基材の表面方向の、想定される外形線4からの凹入量の最大値と突出量の最大値との和が50nm以下、前記縁部2における、基材3の表面方向の、想定される外形線4と直交し、かつ金属配線1の厚み方向の断面のうち、前記厚み方向の外形線の、前記基材3の表面と接する部分の、前記基材3の表面との交差角度が70°以下で、かつ抵抗率が14μΩ・cm以下である。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、特性の安定したトランジスタを得ることが可能で、かつ複数の縦型トランジスタ間の特性のばらつきを抑制可能な半導体装置及びその製造方法を提供することを課題とする。

【解決手段】半導体基板11の表面11aが部分的にエッチングされて形成され、縦壁面となる第1及び第2の側面26a,26bを含む内面によって区画された第2の溝26と、第2の溝26の第1及び第2の側面26a,26bを覆うゲート絶縁膜32と、ゲート絶縁膜32上に形成され、上端面37a,38aが半導体基板11の表面11aより低い位置にある第1の導電膜34、及び第1の導電膜34に形成され、上端面35aが第1の導電膜34の上端面34aより低い位置にある第2の導電膜35よりなるゲート電極33と、第2の溝26内に、半導体基板11の表面11aより低い位置に配置され、第2の導電膜35の上端面35aを覆う第1の絶縁膜17と、を有する。

(もっと読む)

化合物半導体装置の製造方法及び化合物半導体装置

【課題】リフトオフ法を用いずに、簡易な手法で化合物半導体装置のゲート電極、ソース電極、及びドレイン電極を各種パターンに欠陥を生ぜしめることなく形成する。

【解決手段】AlGaN/GaN・HEMTを製造する際に、化合物半導体層上に保護絶縁膜8を形成し、保護絶縁膜8に開口を形成し、開口を埋め込む導電材料を保護絶縁膜8上に形成し、導電材料上の開口上方に相当する部位にマスクを形成し、マスクを用いて導電材料をエッチングしてゲート電極15(又はソース電極45及びドレイン46)を形成し、その後、保護絶縁膜8上に保護絶縁膜16を形成し、保護絶縁膜8,16に開口を形成し、開口を埋め込む導電材料を保護絶縁膜16上に形成し、導電材料上の開口上方に相当する部位にマスクを形成し、マスクを用いて導電材料をエッチングしてソース電極22及びドレイン23(又はゲート電極53)を形成する。

(もっと読む)

半導体装置の製造方法

【課題】サイドウォールスペーサを利用してリソグラフィー解像限界未満のパターンと任意の寸法のパターンとが混在するパターンを形成する。

【解決手段】アモルファスカーボン膜3及びシリコン酸窒化膜4からなる被エッチング部材上に塗布膜5をスピン塗布法により成膜し、塗布膜5をパターニングすることによってサイドウォールコアを形成し、サイドウォールコアの少なくとも側面を覆うシリコン酸化膜7を成膜し、シリコン酸化膜7上に有機反射防止膜8をスピン塗布法により成膜する。次いで、有機反射防止膜8をエッチングすることによって、シリコン酸化膜7の凹部7aを覆う埋込マスクを形成し、シリコン酸化膜7をエッチングすることにより、サイドウォールコアまたは埋込マスクと重ならない被エッチング部材を露出させ、被エッチング部材をエッチングすることでフォトリソグラフィー解像限界未満のパターンを得る。

(もっと読む)

半導体装置

【課題】本発明は、不純物拡散層と半導体基板との間に形成される空乏層中におけるGIDLを抑制することのできる半導体装置を提供することを課題とする。

【解決手段】半導体基板11の表面11aが部分的にエッチングされて形成された第2の溝32と、少なくとも第2の溝32の側面32aを覆うゲート絶縁膜38と、ゲート絶縁膜38を介して、第2の溝32の側面32aに形成され、その上端面45aが半導体基板11の表面11aより低い位置にあってゲート電極39となる第1の導電膜45と、第1の導電膜45に形成され、その上端面46aが第1の導電膜45の上端面45bよりも高く、かつ半導体基板11の表面11aより低い位置にあってゲート電極39となる第2の導電膜46と、第1の導電膜45の上端面45b、及び第1の導電膜45の上端面45bから突出した第2の導電膜46を覆うように、第2の溝32内に設けられた第2の絶縁膜と、を有する。

(もっと読む)

半導体装置の作製方法

【課題】不良を抑制しつつ微細化を達成した半導体装置の提供を目的の一とする。

【解決手段】平坦な表面上に絶縁膜を形成し、絶縁膜上にマスクを形成し、マスクにスリミング処理を行い、マスクを用いて絶縁膜にエッチング処理を行い、絶縁膜を覆うように導電膜を形成し、導電膜および絶縁膜に研磨処理を行うことにより、導電膜および絶縁膜の厚さを等しくし、導電膜をエッチングして、導電膜より厚さの小さいソース電極およびドレイン電極を形成し、絶縁膜、ソース電極、およびドレイン電極と接する酸化物半導体膜を形成し、酸化物半導体膜を覆うゲート絶縁膜を形成し、ゲート絶縁膜上の絶縁膜と重畳する領域にゲート電極を形成する。

(もっと読む)

半導体装置の作製方法、及び半導体装置

【課題】酸化物半導体層を用い、電気特性の優れた薄膜トランジスタを備えた半導体装置

を提供することを課題の一とする。また、同一基板上に複数種類の薄膜トランジスタの構

造を作製して複数種類の回路を構成し、増加する工程数が少ない半導体装置の作製方法を

提供することを課題の一とする。

【解決手段】絶縁表面上に金属薄膜を成膜した後、酸化物半導体層を積層し、その後、加

熱処理などの酸化処理を行うことで金属薄膜の一部または全部を酸化させる。また、論理

回路などの高速動作を優先する回路と、マトリクス回路とで異なる構造の薄膜トランジス

タを配置する。

(もっと読む)

半導体装置及びその製造方法

【課題】良好な電気的特性を有する半導体装置及びその製造方法を提供する。

【解決手段】半導体基板10上に形成されたゲート絶縁膜20と、ゲート絶縁膜上に形成されたキャップ膜22と、キャップ膜上に形成されたシリコン酸化膜23と、シリコン酸化膜上に形成された金属ゲート電極24と、金属ゲート電極の両側の半導体基板内に形成されたソース/ドレイン拡散層48とを有している。

(もっと読む)

ヘテロ接合バイポーラトランジスタおよびその製造方法

【課題】ヘテロ接合バイポーラトランジスタのエミッタメサがより正確に形成できるようにする。

【解決手段】第1エミッタ電極107bの側部には、例えば酸化シリコンからなる庇部108が形成され、また、少なくともキャップ層106を含んで構成されたエミッタメサの露出している側面から庇部108の下部の領域のレッジ構造部105aにかけて形成された、例えば窒化シリコンからなる被覆層109が形成されている。被覆層109が、庇部108の側面,庇部108の下面,エミッタメサの側部,およびレッジ構造部105aの上にかけて形成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極への水素の拡散を防止することにより、ゲート絶縁膜の劣化を抑制し、信頼性の高い半導体装置を提供すること。

【解決手段】半導体装置は、ポリシリコンを含むゲート電極と、ゲート電極の少なくとも上面を覆い、水素を貯蔵する機能を有する水素貯蔵層と、を備える。好ましくは、バリア層は、組成式SixNyOZの酸窒化膜を含有し、x:y:z=1:1:0.1〜0.7である。

(もっと読む)

デュアルドープゲートの用途におけるプロフィル制御とN/Pローディングを改善する方法

【課題】プラズマエッチングチャンバ内でデュアルドープゲート構造をエッチングするための方法を提供する。

【解決手段】エッチングされるポリシリコンフィルムを保護するパターンを設ける工程、次いで、プラズマが点火され、保護されていないポリシリコンフィルムのほぼすべてがエッチングされる。次いで、シリコン含有ガスを導入しつつポリシリコンフィルムの残りをエッチングする。また、エッチング処理中にシリコン含有ガスを導入するよう構成されたエッチングチャンバ。

(もっと読む)

半導体装置の製造方法

【課題】サリサイドプロセスにより金属シリサイド層を形成した半導体装置の性能を向上させる。

【解決手段】全反応方式のサリサイドプロセスを用いず、部分反応方式のサリサイドプロセスによりゲート電極8a,8b、n+型半導体領域9bおよびp+型半導体領域10bの表面に金属シリサイド層41を形成する。金属シリサイド層41を形成する際の熱処理では、ランプまたはレーザを用いたアニール装置ではなく、カーボンヒータを用いた熱伝導型アニール装置を用いて半導体ウエハを熱処理することにより、少ないサーマルバジェットで精度良く薄い金属シリサイド層41を形成し、最初の熱処理によって金属シリサイド層41内にNiSiの微結晶を形成する。

(もっと読む)

半導体装置の製造方法

【課題】ゲート電極と第1のコンタクトプラグとが接触する接触幅を充分に確保する。

【解決手段】半導体基板10の上に、エッチングストッパー膜17、第1の層間絶縁膜18及び第2の層間絶縁膜19を順次形成する。次に、第1,第2の層間絶縁膜18,19を貫通し、且つ、エッチングストッパー膜17を露出する第1のホール23を形成する。次に、酸素ガスを含むプラズマを用いたプラズマ処理により、第2の層間絶縁膜19における第1のホール23の側壁に露出する部分を変質して、第1の変質層25を形成する。次に、第1の変質層25を除去して、第2のホール27を形成する。次に、エッチングストッパー膜17における第2のホール27に露出する部分を除去して、第1のコンタクトホール29を形成する。次に、第1のコンタクトホール29に、第1のコンタクトプラグ32Aを形成する。

(もっと読む)

金属窒化膜、該金属窒化膜を用いた半導体装置、および半導体装置の製造方法

【課題】所望の実効仕事関数(例えば、高い実効仕事関数)を実現し、かつ、EOTが変化しない、またはEOTの変化を低減した金属窒化膜、金属窒化膜を用いた半導体装置、および半導体装置の製造方法を提供すること。

【解決手段】本発明の一実施形態に係る金属窒化膜は、TiとAlとNを含有し、該金属窒化膜のTiとAlとNのモル比率(N/(Ti+Al+N))が0.53以上であり、かつ、上記金属窒化物層のTiとAlとNのモル比率(Ti/(Ti+Al+N))が0.32以下であり、かつ上記金属窒化物層のTiとAlとNのモル比率(Al/(Ti+Al+N))が0.15以下である。

(もっと読む)

半導体発光素子の製造方法

【課題】発光効率と信頼性の向上

【解決手段】第2半導体層108上の全面に、透明導電膜10を形成し、形成された透明導電膜の上に、フォトレジストを塗布し、第1半導体層104の電極形成部16の上部のフォトレジストが除去される際に、除去される部分の輪郭部において、残されたフォトレジストの厚さが除去される部分に向かって次第に薄くなるようにフォトレジストを除去する。残されたフォトレジストをマスクとして、透明導電膜をウエットエッチングして、第2半導体層の一部を露出させる。残されたフォトレジスト及び透明導電膜をマスクとして、ドライエッチングして、第1半導体層の電極形成部を露出させる。残されたフォトレジストをマスクとして、透明導電膜のドライエッチングで露出した部分をウエットエッチングし、残されたフォトレジストを除去する。

(もっと読む)

表示装置、電子機器

【課題】アクティブマトリクス型の液晶表示装置の画面の大面積化を可能とするゲート電

極とゲート配線を提供することを第1の課題とする。

【解決手段】同一基板上に表示領域と、表示領域の周辺に設けられた駆動回路と、を有し

、表示領域は、第1の薄膜トランジスタを有し、駆動回路は、第2の薄膜トランジスタを

有し、第1の薄膜トランジスタと第2の薄膜トランジスタは、リンがドープされたシリコ

ンでなるゲート電極を有し、ゲート電極は、チャネル形成領域の外側に設けられた接続部

でアルミニウムまたは銅を主成分とする層とタンタル、タングステン、チタン、モリブデ

ンから選ばれた少なくとも1種を主成分とする層とを有する配線と電気的に接続する。

(もっと読む)

141 - 160 / 947

[ Back to top ]