Fターム[4M104GG06]の内容

Fターム[4M104GG06]に分類される特許

41 - 60 / 275

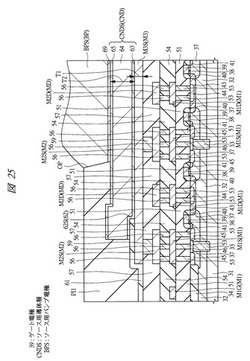

半導体装置およびその製造方法

【課題】電力増幅モジュールの放熱特性を向上させる。

【解決手段】電力増幅モジュールに用いられる電力増幅回路用のLDMOSFET素子が形成された半導体チップにおいて、LDMOSFET素子用の複数のソース領域、複数のドレイン領域および複数のゲート電極39が形成されたLDMOSFET形成領域上に、ソース用バンプ電極BPSを配置する。ソース用バンプ電極BPSは、アルミニウムを主体とするソース用パッドM3S上に、ソース用パッドM3Sよりも厚くかつ銅を主体とするソース用導体層CNDSを介して形成する。ソース用バンプ電極BPSとソース用導体層CNDSの間には樹脂膜は介在していない。

(もっと読む)

銀含有金属オーミック接触電極

【課題】既存の業界工程と互換でき、有効に、生産コストを低減できる銀含有金属オーミック接触電極を提供する。

【解決手段】ニッケル(Ni)層とゲルマニウム(Ge)層、銀(Ag)層、パラジウム(Pd)層或いはプラチナ(Pt)層及び厚い膜金属(Thick Metal)層からなり、順に、n形III-V族化合物半導体層上に堆積されてから、アニール(Anneal)処理を介して形成された構造で、上記銀層とゲルマニウム層との厚さ比例範囲が、Ag/Ge=7〜8の間にある。また、上記の低い電気抵抗率(Electric

Resistivity)と高い熱伝導率(Thermal Conductivity)のオーミック接触電極は、銀が材料として形成される。

(もっと読む)

半導体装置およびその製造方法

【課題】特性の劣化を効果的に抑制することのできる半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、GaNを含む半導体層1と、電極とを備えている。電極は、電極本体6と、半導体層1から見て電極本体6よりも離れた位置に形成され、かつAlを含む接続用電極8と、電極本体6と接続用電極8との間に形成されたW、TiW、WN、TiN、Ta、およびTaNよりなる群から選ばれる少なくとも1種を含むバリア層7とを含んでいる。バリア層7の表面粗さRMSが3.0nm以下である。

(もっと読む)

バイポーラトランジスタ及びその製造方法

【課題】エミッタ接地直流増幅率のばらつきを低減し、かつ抵抗の増大を防止できる、信頼性に優れるバイポーラトランジスタを得ること。

【解決手段】本発明は、N−型エピ層3aやP−型シリコン基板1aを含む半導体基板、N+型ポリシリコン層21a、タングステン層25、シリサイド層27a、シリサイド層39a、ベース電極36a、エミッタ電極36b及びコレクタ電極36cを少なくとも備える。半導体基板上に形成されたN+型ポリシリコン層21aはシリサイド層27aに覆われる。シリサイド層27a上の形成されたタングステン層25はシリサイド層39aに覆われる。

(もっと読む)

半導体装置およびその製造方法

【課題】ソース抵抗を低減できる半導体装置およびその製造方法を提供する。

【解決手段】

基板10上に配置された窒化物系化合物半導体層12と、窒化物系化合物半導体層12上に配置され、アルミニウム窒化ガリウム層18からなる活性領域AAと、活性領域上に配置されたゲート電極24、ソース電極20およびドレイン電極22と、ゲート電極、ソース電極およびドレイン電極が延伸する方向の窒化物系化合物半導体層上に配置され、それぞれゲート電極、ソース電極およびドレイン電極に接続されたゲート端子電極GE1〜GE3、ソース端子電極SE1〜SE4およびドレイン端子電極DEと、ソース端子電極が配置される側の基板の端面に配置され、ソース端子電極と接続され、最外層のエッジが下地金属層よりも後退する3層以上の異なる多層金属を有する端面電極SC1〜SC4とを備え、ダイボンディング半田層がソース端子電極に到達するのを防止する。

(もっと読む)

半導体装置の製造方法

【課題】最新の0.15μmパワーMOSFETにおいては、微細化によるセル・ピッチの縮小のためトレンチ部(ソース・コンタクト用の溝)において、アルミニウム・ボイド(アルミニウム系電極内に形成されるボイド)が多発することが、本願発明者らによって明らかにされた。この欠陥の発生は、主にアスペクト比が前世代の0.84から一挙に2.8に上昇したことによると考えられる。

【解決手段】本願の一つの発明は、アスペクト比の大きい繰り返し溝等の凹部をアルミニウム系メタルで埋め込む際に、アルミニウム系メタル・シード膜の形成から埋め込みに至るまで、イオン化スパッタリングにより、実行するものである。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】本発明によれば、SiCを用いた微細化可能で、超低オン抵抗、かつ信頼性にも優れた半導体装置および半導体装置の製造方法を提供する。

【解決手段】炭化珪素基板と、その第1の主面の第1導電型の第1の炭化珪素層と、この表面の第2導電型の第1の炭化珪素領域と、この表面の第1導電型の第2の炭化珪素領域と、その下部の第2導電型の第3の炭化珪素領域と、第2の炭化珪素領域を貫通し、第3の炭化珪素領域に達するトレンチと、ゲート絶縁膜と、ゲート電極と、ゲート電極を被覆する層間絶縁膜と、トレンチ側面の第2の炭化珪素領域上および層間絶縁膜上に形成されたNi、Ti、Ta、MoおよびWからなる群から選択される金属元素を含有する第1の電極と、トレンチ底部の第3の炭化珪素領域上および第1の電極上に形成されたAlを含有する第2の電極と、第2の電極上の第1の主電極と、炭化珪素基板の第2の主面に形成された第2の主電極と、を有する半導体装置。

(もっと読む)

半導体装置

【課題】開口率の高い半導体装置又はその作製方法を提供することを目的の一とする。また、消費電力の低い半導体装置又はその作製方法を提供することを目的の一とする。

【解決手段】絶縁表面を有する基板上に設けられた半導体層と、半導体層を覆うゲート絶縁膜と、ゲート絶縁膜上に設けられた第1の導電層と第2の導電層とで積層されたゲート電極を含むゲート配線と、半導体層と前記ゲート電極を含む前記ゲート配線を覆う絶縁膜と、絶縁膜上に設けられ、半導体層と電気的に接続され、第3の導電層と第4の導電層とで積層されたソース電極を含むソース配線と、を有し、ゲート電極は、第1の導電層で形成され、ゲート配線は、第1の導電層と第2の導電層で形成され、ソース電極は、第3の導電層で形成され、ソース配線は、第3の導電層と第4の導電層で形成されている。

(もっと読む)

ヘテロ接合バイポーラトランジスタの製造方法

【課題】アスペクト比の高いサブミクロンサイズのエミッタ電極パタンを線幅制御性良く形成することを可能とするヘテロ接合バイポーラトランジスタの製造方法を提供すること。

【解決手段】エミッタコンタクト層6上にTi層(図示せず)、エッチングストッパー用のW層7、Au層8、エッチングマスク用W層9、フォトレジストパタン10を形成し、フォトレジストパタン10をマスクとしてエッチングマスク用W層9を選択的に除去することによってWパタン9とし、Wパタン9をマスクとして、Au層8を、酸素ガスを含有する混合ガスを用いる反応性イオンエッチング法により選択的に除去し、Wパタン9をマスクとして、エッチングストッパー用のW層7、Ti層を選択的に除去することを特徴とするヘテロ接合バイポーラトランジスタの製造方法を構成する。

(もっと読む)

半導体装置

【課題】オン状態にすることが容易な半導体装置を提供する。

【解決手段】半導体チップ10にN型ドリフト層1、P型ベース層2、N型エミッタ層3、N型バッファ層4、P型コレクタ層6、N型コンタクト層7が形成され、半導体チップ10上にP型ベース層2及びN型エミッタ層3に接続されたエミッタ電極11が設けられ、半導体チップ10内にN型エミッタ層3及びP型ベース層2を貫きN型ドリフト層1内に進入したトレンチゲート電極14が埋設され、半導体チップ10とトレンチゲート電極14との間にゲート絶縁膜13が形成され、半導体チップ10の下面上にP型コレクタ層6及びN型コンタクト層7に接続されたコレクタ電極15が設けられたアノードショート型の半導体装置101において、N型バッファ層1とP型コレクタ層6及びN型コンタクト層7との間に、抵抗率がN型バッファ層4の抵抗率よりも高いN型高抵抗層5を設ける。

(もっと読む)

垂直接触電子部品及びその製造方法

本発明は、電子部品に関するもので、接触平面に位置する少なくとも一つの接触表面と、前記接触平面の上方にある少なくとも一つの絶縁層と、該部品の機械的安定性を高めるために、前記絶縁層に接して配置される少なくとも一つの安定化層と、少なくとも一つのボンディング及び/または半田接点とを有し、前記絶縁層及び前記安定化層が少なくとも一つの開口を有し、その開口が、前記接触表面から離れて対向する前記安定化層の一表面に向かって開口するとともに、前記安定化層及び前記絶縁層を通じて前記接触表面まで達し、前記ボンディング及び/または半田接点が、前記安定化層を横切って延び、前記開口を通じて前記接触表面に接する。 (もっと読む)

半導体装置およびその製造方法

【課題】低コストかつ高製造歩留まりで、BiCMOS型半導体集積回路装置を実現することができる半導体装置およびその製造方法を提供する。

【解決手段】シャロートレンチ3、ディープトレンチ6に囲まれた半導体層2の基板領域17に、p型の単結晶半導体からなるエピタキシャル・ベース層24が島状に形成される。当該島状領域を含む半導体層2上の全面に窒化シリコン膜42、酸化シリコン膜43が形成される。島状領域上の異なる位置の窒化シリコン膜42、酸化シリコン膜43には、少なくとも2つの開口部が形成され、開口部が形成された窒化シリコン膜42、酸化シリコン膜43上に半導体膜44が形成される。当該半導体膜44が選択的に除去され、一方の開口部において島状領域に接続するベース電極と、他方の開口部において島状領域に接続するエミッタ電極とが同時に形成される。

(もっと読む)

トレンチ・シールドされた半導体デバイスおよびショットキー・バリア整流デバイスの構造およびそれらを改善するための方法

トレンチ・シールドされた電力用半導体デバイス等の性能を改良するための種々の構造および方法について記載されている。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】ボンディングパッドの剥がれを防止し、かつボンディングパッド間におけるリーク電流の発生を防止することができる半導体装置及びその製造方法を提供すること。

【解決手段】HBT(ヘテロ構造バイポーラトランジスタ)が構成要素の1つとして集積された半導体装置110は、半絶縁性InP基板11上に、順次、エッチングストップ層12、コレクタコンタクト層13、コレクタ層14、傾斜コレクタ層15、セットバック層16、ベース層17が形成された構成を有し、ベース層17はInGaAsで構成された薄膜であってPを含まず、このベース層17上にSiN23が形成され、SiN23上にボンディングパッド25が形成された構成を有する。

(もっと読む)

シリコン基板上に形成されるCMOSデバイスおよびIII−V族デバイスのための電気コンタクト

半導体構造体は、基板(12)と、基板を覆うシード層(13)と、シード層上に配置されるシリコン層(22)と、シリコン層中のトランジスタデバイス(27)と、シード層上に配置されるIII−V族デバイスと、複数の電気コンタクトと、を備え、それぞれの電気コンタクトは、TiNまたはTaNの層(32)と、TaNまたはTiNの層上の銅またはアルミニウムの層(34)と、を備え、電気コンタクトの1つは、トランジスタ(27)に電気的に接続され、電気コンタクトの別の1つは、III−V族デバイスに電気的に接続される。 (もっと読む)

半導体装置および半導体装置の製造方法

【課題】寄生容量を低減しつつ、トランジスタが形成される半導体層に歪応力を与える。

【解決手段】半導体層3に形成されたコレクタ層3aの表面および裏面にストレス印加層5を形成し、ストレス印加層5を介して埋め込み絶縁層6上に配置されたベース層9をコレクタ層3aの側壁に選択的に形成し、ベース層9の側壁を絶縁膜10から露出させる開口部12を形成し、開口部12を介してベース層9の側壁に接続されたエミッタ層13aを埋め込み絶縁層6上に形成する。

(もっと読む)

半導体装置

【課題】電力密度の集中を抑制して発熱の分散を図り、かつ電気位相差を低減した高性能な半導体装置を提供する。

【解決手段】基板上に配置された窒化物系化合物半導体層と、窒化物系化合物半導体層上に配置され、アルミニウム窒化ガリウム層(AlxGa1-xN)(0.1≦x≦1)からなる活性領域と、活性領域を互いに素子分離する素子分離領域と、素子分離領域によって囲まれた活性領域上に配置されたゲート電極24、ソース電極20およびドレイン電極22と、素子分離領域14上に配置され、それぞれゲート電極24,ソース電極20およびドレイン電極22に接続されたゲート端子電極240,ソース端子電極200およびドレイン端子電極220とを備え、ゲート電極24の分岐を再帰的な自己相似のフラクタル図形で構成する。

(もっと読む)

半導体装置、半導体装置の製造方法およびスイッチ回路

【課題】トランジスタのリーク電流の低減。

【解決手段】半導体材料の表面に沿って互いに隣接する複数の電気素子要素と、複数の電気素子要素を覆う、シリコンを含まない下層保護絶縁膜と、下層保護絶縁膜の上に配置され、シリコンを含む上層保護絶縁膜と、を備える半導体装置が提供される。上記半導体装置において、複数の電気素子要素の少なくとも一つは、シリサイド化される金属を含有でき、下層保護絶縁膜は、電気素子要素に含有される金属と上層保護絶縁膜に含有されるシリコンとの接触を阻害できる。下層保護絶縁膜は、比誘電率が10以上の高誘電体層を有してよい。上層保護絶縁膜は、シリコンおよび窒素を含有することができる。

(もっと読む)

縦型半導体装置及びその製造方法

【課題】素子終端領域の占有面積を小さくして阻止特性の安定性を確保でき、必要に応じて、順方向/逆方向の電圧阻止能力を実現できる縦型半導体装置を提供する。

【解決手段】縦型半導体装置は、IGBTの素子機能を実現する素子活性領域100と、素子活性領域100を囲む素子終端領域200とによって構成されている。素子終端領域200には、基板表面に略垂直に、素子活性領域100を取り囲む閉ループ状にトレンチ700が形成されている。トレンチ700は、その側壁に形成されたシリコン酸化膜710と、酸化膜間の隙間を充填する多結晶シリコン720とによって形成されている。さらに、素子終端領域200は、トレンチ700と所定距離を隔てたp−型低不純物濃度層500で終端されている。これによって、素子終端領域200の占有面積を大幅に低減するトレンチ構造において、薄膜の低応力な酸化膜を形成して高耐圧化を図ることができる。

(もっと読む)

半導体装置

【課題】半導体基板内に縦型のスイッチング素子群が設けられている半導体装置において、スイッチング素子領域内の局所的な温度上昇を抑制する。

【解決手段】半導体装置100の半導体基板内に、縦型のスイッチング素子群が設けられているスイッチング素子領域50を備えている。スイッチング素子領域50は、第1領域51と第2領域52を有している。第1領域51には、バイポーラ構造の第1スイッチング素子群が設けられている。第2領域52には、ユニポーラ構造の第2スイッチング素子群が設けられている。第2スイッチング素子群は、第1スイッチング素子群の間に設けられている。

(もっと読む)

41 - 60 / 275

[ Back to top ]