Fターム[4M104GG18]の内容

Fターム[4M104GG18]に分類される特許

81 - 100 / 675

半導体装置及びその作製方法

【課題】酸化物半導体を用いるトランジスタにおいて、電気特性の良好なトランジスタ及びその作製方法を提供する。

【解決手段】下地絶縁膜上に形成される酸化物半導体膜と、当該酸化物半導体膜とゲート絶縁膜を介して重畳するゲート電極と、酸化物半導体膜に接し、ソース電極及びドレイン電極として機能する一対の電極とを備えるトランジスタであり、下地絶縁膜は、酸化物半導体膜と一部接する第1の酸化絶縁膜と、当該第1の酸化絶縁膜の周囲に設けられる第2の酸化絶縁膜とを有し、トランジスタのチャネル幅方向と交差する酸化物半導体膜の端部は、第2の酸化絶縁膜上に位置するものである。

(もっと読む)

半導体装置およびその作製方法

【課題】酸化物半導体膜を用いたトランジスタに安定した電気的特性を付与し、信頼性の高い半導体装置を作製する。

【解決手段】酸化物半導体膜を用いた半導体装置であるトランジスタにおいて、酸化物半導体膜から水素を捕縛する膜(水素捕縛膜)、および水素を拡散する膜(水素透過膜)を有し、加熱処理によって酸化物半導体膜から水素透過膜を介して水素捕縛膜へ水素を移動させる。具体的には、酸化物半導体膜を用いたトランジスタのゲート絶縁膜を、水素捕縛膜と水素透過膜との積層構造とする。このとき、水素透過膜を酸化物半導体膜と接する側に、水素捕縛膜をゲート電極と接する側に、それぞれ形成する。その後、加熱処理を行うことで酸化物半導体膜から脱離した水素を、水素透過膜を介して水素捕縛膜へ移動させることができる。

(もっと読む)

ワイドバンドギャップ半導体における常時オフ集積JFET電源スイッチおよび作成方法

【課題】常時オフVJFET集積電源スイッチを含むワイドバンドギャップ半導体デバイスの提供。

【解決手段】電源スイッチは、モノリシックまたはハイブリッドに実装され得、シングルまたはマルチチップのワイドバンドギャップ電源半導体モジュールにビルトインされた制御回路と一体化され得る。該デバイスは、高電力で温度に対する許容性があり、耐放熱性のエレクトロニクスコンポーネントにおいて用いられ得る。該デバイスを作成する方法もまた、記述される。

(もっと読む)

半導体装置およびその製造方法

【課題】 高周波特性を確保し、サイズを小型化し、かつ製造が容易な、正孔の蓄積を解消できる、耐圧性に優れた、半導体装置等を提供する。

【解決手段】 ヘテロ接合電界効果トランジスタ(HFET:Hetero-junction Field Effect Transistor)であって、非導電性基板1上に位置する、チャネルとなる二次元電子ガス(2DEG:2 Dimensional Electron Gas)を形成する再成長層7(5,6)と、再成長層に接して位置する、ソース電極11、ゲート電極13およびドレイン電極15を備え、ソース電極11が、ゲート電極13に比べて、非導電性基板1から遠い位置に位置することを特徴とする。

(もっと読む)

半導体素子及び半導体素子の製造方法

【課題】3次元形の半導体素子において、オン抵抗をより効果的に低減できる半導体素子及び半導体素子の製造方法を提供する。

【解決手段】半導体素子は、ドレイン層と、ドレイン層内に選択的に設けられたドリフト領域と、ドリフト領域内に選択的に設けられたベース領域と、ベース領域内に選択的に設けられたソース領域と、ソース領域又はドレイン層の少なくとも一方の内部に、ソース領域又はドレイン層の少なくとも一方に選択的に設けられた第1,第2の金属層と、ドレイン層の表面に対して略平行な方向に、ソース領域の一部から、ソース領域の少なくとも一部に隣接するベース領域を貫通して、ドリフト領域の一部にまで到達するトレンチ状のゲート電極と、第1の金属層に接続されたソース電極と、ドレイン層又は第2の金属層に接続されたドレイン電極と、を備える。

(もっと読む)

半導体装置およびその製造方法

【課題】オン抵抗が低く、高いアバランシェ耐量を有する半導体装置およびその製造方法を提供することである。

【解決手段】実施形態の半導体装置は、第1半導体層と、複数のベース領域と、ソース領域と、トレンチ内に、ゲート絶縁膜を介して設けられたゲート電極と、トレンチ内において、ゲート電極の下にフィールドプレート絶縁膜を介して設けられたフィールドプレート電極と、第1主電極と、第2主電極と、を備える。フィールドプレート絶縁膜の一部の厚さは、ゲート絶縁膜の厚さよりも厚く、一対のトレンチ内に設けられたフィールドプレート絶縁膜の一部どうしの間の第1半導体層の幅は、一対のトレンチ内に設けられたゲート絶縁膜どうしの間のベース領域の幅よりも狭く、第1半導体層と、フィールドプレート絶縁膜の一部と、の界面の直上には、ソース領域が形成されていない。

(もっと読む)

半導体装置及びその製造方法

【課題】低いオン抵抗を維持したまま、耐圧の向上を図ることができる半導体装置及びその製造方法を提供する。

【解決手段】実施形態に係る半導体装置は、第1半導体領域、第2半導体領域、第3半導体領域、制御電極、第1主電極、内部電極、絶縁領域、を備える。制御電極は、トレンチの内側に設けられる。第1主電極は、第3半導体領域と導通し、トレンチの外側に設けられる。内部電極は、トレンチ内に設けられ、第1主電極と導通する。絶縁領域は、トレンチの内壁と第1主電極とのあいだ、及びトレンチの内壁と内部電極とのあいだ、に設けられる。内部電極は、制御電極よりもトレンチの底面側の第1領域に含まれる第1内部電極部と、第1領域と、第1主電極と、のあいだの第2領域に含まれる第2内部電極部と、を有する。第1内部電極部とトレンチの内壁との間隔は、第2内部電極部とトレンチの内壁との間隔よりも広い。

(もっと読む)

半導体素子、半導体素子の製造方法、およびトランジスタ回路

【課題】高電子移動度トランジスタの耐圧を高くする。

【解決手段】第1の高電子移動度トランジスタ4と、負の閾値電圧を有する第2の高電子移動度トランジスタ6とを有し、第2の高電子移動度トランジスタ6のソースS2は、第1の高電子移動度トランジスタ4のゲートG1に接続され、第2の高電子移動度トランジスタ6のゲートG2は、第1の高電子移動度トランジスタ4のソースS1に接続されている。

(もっと読む)

高耐圧半導体装置

【課題】高耐圧半導体装置の大型化を招くことなく、従来の高耐圧半導体装置900の場合よりも「気中放電による逆耐圧の低下」を抑制することが可能な高耐圧半導体装置を提供する。

【解決手段】炭化珪素からなるn型の半導体層110と、バリアメタルからなる第1電極層層128と、第2電極層130と、p型のリサーフ層116と、p+型のエッジターミネーション層120と、リサーフ層116の内部における、エッジターミネーション層120の周囲を離間して囲む位置に形成されたp+型の第1ガードリング層122と、半導体層110の表面における、リサーフ層116の周囲を離間して囲む位置に形成されたp型の第2ガードリング層118と、半導体層110の表面上において第1電極層128を取り囲む領域に形成された絶縁層124とを備え、第2ガードリング層118が絶縁層124の外周近傍まで形成されている高耐圧半導体装置100。

(もっと読む)

半導体素子及び半導体素子の製造方法

【課題】SiC半導体装置において、不純物添加工程や表面保護膜形成におけるプロセス条件のばらつきがあっても、簡便に逆方向耐圧に大きな影響を与えないターミネーション構造(接合終端構造)を提供する。

【解決手段】素子の外周端部に、第1導電型の耐圧維持層および有限長さの前記第1導電型とは異なる第2導電型の領域からなる接合終端構造を備えたSiC半導体素子であって、前記接合終端構造の一部において、第1の方向である層方向に対して均一ではなく、前記接合終端領域の内側端であって前記素子の外周端から前記接合終端領域の外側端に向かって、前記第1導電型領域の不純物濃度が空間的に変調され、不純物濃度が徐々に減少する傾向を持って形成された接合終端構造を有することを特徴とするSiC半導体素子。

(もっと読む)

半導体装置の製造方法

【課題】本発明は、製造コストの増大を抑制しつつ、簡易な構成で、絶縁膜とさらに上部に形成された絶縁膜との界面の電荷を低減することができる半導体装置の製造方法の提供を目的とする。

【解決手段】本発明にかかる半導体装置の製造方法は、(a)SiC半導体を用いた基板を用意する工程と、(b)前記基板の表層部において、前記基板の素子領域を囲むように、リセス構造と前記リセス構造の下部にガードリング層とを形成する工程と、(c)前記ガードリング層を覆って、第1絶縁膜を形成する工程と、(d)前記第1絶縁膜を覆って、前記第1絶縁膜とは異なる材質の第2絶縁膜を形成する工程と、(e)前記第1絶縁膜上に蓄積する電荷とは逆電荷のイオンを、前記工程(d)の前、又は、前記工程(d)中、又は前記工程(d)の後に照射する工程とを備える。

(もっと読む)

半導体装置

【課題】耐圧劣化を防止するとともに低コストで製造可能な構造を備える半導体装置を提供する。

【解決手段】半導体基板と、基板上に形成される炭化珪素からなる第1導電型の半導体層と、半導体層の表面に形成される活性領域と、活性領域を取り囲むように、半導体層の表面に形成される第2導電型の第1の半導体領域と、半導体層の表面に第1の半導体領域の外側に接し、第1の半導体領域を取り囲んで設けられ、第1の半導体領域と同一の不純物濃度および同一の深さを有する第2導電型の不純物領域がメッシュ形状に形成される第2の半導体領域と、活性領域上に設けられる第1の電極と、半導体基板の裏面に設けられる第2の電極を備えることを特徴とする半導体装置である。

(もっと読む)

半導体装置

【課題】半導体装置内に保護ダイオードをレイアウトする。

【解決手段】半導体装置は、電界効果トランジスタ11と、電界効果トランジスタ11の形成領域30に隣接するダイオード形成領域12とを備え、ダイオード形成領域12はトランジスタの形成領域30と半導体基板上で絶縁され、ダイオード形成領域12内において、電界効果トランジスタ11のゲート電極1がバス配線7を介して半導体基板とショットキー接合とオーミック接合のいずれか又は両方の接合をする第1のダイオード電極20と、電界効果トランジスタ11のソース電極2がパッド5を介して半導体基板とオーミック接合とショットキー接合のいずれか又は両方の接合をする第2のダイオード電極21とを備えることによってゲート電極1とソース電極2間にダイオードが形成されたことを特徴とする。

(もっと読む)

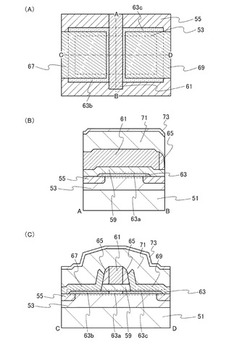

半導体装置および半導体装置の作製方法

【課題】トランジスタのチャネル部が形成される領域にU字状の縦長溝を形成し、見かけ上のチャネル長に対してチャネル長を長くする方法は、溝を掘るためにフォトリソグラフィ工程を余分に行う必要があり、コストや歩留まりの観点で問題があった。

【解決手段】ゲート電極または絶縁表面を有する構造物を利用し、三次元形状のチャネル領域を形成することにより、チャネル長が、上面から見たチャネル長に対して3倍以上、好ましくは5倍以上、さらに好ましくは10倍以上の長さとする。

(もっと読む)

電界効果トランジスタとその製造方法

【課題】電界効果トランジスタとその製造方法において、電界効果トランジスタの耐圧を高めつつそのオン抵抗を低減すること。

【解決手段】基板1と、基板1の上に形成され、複数の第1の半導体層3と複数の層間絶縁層4とが交互に積層された積層体10と、積層体10の側面10aに形成されると共に、該側面10aにおいて複数の第1の半導体層3の各々に接続された第2の半導体層12と、第2の半導体層12の上に形成されたゲート絶縁層17と、ゲート絶縁層17の上に形成され、ゲート絶縁層17を介して側面10aに対向するゲート電極19と、第2の半導体層12に電気的に接続されたソース電極14と、複数の第1の半導体層3の各々に電気的に接続されたドレイン電極15とを有する電界効果トランジスタによる。

(もっと読む)

半導体装置とその製造方法

【課題】高耐圧な半導体素子を提供することを目的とする。

【解決手段】 実施形態の半導体装置は、第一と第二の主面を有する炭化珪素基板と、炭化珪素基板の第一の主面に設けられた第一導電型の第一の炭化珪素層と、第一の炭化珪素層の表面に形成された第二導電型の第一の炭化珪素領域と、第一の炭化珪素領域の表面に形成された第一導電型の第二の炭化珪素領域と、第一の炭化珪素領域の表面に形成された第二導電型の第三の炭化珪素領域と、第一の炭化珪素層、第一の炭化珪素領域および第三の炭化珪素領域の表面に連続的に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成された炭化珪素からなる第一の電極と、第一の電極上に形成された第二の電極と、第一と第二の電極を被覆する層間絶縁膜と、第二の炭化珪素領域と第三の炭化珪素領域と電気的に接続される第三の電極と、炭化珪素基板の第二の主面に形成された第4の電極と、を具備することを特徴とする。

(もっと読む)

ドリフト領域とドリフト制御領域とを有する半導体素子

【課題】低いオン抵抗を有するドリフト経路/ドリフト領域を有する、半導体素子、特にパワー半導体素子を提供する。

【解決手段】半導体基材100と、上記半導体基材100内の、半導体材料からなるドリフト領域2と、ドリフト領域2に対し、少なくとも部分的に隣り合って配置され、接続電極19を含む、半導体材料からなるドリフト制御領域3と、ドリフト領域2とドリフト制御領域3との間に配置された蓄積誘電体4と、第1素子領域8と、第1素子領域8との間にドリフト領域2が配置され、第1素子領域8から離れて配置された第2素子領域5と、ドリフト制御領域3の接続電極19および第1素子領域8の間に接続された容量性素子50とを含む。

(もっと読む)

半導体装置およびその製造方法

【課題】ショットキーバリアダイオードの逆リーク電流を低減させる。

【解決手段】禁制帯幅の異なるGaN膜3a、3bとバリア膜4a、4bとを交互に積層して形成したヘテロ接合体5a、5bを有する積層体6と、積層体6の一方の側壁にショットキー接続された第1電極8と、もう一方の側壁に接して形成された第2電極10とを有する半導体装置において、第1電極8とバリア膜4a、4bとの間に酸化膜12を設ける。これにより、バリア膜4a、4bの加工に起因してバリア膜4a、4bに残留する欠陥にを介して逆リーク電流が流れることを防ぐ。

(もっと読む)

半導体装置の製造方法

【課題】信頼性と電気的特性の確保を両立した半導体装置を提供する。

【解決手段】同一の半導体基板1上に形成されたパワーMOSFETと保護回路を備える。パワーMOSFETがトレンチゲート縦型PチャネルMOSFETであって、そのゲート電極6の導電型をP型とする。また、保護回路がプレーナゲート横型オフセットPチャネルMOSFETを備え、そのゲート電極10の導電型をN型とする。これらゲート電極6とゲート電極10は別工程で形成される。

(もっと読む)

表示装置および半導体装置用Al合金膜

【課題】450〜600℃程度の高温下に曝されてもヒロックが発生せず高温耐熱性に優れており、膜自体の電気抵抗(配線抵抗)も低く、アルカリ環境下の耐食性にも優れた表示装置用Al合金膜を提供する。

【解決手段】Geを0.01〜2.0原子%と、Ta、Ti、Zr、Hf、W、Cr、Nb、Mo、Ir、Pt、Re、およびOsよりなる群(X群)から選択される少なくとも一種の元素とを含み、450〜600℃の加熱処理を行なったとき、下記(1)の要件を満足する表示装置もしくは半導体装置用Al合金膜である。

(1)Alと、前記X群から選択される少なくとも一種の元素と、Geとを含む第1の析出物について、円相当直径50nm以上の析出物が200,000個/mm2以上の密度で存在する。

(もっと読む)

81 - 100 / 675

[ Back to top ]