Fターム[4M104GG18]の内容

Fターム[4M104GG18]に分類される特許

61 - 80 / 675

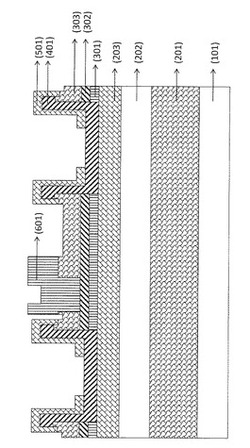

HEMT装置を製造するCMOSコンパチブルな方法とそのHEMT装置

【課題】Si−CMOSプロセス時術とコンパチブルなHEMT装置の製造法を提供する。

【解決手段】基板101を提供するステップと、III族窒化物層のスタックを基板上に形成するステップと、窒化シリコンからなり、スタックの上方層に対して上に位置すると共に当接する第1パッシベーション層301を形成し、第1パッシベーション層が、現場でスタックに堆積されるステップと、第1パッシベーション層に対して上に位置すると共に当接する誘電体層を形成するステップと、窒化シリコンからなり、誘電体層に対して上に位置すると共に当接する第2パッシベーション層303を形成し、第2パッシベーション層が、LPCVD、MOCVD又は同等の手法によって450℃より高い温度で堆積されるステップと、ソースドレイン・オーミック接触とゲート電極601を形成するステップとを備える。

(もっと読む)

炭化珪素半導体を用いたMOS構造およびその酸化膜形成方法

【課題】 SiO2/SiC界面における界面準位自体を低減することが出来るSiC半導体を用いたMOS構造、およびその酸化膜の形成方法を提供する。

【解決手段】 SiC半導体基板1を処理炉内に用意し、処理炉内を比較的低い700℃に設定して、SiC半導体基板1の基板表面を酸素ガス雰囲気中にさらす。この熱酸化により、SiC半導体基板1の基板表面には、SiO2から成る中間層2が約1nmの極薄い厚さで形成される。次に、中間層2上にSiO2膜を約50nmの厚さに堆積して、SiO2から成る堆積層3を形成する。次に、SiC半導体基板1が酸化しない温度および時間で、堆積層3をアニーリングする。このアニーリングは、赤外線ランプなどの急速加熱装置により、SiO2膜の融点である1200℃に近い、この1200℃の融点よりも低い例えば1000〜1100℃程度の温度で、短時間に急速に行われる。

(もっと読む)

シリコンカーバイドから製造されるモノリシックな縦型接合型電界効果トランジスタおよびショットキーバリアダイオード、および、その製造方法

【課題】縦型接合型電界効果トランジスタ(JFET)およびショットキーバリアダイオード(SBD)を備えるスイッチング素子を提供すること。

【解決手段】自己整合縦型接合型電界効果トランジスタを、エッチング注入ゲートおよび集積逆並列ショットキーバリアダイオードと組み合わせたスイッチング素子が、記載されている。ダイオードのアノードは、漂遊インダクタンスによる損失を低減するために、デバイスレベルでトランジスタのソースに接続される。SBDアノード領域におけるSiC表面は、SBDのターンオン電圧と関連するパワー損失が低減されるよう低いショットキーバリア高さを達成するために、乾式エッチングによって調整される。

(もっと読む)

半導体装置の製造方法

【課題】ワイドバンドギャップ半導体層とメタル電極のコンタクト抵抗を低減することができる半導体装置の製造方法を得る。

【解決手段】まず、シリコンに比べてバンドギャップが大きいIII−V族化合物半導体又はIV−IV族化合物半導体からなるp型窒化ガリウム層1の表面に、3−ヘリウム又は4−ヘリウムのイオンを照射してイオン照射領域2を形成する。イオン照射領域2を形成した後に、p型窒化ガリウム層1の表面にオーミックコンタクトしたメタル電極3を形成する。

(もっと読む)

パワーモジュールおよび電力変換回路

【課題】電力変換回路の性能を高める。

【解決手段】ユニット10は、半導体スイッチ素子1,2と、ダイオード3,4とを備える。ダイオード3は、半導体スイッチ素子2がオン状態である時に逆バイアスされ、半導体スイッチ素子2がオフ状態である時に導通する。ダイオード4は、半導体スイッチ素子1がオン状態である時に逆バイアスされ、半導体スイッチ素子1がオフ状態である時に導通する。ダイオード3,4は、窒化ガリウム(GaN)ダイオードまたはダイヤモンドダイオードである。ユニット10を備えるパワーモジュールは、コンバータ、インバータ等の電力変換回路に適用される。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】縦型トランジスタの特性にばらつきが生じることを抑制する。

【解決手段】半導体基板100には縦型MOSトランジスタ20が形成されている。半導体基板100の表面上には、第1層間絶縁膜300及び第1ソース配線312が形成されている。第1ソース配線312は、第1層間絶縁膜300上に形成されており、平面視で縦型MOSトランジスタ20と重なっている。第1層間絶縁膜300にはコンタクト302が埋め込まれている。コンタクト302は、縦型MOSトランジスタ20のn型ソース層140と第1ソース配線312とを接続している。そして第1ソース配線312には、複数の開口316が形成されている。

(もっと読む)

半導体装置

【課題】大電力の制御を行う、高耐圧の半導体装置を提供する。

【解決手段】ゲート電極と、ゲート電極上のゲート絶縁層と、ゲート絶縁層上の、ゲート電極と重畳する酸化物半導体層と、酸化物半導体層と接し、端部をゲート電極と重畳するソース電極及びドレイン電極と、を有し、ゲート電極と酸化物半導体層が重畳する領域において、ゲート絶縁層は、ドレイン電極と端部を重畳する第1の領域と、前記第1の領域と隣接する第2の領域と、を有し、第1の領域の静電容量は第2の領域の静電容量より小さいトランジスタを提供すること。

(もっと読む)

相互接続構造の珪化物層およびロープロファイルバンプを有するパワーMOSFETを形成する半導体デバイスおよび方法

【課題】相互接続構造の珪化物層と、ロープロファイルバンプを含む、バンプ間ショートを防止したパワーMOSFETからなる半導体デバイスおよび製造方法を提供する。

【解決手段】基板上にソース領域160およびドレイン領域170を有し、珪化物層174が、ソース領域およびドレイン領域の上に配置されている。第1の相互接続層194が、珪化物層上に形成されており、ソース領域に接続される第1のランナー196と、ドレイン領域に接続される第2のランナー198とが配置される。第2の相互接続層214が、第1の相互接続層上に形成されており、第1のランナーに接続される第3のランナー216と、第2のランナーに接続される第4のランナー218とを含む。第3の相互接続層234が形成され、ソースパッド236、ソースバンプ240が電気的に接続される。

(もっと読む)

半導体装置

【課題】冷却効率を向上させることができる半導体装置を提供すること。

【解決手段】実施形態に係る半導体装置10は、裏面に複数の凹部16を有するシリコン基板11と、この基板11の表面上に形成された半導体層12と、半導体層12の表面上に、互いに離間して形成されたドレイン電極13およびソース電極14と、ドレイン電極13とソース電極14との間の半導体層12上に形成されたゲート電極15と、複数の凹部16の内部を含むシリコン基板11の裏面全体に形成された裏面金属17と、を具備する。

(もっと読む)

半導体装置の製造方法

【課題】炭化珪素単結晶基板を用いた半導体装置の製造方法において、炭化珪素表面の金属汚染を十分除去することにより、製造された炭化珪素半導体素子の初期特性を改善する。また、金属汚染を低減し、半導体装置の長期信頼性を向上する方法を提供する。

【解決手段】炭化珪素単結晶基板を用いた半導体装置の製造方法において、炭化珪素表面を酸化するステップと、該ステップにより炭化珪素表面に形成された二酸化シリコンを主成分とする膜を除去するステップとからなる炭化珪素表面の金属汚染除去工程を適用する。

(もっと読む)

半導体装置及びその製造方法

【課題】シンカー層を含むエピタキシャル層の厚さを増大させても耐圧性能の向上が可能な半導体装置及びその製造方法を提供する。

【解決手段】半導体装置1は、第1導電型の埋め込み拡散層16Na,16Nd,16Nbを有する支持基板10と、第1導電型と同じ導電型のシンカー層21Na,21Nbを有するエピタキシャル層20と、シンカー層21Na,21Nbから離れた領域でエピタキシャル層20上に形成された電極層31とを備える。支持基板10の上層部は、エピタキシャル層の上面に向けて突出する凸状部10Pa,10Pbを有し、シンカー層21Na,21Nbは、エピタキシャル層20の上面近傍から凸状部10Pa,10Pbにおける埋め込み拡散層16Na,16Nbにまで延在する不純物拡散領域からなる。

(もっと読む)

半導体装置の製造方法と半導体装置

【課題】半導体基板の表面のAl層の表面が荒れることを抑制しつつ、リフトオフの後に溶解層が剥離せずに残ることを防止し得る半導体装置の製造方法を提供する。

【解決手段】半導体基板12の表面にAl層14を形成し、Al層14の表面にTiN層16を形成し、TiN層16の表面の一部に絶縁層20を形成し、TiN層16と絶縁層20の表面に溶解層を形成し、溶解層の表面にレジスト層を形成し、溶解層とレジスト層の一部を除去して溶解層開口部を形成してTiN層16の一部を露出させ、レジスト層の表面、及び、露出したTiN層16の一部の表面にTi層30及びNi層40を形成し、アルカリ溶液によって溶解層を溶解させることにより、溶解層とともに、レジスト層とその表面に形成されたTi層及びNi層を除去する。

(もっと読む)

半導体電極構造

【課題】半導体装置の製造工程で高温下に曝された場合であっても、ヒロックの発生が抑制されて耐熱性に優れ、かつ膜自体の電気抵抗率が低く抑えられたAl合金膜を有する半導体電極構造を提供する。

【解決手段】基板上に少なくとも、基板側から順に、高融点金属薄膜と、Al合金膜とを備えた半導体電極構造であって、前記Al合金膜は、480℃で30分間保持する加熱処理を行った後に下記(a)〜(c)を全て満たし、かつ膜厚が1〜5μmであることを特徴とする半導体電極構造。

(a)Alマトリックスの最大粒径が1μm以下

(b)ヒロック密度が1×109個/m2未満

(c)電気抵抗率が10μΩcm以下

(もっと読む)

半導体装置

【課題】本発明は、トレンチの設計自由度が損なわれることなく、プロセス条件に制約されることなく、電気的特性を向上することができる半導体装置を提供する。

【解決手段】半導体装置10は、第1の半導体領域1内のトレンチ15の底部に第4の半導体領域4を介して配設され、隣り合う同士において相互に離間され、第1の半導体領域1よりも高い不純物密度を有する第1の導電型の第5の半導体領域5を備える。

(もっと読む)

半導体電極構造

【課題】半導体装置の製造工程で高温下に曝された場合であっても、ヒロックの発生が抑制されて耐熱性に優れ、かつ膜自体の電気抵抗率が低く抑えられたAl合金膜を有する半導体電極構造を提供する。

【解決手段】基板上に少なくとも、基板側から順に、高融点金属の窒化物薄膜と、Al合金膜とを備えた半導体電極構造であって、前記Al合金膜は、500℃で30分間保持する加熱処理を行った後に下記(a)〜(c)を全て満たし、かつ膜厚が300nm〜5μmであることを特徴とする半導体電極構造。(a)Alマトリックスの最大粒径が1μm以下(b)ヒロック密度が1×109個/m2未満(c)電気抵抗率が10μΩcm以下

(もっと読む)

半導体装置の製造方法

【課題】電極パターンが基板支持台に直接押し付けられることによって生じる電極パターンへのダメージの発生を防止することができる半導体装置の製造方法を提供する。

【解決手段】半導体基板40の表面S1上に電極パターン41が形成される。半導体基板40の表面S1上において電極パターン41を覆う絶縁膜43が形成される。成膜装置の基板支持台100上に、絶縁膜43が基板支持台100に接するように半導体基板40が取り付けられる。基板支持台100に取り付けられた半導体基板40の裏面上に成膜装置によって電極層44が堆積される。電極層44が堆積された後に、電極パターン41の少なくとも一部が露出するように絶縁膜43がパターニングされる。

(もっと読む)

窒化物半導体素子及びその製造方法

【課題】FETのソース領域にショットキー電極を形成し、ゲート電極をソース電極の一部領域と窒化物半導体領域の一部に形成し、ドレイン電極と該ソース電極との間にフローティングガードリングを設けることによって、ノーマリ−オフで動作する半導体素子を提供する。

【解決手段】内部に2次元電子ガス(2DEG)チャネルを形成する窒化物半導体層30と、窒化物半導体層30にオーミック接合されたドレイン電極50と、ショットキー接合されたソース電極60と、ドレイン電極50とソース電極60との間で窒化物半導体層30にショットキー接合されたフローティングガードリング75と、ドレイン電極50とソース電極60との間及びソース電極60の少なくとも一部上にかけて形成された誘電層40と、誘電層40上に形成され、一部が、誘電層40を挟んでソース電極60のドレイン方向のエッジ部分上に形成されたゲート電極70とを含む。

(もっと読む)

窒化物半導体素子及びその製造方法

【課題】オン抵抗を低め、高電流で動作する半導体素子及び製造方法を提供する。

【解決手段】基板10上部に配設され、内部に2次元電子ガスチャネルを形成する窒化物半導体層30と、窒化物半導体層30にオーミック接合されたドレイン電極50と、ドレイン電極50と離間して配設され、窒化物半導体層30にショットキー接合されたソース電極60と、ドレイン電極50とソース電極60との間の窒化物半導体層30上及びソース電極60の少なくとも一部上にかけて形成され、ドレイン電極50とソース電極60との間にリセスを形成する誘電層40と、ドレイン電極50と離間して誘電層40上及びリセスに配設され、一部が誘電層40を挟んでソース電極60のドレイン方向へのエッジ部分上部に形成されたゲート電極70とを含む。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体を用いるトランジスタにおいて、電気特性の良好なトランジスタ及びその作製方法を提供する。

【解決手段】下地絶縁膜上に形成される酸化物半導体膜と、当該酸化物半導体膜とゲート絶縁膜を介して重畳するゲート電極と、酸化物半導体膜に接し、ソース電極及びドレイン電極として機能する一対の電極とを備えるトランジスタであり、下地絶縁膜は、酸化物半導体膜と一部接する第1の酸化絶縁膜と、当該第1の酸化絶縁膜の周囲に設けられる第2の酸化絶縁膜とを有し、トランジスタのチャネル幅方向と交差する酸化物半導体膜の端部は、第2の酸化絶縁膜上に位置するものである。

(もっと読む)

トレンチ絶縁ゲート型半導体装置

【課題】セル領域が接する平行トレンチ部分と接しない平行トレンチ部分の表面間隔が異なるトレンチ表面パターンを有していても、耐圧低下がなく、低オン電圧が得られるトレンチ絶縁ゲート型半導体装置を提供すること。

【解決手段】トレンチ9の表面間隔の異なる平行トレンチ部分9a同士は斜行トレンチ部分9bによって交差すること無く連結されるトレンチ表面パターンを備え、前記平行トレンチ部分9aの側壁面の面方位が、前記主面の面方位(100)と直交する等価な面方位{100}であるトレンチ絶縁ゲート型半導体装置。

(もっと読む)

61 - 80 / 675

[ Back to top ]