Fターム[4M104GG18]の内容

Fターム[4M104GG18]に分類される特許

121 - 140 / 675

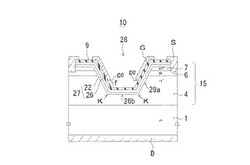

半導体装置およびその製造方法

【課題】 開口部が設けられ、当該開口部に二次元電子ガスで形成されるチャネルを備える縦型半導体装置の耐圧性能を向上させることを目的とする。

【解決手段】開口部28が設けられたGaN系積層体15を備える縦型の半導体装置であって、n型GaN系ドリフト層4/p型GaN系バリア層6/n型GaN系コンタクト層7、を備え、開口部を覆うように電子走行層22および電子供給層26を含む再成長層27と、ソース電極Sと、再成長層上に位置するゲート電極Gとを備え、ゲート電極Gは、p型GaNバリア層の厚み範囲に対応する部分を覆い、かつ開口部の底部から離れた位置の壁面内で終端している。

(もっと読む)

半導体装置の製造方法

【課題】本発明は、製造工程の煩雑化および製造プロセスの長時間化を抑制できると共に、量産性に優れた半導体装置の製造方法を提供する。

【解決手段】本発明に係る半導体装置の製造方法では、ゲート電極7上に、積層膜19を形成する。そして、層間絶縁膜8形成後、層間絶縁膜8等に対してエッチング処理を施す。これにより、ソース領域3およびp+ベースコンタクト領域5が底面から露出した第1のコンタクトホール12を形成すると同時に、積層膜19が底面から露出した第2のコンタクトホール13を形成する。ここで、当該エッチング処理は、積層膜19のエッチングレートが層間絶縁膜8のエッチングレートよりも遅くなるエッチング条件により、実施する。

(もっと読む)

パターン転写方法及びパターン転写装置、これを適用したフレキシブルディスプレイパネル、フレキシブル太陽電池、電子本、薄膜トランジスター、電磁波遮蔽シート、フレキシブル印刷回路基板

【課題】パターン転写方法及びパターン転写装置、これを適用したフレキシブルディスプレイパネル、フレキシブル太陽電池、電子本、薄膜トランジスター、電磁波遮蔽シート、フレキシブル印刷回路基板を提供する。

【解決手段】本発明によるパターン転写方法は、基板上にパターン物質を形成する第1段階と、パターン物質を固相状態に硬化させる第2段階と、硬化された固相状態のパターン物質にレーザー光を照射して、パターン物質をパターニングする第3段階と、パターニングされた固相状態のパターン物質と柔軟基板をお互いに突き合わせて加圧して、パターン物質から柔軟基板方向に、または柔軟基板からパターン物質方向にレーザー光を照射して、パターン物質と柔軟基板を突き合わせた部位で発生する柔軟基板の粘性力によって、パターン物質を柔軟基板に転写する第4段階と、を含む。

(もっと読む)

半導体装置

【課題】ゲート抵抗の増大を抑制しつつ、外部ウェルがトレンチゲート電極によってセル領域のウェルから分断されてしまうことを抑制する。

【解決手段】埋込ゲート電極140のうち平面視でゲートコンタクト領域102と重なる方向に延伸している埋込ゲート電極142は、ゲート電極310と重ならないように、ゲート電極310の手前までしか延伸していない。また埋込ゲート電極142の相互間に位置するソースコンタクトは、図中上下方向において、埋込ゲート電極142よりも短く形成されている。そして埋込ゲート電極142のうちゲート電極310側の端部は、ゲート電極310の手前に設けられた接続用埋込電極141によって互いに接続されている。接続用埋込電極141は、半導体装置の長辺と平行な方向に延伸している。接続用埋込電極141は、埋込ゲート電極142の隣に位置する埋込ゲート電極144には接続していない。

(もっと読む)

半導体装置

【課題】トレードオフの関係にある臨界オフ電圧上昇率dV/dtとゲート感度との関係を改善した半導体装置を提供する。

【解決手段】少なくとも、ゲートトリガ電流IGTの経路となるベース層(P型ベース領域、P型半導体領域P1)のゲート電極M1bとのオーミック接触面である高濃度不純物層を、高融点金属シリサイド層LMで形成する。

(もっと読む)

電界効果トランジスタ及びその製造方法

【課題】本発明は、トランジスタ特性の再現性が高く、高速でパワーの大きい電界効果トランジスタ及びその製造方法を提供することを課題とする。

【解決手段】ダイヤモンド基板11と、前記ダイヤモンド基板11の一面11a側に離間して形成された第2の電極13及び第3の電極14と、2つの電極13、14の間に離間して形成された第1の電極15と、を有する電界効果トランジスタであって、第1の電極15とダイヤモンド基板11との間にIII族窒化物半導体層12が設けられ、ダイヤモンド基板11とIII族窒化物半導体層12との界面17の近傍領域に正孔伝導チャネル領域16が形成されている電界効果トランジスタ10を用いることによって前記課題を解決できる。

(もっと読む)

薄膜トランジスタ及び液晶表示装置の作製方法

【課題】作製工程を大幅に削減し、低コストで生産性の良い液晶表示装置を提供する。消費電力が少なく、信頼性の高い液晶表示装置を提供する。

【解決手段】ゲート配線上の一部を含む半導体層のエッチングと、画素電極とドレイン電極を接続するためのコンタクトホールの形成を、同一のフォトリソグラフィ工程及びエッチング工程で行うことで、フォトリソグラフィ工程を削減する。これにより露出したゲート配線の一部を絶縁層で覆い、これに液晶層の間隔を維持するスペーサを兼ねさせる。フォトリソグラフィ工程を削減することにより、低コストで生産性の良い液晶表示装置を提供することができる。また、半導体層に酸化物半導体を用いることで、消費電力が低減され、信頼性の高い液晶表示装置を提供することができる。

(もっと読む)

ダイヤモンド電子素子及びその製造方法

【課題】欠陥密度が低減したドリフト層を有する高出力ダイヤモンド電子素子を提供する。

【解決手段】ダイヤモンド半導体からなるドリフト層と、半絶縁性ダイヤモンド層を有する構造保持材と、ダイヤモンド半導体からなるコンタクト層とを備えるダイヤモンド電子素子であって、前記構造保持材は、開口部を有し、前記ドリフト層の一方の面に積層されており、前記コンタクト層は、前記開口部内において、前記ドリフト層に直接積層されており、また、アノード電極は、前記開口部内の前記コンタクト層に設け、カソード電極は前記ドリフト層の他方の面に設けて、例えば、ショットキーバリアダイオードを実現する。単結晶ダイヤモンド基板の一方の基板面に欠陥層を形成した後、該基板面上に前記ドリフト層を成膜し、半絶縁性ダイヤモンド層を選択的に成長させて開口部を有する構造保持材を形成した後、前記基板はスマートカット法により素子部より分離する。

(もっと読む)

半導体装置の製造方法

【課題】金属半導体化合物電極の界面抵抗を低減する半導体装置の製造方法を提供する。

【解決手段】実施の形態によればn型半導体上に硫黄を含有する硫黄含有膜を堆積し、硫黄含有膜上に第1の金属を含有する第1の金属膜を堆積し、熱処理によりn型半導体と第1の金属膜を反応させて金属半導体化合物膜を形成するとともに、n型半導体と金属半導体化合物膜との界面に硫黄を導入することを特徴とする半導体装置の製造方法である。

(もっと読む)

窒化ガリウム系半導体素子及び窒化ガリウム系半導体素子の製造方法

【課題】窒化ガリウム系半導体素子及びその製造方法を提供する。

【解決手段】導電性放熱基板(すなわち、熱伝導性基板)、放熱基板上に備わったGaN系多重層及びGaN系多重層上に備わったショットキー電極を含む窒化ガリウム系半導体素子である。該GaN系多重層は、放熱基板側に備わったAlGaN層及びショットキー電極側に備わったGaN層を含むことができる。かような窒化ガリウム系半導体素子の製造時、ウェーハボンディング(またはメッキ)及びレーザ・リフトオフ工程を利用することができる。

(もっと読む)

半導体装置およびその製造方法

【課題】シリコン以外の半導体で形成される半導体素子で使用可能なTEGを有する半導体装置およびその製造方法を提供する。

【解決手段】SBD部2aと、SBD部2aの電気特性を測定するためのTEG部3aと、を備えた半導体装置1aであって、SBD部2aは、n型のSiCドリフト層8と、SiCドリフト層8上に、SiCドリフト層8の表面9と接触して形成された第1のショットキー電極13と、を有し、TEG部3aは、SiCドリフト層8の表面9を含む箇所に形成されたp型のイオン注入層18aと、SiCドリフト層8上に、SiCドリフト層8の表面9と接触して形成された第2のショットキー電極21aと、第2のショットキー電極21aと電気的に接続され、SiCドリフト層8とは接触しないようにイオン注入層18a上に形成された電極パッド22と、を有する

(もっと読む)

半導体装置の製造方法

【課題】IGBT等においては、ドリフト領域やフィールドストップ領域における少数キャリアのライフタイムを制御して、スイッチング特性を改善するため、ウエハへの電子線照射が行われている。この電子線照射によって、デバイスの閾値電圧がシフトするため、電子線照射後に水素アニールを施すことにより、閾値電圧の回復を図っている。しかし、ボンディングダメージ等を低減するため、デバイス表面のモリブデン系バリアメタルをTiW系バリアメタルに変更すると、水素アニールによる閾値電圧の回復率が低下する問題が発生した。

【解決手段】本願発明はシリコン系半導体ウエハのデバイス主面側にパワー系絶縁ゲート型トランジスタの主要部を形成する半導体装置の製造方法において、デバイス主面上にTiW系のバリアメタルをスパッタリングにより形成するに際して、TiWターゲットのチタン濃度を、8重量%以下で、且つ、2重量%以上とするものである。

(もっと読む)

半導体装置

【課題】低オン抵抗と高破壊耐量との両立が可能な半導体装置を提供する。

【解決手段】実施形態によれば、半導体装置は、第1の主電極と、第1の半導体層と、第1導電形ベース層と、第2導電形ベース層と、第1導電形の第2の半導体層と、第2導電形の埋め込み層と、埋め込み電極と、ゲート絶縁膜と、ゲート電極と、第2の主電極とを備えた。埋め込み層は、第1導電形ベース層中に選択的に設けられた。埋め込み電極は、第2導電形ベース層を貫通して埋め込み層に達するトレンチの底部に設けられ、埋め込み層に接する。ゲート絶縁膜は、埋め込み電極より上のトレンチの側壁に設けられた。ゲート電極は、トレンチ内におけるゲート絶縁膜の内側に設けられた。第2の主電極は、第2の半導体層上に設けられ、第2の半導体層及び埋め込み電極と電気的に接続された。

(もっと読む)

アッド‐オン層形成方法

【課題】多くの半導体装置に必要な低温処理と両立しない高温操作を必要とするような欠点がない、堆積可能なアッド‐オン層形成方法を提供することを目的とする。

【解決手段】堆積可能なアッド‐オン層形成方法であって、第一半導体基板の取り外し層の形成、取り外し層の上の第一半導体基板に多くのドーピング領域の形成、ここで多くのドーピング層の形成は、第一電導型を有するように、ドーピングされ、取り外し層の上の第一半導体基板の第一ドーピング層の形成、第一電導型に対する第二電導型を有するようにドーピングされ、第一ドーピング層の上の第一半導体基板に最低中間ドーピング層の形成、及び中間ドーピング層上の第一半導体基板に最低第三ドーピング層の形成からなり、第三ドーピング層上に第一の電導性ブランケット層の形成、第一電導ブランケット層上に第二の電導性ブランケット層の形成、及び第二電導性ブランケット層が第二半導体基板の対応する電導性上部層と接触するように、第一半導体基板を第二半導体基板への取り付け、からなる。

(もっと読む)

炭化珪素半導体装置およびその製造方法

【課題】トレンチ内のダメージ除去を行う際に、ソース領域とソース電極とのコンタクト抵抗が増大することを抑制できるようにする。

【解決手段】n+型ソース領域4の第2領域4bについて、最表面からある程度の深さの場所については、高不純物濃度とせず、比較的低不純物濃度となるようにする。これにより、ダメージ除去工程を行ったときに、n+型ソース領域4の第2領域4bのうち比較的低不純物濃度とされる部分が若干残るか、もしくは、この部分が消失して第2領域4bのうちの高不純物濃度の部分が増速酸化されても、比較的低不純物濃度とされる部分の酸化に時間が掛かるため、増速酸化される領域が少なくなるようにできる。したがって、n+型ソース領域4の第2領域4bのうちのソース電極9とのコンタクト部が消失することを防止でき、n+型ソース領域4とソース電極9とのコンタクト抵抗の増大を抑制することが可能となる。

(もっと読む)

半導体整流装置

【課題】十分なサージ電流耐性を有し、かつ、信頼性の向上するワイドバンドギャップ半導体を用いた半導体整流装置を提供する。

【解決手段】第1導電型の第1のワイドバンドギャップ半導体領域16と、第1の半導体領域に挟まれて形成される第2導電型の第2のワイドバンドギャップ半導体領域18とを備えている。また、少なくとも一部が第2の半導体領域に接続され、第1の半導体領域に挟まれて形成され、第2の半導体領域より幅の狭い、複数の第2導電型の第3のワイドバンドギャップ半導体領域32を備えている。ここで、第3の半導体領域の長手方向を第1導電型の半導体層の表面に投影した方向が、第1導電型の半導体層の表面から裏面に向かう方向に対し、90±30度の角度を有している。また、第3の半導体領域の間隔が、第1導電型のワイドバンドギャップ半導体層の厚さをdとする場合に2d×tan18°以上である。

(もっと読む)

半導体装置

【課題】電界効果型トランジスタ部のオン抵抗を下げ、かつショットキーバリアダイオード部のリーク電流を抑制する。

【解決手段】半導体装置は、第1の半導体層と、第2の半導体層と、第3の半導体層と、第3の半導体層の表面から、第2の半導体層を貫通し、第1の半導体層に至る第1のトレンチ内に、第1の絶縁膜を介して設けられた埋め込み電極と、埋め込み電極の上に、第2の絶縁膜を介して設けられた制御電極と、第3の半導体層の表面から、第2の半導体層を貫通し、第1の半導体層に至る第2のトレンチの下端に接続され、第1の半導体層内に選択的に設けられた第4の半導体層と、第1の半導体層に接続された第1の主電極と、第2のトレンチ内に設けられた第2の主電極と、を備える。第2のトレンチの側壁において、第2の主電極と、第1の半導体層と、によるショットキー接合が形成されている。

(もっと読む)

半導体装置

【課題】信頼性を向上させることができる半導体装置を得る。

【解決手段】半導体素子10のエミッタ電極12の一部の領域上に多層メタル20が形成されている。多層メタル20に外部電極22が半田24を介して接続されている。半導体素子10はモールド樹脂36に覆われている。多層メタル20の終端部の直下に第1のセル38aが存在し、多層メタル20の終端部の直下以外に第2のセル38bが存在する。第2のセル38bにはIGBTが形成され、第1のセル38aにはIGBTが形成されていない。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】容量増加による高周波特性の劣化及び裏面電極に起因する絶縁破壊を抑止し、チップ面積を増加させることなく、インパクトイオン化により生成したホールを容易且つ確実に引き抜いて排出することを可能として、高耐圧性及び高信頼性を実現する化合物半導体装置及びその製造方法を提供する。

【解決手段】絶縁性又は半絶縁性の基板1の表面に電子走行層3、電子供給層4が形成され、電子供給層4内には局所的なp型領域7が形成されており、基板1の裏面にp型領域7の一部を露出させる開口1aが形成され、開口1aを導電材料で埋め込みp型領域7とオーミック接続された裏面電極8を備え、AlGaN/GaN・HEMTが構成される。

(もっと読む)

半導体装置およびその制御方法

【課題】リカバリ損失の低減が図れ、かつ、ノイズによるセルフターンオンが生じ難い構造の半導体装置を提供する。

【解決手段】ゲート電極8を深さの異なる第1、第2ゲート電極8a、8bを備えたダブルゲート構造とする。このような構造では、第1、第2ゲート電極8a、8bのうちの第1ゲート電極8aのみをオンさせることで、p型ベース領域3に対して反転層を形成しながらも、その反転層がn-型ドリフト層2とn+型不純物領域4とを繋ぐ深さまでは形成されないようにすることができる。この第1ゲート電極8aを過剰キャリア注入抑制ゲートとして機能させる。

(もっと読む)

121 - 140 / 675

[ Back to top ]