Fターム[4M104HH08]の内容

Fターム[4M104HH08]に分類される特許

81 - 100 / 419

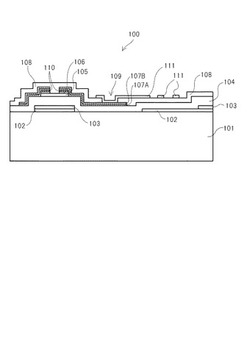

表示装置及び表示装置の製造方法

【課題】表示装置の薄膜トランジスタ基板において、水素プラズマ処理時の水素による影響を低減する。

【解決手段】非晶質ケイ素の膜により形成された非晶質ケイ素層上に形成される銅配線において、第1添加元素として水素化物の生成エネルギーが負の元素、さらに第2添加元素を含む銅を主成分とする合金により形成された銅合金層107Aと、前記銅合金層の上に純銅により形成された純銅層107Bとを有する薄膜トランジスタ基板を備える。

(もっと読む)

半導体発光素子および半導体発光素子の製造方法

【課題】2つの電極の構造を共通にして構成の簡易化を図るとともに、各電極の接合性を向上させつつ、半導体発光素子の電気的特性の低下を抑制する。

【解決手段】半導体発光素子1は、n型半導体層140、発光層150、p型半導体層160、透明電極170、透明電極170に形成されるp側電極300、n型半導体層140に形成されるn側電極400を備える。p側電極300は、透明電極170に積層されるp側接合層310およびp側ボンディングパッド電極320を備え、n側電極400は、n型半導体層140に積層されるn側接合層410およびn側ボンディングパッド電極420を備える。p側接合層310およびn側接合層410はTaNとPtとの混在層で構成され、p側ボンディングパッド電極320およびn側ボンディングパッド電極420はPtとAuとの積層構造で構成される。

(もっと読む)

炭化珪素半導体装置の製造方法

【課題】カーボン膜の除去が必要とならず、かつ、十分にコンタクト抵抗を低抵抗化できるようにする。

【解決手段】オーミック電極5を形成するための金属層15の形成前にレーザ光の吸収効果の高いカーボン層14を形成しておき、その上に金属層15を形成してからレーザアニールを行うようにしている。これにより、金属層15を構成する金属がカーボン層14を構成する炭素(C)やn+型基板1を構成するシリコン(Si)または炭素と反応してオーミック電極5が形成されるため、カーボン層14を除去する必要がない。また、レーザアニール時にカーボン層14を用いているため、レーザ光の吸収率を高くすることができ、オーミック電極5のコンタクト抵抗の低抵抗化を十分に行うことが可能となる。したがって、カーボン膜14の除去が必要とならず、かつ、十分にコンタクト抵抗を低抵抗化することが可能となる。

(もっと読む)

相互接続用自己整合バリアおよびキャッピング層

集積回路に使用する銅線のための集積回路用相互接続構造およびこれを作る方法が提供される。Mn、Cr、またはV含有層が、線からの銅の拡散に対しバリアを形成し、それにより、絶縁体の早期絶縁破壊を防ぎ、銅によるトランジスタの劣化を保護する。また、Mn、Cr、またはV含有層は、銅と絶縁体の間の強い接着を促進し、その結果、製造と使用中のデバイスの機械的健全性を保ち、さらに、デバイスの使用中の銅のエレクトロマイグレーションによる故障を防ぎ、また、環境からの酸素または水による銅の腐食を防ぐ。このような集積回路の形成に関しては、本発明の特定の実施形態により、Mn、Cr、V、またはCoを銅表面上に選択的に堆積させ、一方で、絶縁体表面上のMn、Cr、V、またはCoの堆積を減らす、または防ぎさえもする方法が提供される。また、Mn、Cr、またはV含有前駆物質およびヨウ素または臭素含有前駆物質を使った銅の触媒堆積も提供される。 (もっと読む)

金属酸化膜の形成方法および金属酸化膜

【課題】所定パターンを有するとともに、表面抵抗率や光透過率等のばらつきが少ない金属酸化膜の形成方法およびそのような金属酸化膜を提供する。

【解決手段】基材上に、所定パターンを有する金属酸化膜の形成方法等であって、基材に対して、金属塩を含有する液状物を塗布して金属塩膜を形成する第1工程と、金属塩膜に対して、所定パターンを設ける第2工程と、金属塩膜に対して、熱酸化処理または所定のプラズマ酸化処理を行い、金属酸化膜とする第3工程と、を含む。

(もっと読む)

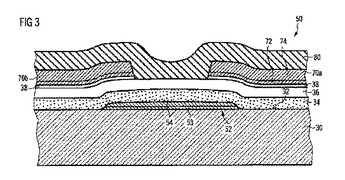

半導体デバイスを製造する方法および設備と半導体デバイス

半導体デバイスを生産する方法が提供され、この半導体デバイス(50)は、基板(30)と、半導体層(36、38)と、基板および半導体層から選択された少なくとも1つの要素に隣接する少なくとも1つのメタライゼーション層(52、70)とを含み、この方法は、基板および半導体層から選択された少なくとも1つの要素の近くに酸素を含む少なくとも1つのメタライゼーション層を形成するステップを含む。  (もっと読む)

(もっと読む)

配線構造およびそれを備えた表示装置

【課題】銅配線層の接着性を改善するとともに、銅配線層の抵抗値が大きくなることを抑制する配線構造を提供する。

【解決手段】配線構造10では、ガラス基板11上に、チタンからなる接着層12と、酸化銅からなるバリア層13と、純銅からなる銅配線層14とが順に積層されている。接着層12は、銅配線層14をガラス基板11に確実に接着させて、銅配線層14がガラス基板11から剥がれるのを防止する。バリア層13は、配線構造10を熱処理したときに、接着層12を構成するチタン原子が銅配線層14内に拡散しないようにして、銅配線層14の抵抗値が大きくならないようにする。このため、銅配線層14は、熱処理された後も、比抵抗を小さな値に保つことができるので、信号の遅延を防止できる。

(もっと読む)

半導体装置

【課題】半導体基板に縦型パワートランジスタが形成され、該半導体基板の主面側と裏面側にそれぞれ電極が形成されてなる半導体装置であって、半導体基板の主面側と裏面側とで残留応力が低くバランスされており、半田接合に際して剥がれや亀裂等の不具合が生じ難い電極構造を有してなる半導体装置を提供する。

【解決手段】主面側の半導体基板1上に保護膜5が形成され、第1下地電極層14に接続する第1金属電極30aが保護膜5に設けられた開口部5kを介して外部に露出すると共に、裏面側の半導体基板1上の全面に第2下地電極層14bに接続する第2金属電極30bが形成され、第1金属電極30aと第2金属電極30bが、半導体基板1側から外部側に向かって、スパッタにより形成された同じ層数で対応する各層が同じ材料からなる積層構造を有してなる半導体装置100とする。

(もっと読む)

成膜方法および記憶媒体

【課題】Coをメッキシードとして電解メッキによるCu膜を成膜する場合に、Coの溶出を抑制してCoシード上に均質でかつ密着性の高いCu膜を形成することができる成膜方法を提供すること。

【解決手段】表面にシード層としてCo膜が形成された基板を準備し、Co膜の上に硫酸銅溶液を主体とするメッキ液を用いて、電解メッキにより基板のCo膜上にCu膜を成膜するにあたり、基板表面をメッキ液に浸漬する前に、基板に対して、Coの表面電位がCoの酸化電位より低くなるような負の電圧を印加する。

(もっと読む)

半導体装置およびその製造方法

【課題】炭化珪素(SiC)半導体装置において、SiC基板との良好なオーミック特性が得られると共に、密着性および耐久性に優れた裏面電極を提供する。

【解決手段】SiC半導体装置は、SiC基板1の裏面に形成されたニッケル膜3を含む裏面電極11と、SiC基板1とニッケル膜3との間に介在し、開口部2aを有するバリア膜2とを備える。SiC基板1とニッケル膜3との間においては、バリア膜2の開口部2aの部分に、ニッケルシリサイドの反応層4が形成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】従来の半導体装置では、基板裏面側のプラズマ処理により、基板表面側の電極が変色し、SiN膜がプラズマ処理されてしまう問題があった。

【解決手段】本発明の半導体装置では、シリコン基板2の裏面側に裏面電極13を配置し、その裏面電極13を構成するAl層14は、シリコン基板2上に直接配置される。そして、Al層14は、シリコン基板2とAlスパイクを形成することで、シリコン基板2と裏面電極13との接着性が向上される。この構造により、シリコン基板2へのプラズマ処理が不要となり、シリコン基板2の表面側のパッド電極12が変色し、ジャケット膜10がプラズマ処理されることを防止できる。

(もっと読む)

配線構造およびその製造方法、並びに配線構造を備えた表示装置

【課題】有機ELディスプレイや液晶ディスプレイなどの表示装置において、半導体層と例えばソース電極やドレイン電極を構成するAl系膜とを安定して直接接続させることが可能であるとともに、ウェットプロセスで用いる電解質液中で、半導体層とAl系膜との間でガルバニック腐食が生じにくく、Al系膜の剥離を抑制することのできる配線構造を提供する。

【解決手段】基板1の上に、基板1側から順に、薄膜トランジスタの半導体層4と、半導体層4と直接接続するAl合金膜6と、を備えた配線構造であって、半導体層4は酸化物半導体からなり、Al合金膜6は、Niおよび/またはCoを含む。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体装置において、Au配線との密着性が強く、より高い熱的安定性を有するバリアメタル層を実現し、更なる特性向上、歩留まり向上を実現する。

【解決手段】半導体装置を、Al層8を含む電極9,10と、Au配線12と、Al層8とAu配線12との間に設けられ、Al層8の側から順に第1Ta層14、第1TaN層15、第1Pt層16を積層した構造を有するバリアメタル層11とを備えるものとする。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、ウエハが反るのを防止できる半導体装置及びその製造方法を提供することを目的とする。

【解決手段】本発明に係る半導体装置は、互いに対向する第1及び第2の主面を有するGaAs基板と、前記GaAs基板の前記第1の主面上に形成され、Pd、Ta、Moの少なくとも1つから構成された第1の金属層と、前記第1の金属層上に形成され、Ni系合金又はNiから構成された第2の金属層と、を備えることを特徴とする。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】製造コストの増加を抑制しつつ、SiC基板の一方面に直接接合されるメタル層の接続信頼性を向上でき、さらにはSiC基板に対するメタル層のオーミック接合を確保することのできる半導体装置およびその製造方法を提供すること。

【解決手段】SiC基板2を有する半導体装置1において、SiC基板2の裏面22側の表層部分に、表面21側の表層部分よりもカーボンが高濃度に含まれる高カーボン濃度SiC層3を形成する。そして、その高カーボン濃度SiC層3の表面にドレイン電極17を直接接合する。

(もっと読む)

半導体素子及びその製造方法、並びに半導体装置

【課題】高温動作の際の相互拡散によるSiC基板と金属シリサイド層との間及び金属シリサイド層とボンディングメタル層との間の接着強度の低下を防止し、高温下での連続動作性及び電気的特性に優れた信頼性の高い半導体素子の製造方法を提供する。

【解決手段】本発明は、ニッケル及びチタンからなる群より選択される少なくとも1つの金属を含む第1の金属層を炭化ケイ素基板の表面に形成する工程と、鉄を含む第2の金属層を前記第1の金属層の表面に形成する工程と、前記第1及び第2の金属層が形成された炭化ケイ素基板を熱処理する工程と、熱処理された前記第2の金属層を除去する工程と

を含むことを特徴とする半導体素子の製造方法である。

(もっと読む)

リフトオフ法を用いたパターン形成方法

【課題】本発明は、リフトオフ法を用いたパターン形成方法を実施したとしても、導電性パターンのエッジ付近にバリが発生することがない、リフトオフ法を用いたパターン形成方法を提供する。

【解決手段】本発明では、まず、導電性パターン6のエッジ部が位置するウエハ基板1の表面内に、溝2を形成する。次に、溝2が露出する開口部3aを有するレジスト3を、ウエハ基板1上に形成する。次に、開口部3aから露出するウエハ基板1上とレジスト3上とに、導電性膜5を形成する。そして、レジスト3を除去することにより、ウエハ基板1上に導電性パターン6を形成する。

(もっと読む)

電極材料、電極及び素子

【課題】導電性、耐熱性、耐硫化性又は耐セレン化性に優れた電極材料、あるいは、製造工程のいずれかの段階において硫化雰囲気又はセレン化雰囲気に曝される素子の電極として用いることが可能な電極材料、このような電極材料を用いた電極、及び、このような電極材料を用いた素子を提供すること。

【解決手段】少なくともSiを含有し、Moを70at%以上含む電極材料、このような電極材料を用いた電極、及び、このような電極材料を電極に用いた素子。Si含有量は、10at%以下が好ましい。

(もっと読む)

電子素子及び電子素子の製造方法

【課題】簡易な構成でリーク電流の抑制された電子素子及びその製造方法を提供する。

【解決手段】基板上に設けられ、Mo−Nb合金から構成された第1の電極と、前記第1の電極上に配置された絶縁膜と、前記第1の電極に対して少なくとも前記絶縁膜を介して配置された第2の電極と、を備えた電子素子とする。

(もっと読む)

不揮発性記憶装置

【課題】第1の配線と第2の配線との交差部に整流素子と不揮発性記憶素子を有する不揮発性記憶装置で、従来に比して高さを抑えることができる不揮発性記憶装置を提供する。

【解決手段】第1の方向に延在するビット線BLと、ビット線BLとは異なる高さに形成され、第2の方向に延在するワード線WLと、ビット線BLとワード線WLとが交差する位置にビット線BLとワード線WLの間に挟持されるように配置される抵抗変化型メモリセルと、を備え、抵抗変化型メモリセルは、抵抗変化素子20がN型半導体層10とP型半導体層30で挟まれた構造を有する。

(もっと読む)

81 - 100 / 419

[ Back to top ]