Fターム[5B046BA04]の内容

CAD (21,103) | 設計対象(段階、工程) (4,232) | 実装設計、レイアウト設計 (2,049)

Fターム[5B046BA04]の下位に属するFターム

割付、配置、ネスティング (289)

ルート探索、配線 (682)

Fターム[5B046BA04]に分類される特許

161 - 180 / 1,078

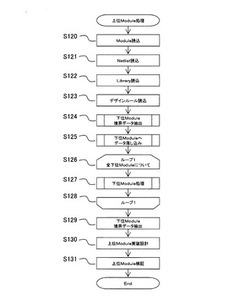

レイアウト設計装置、レイアウト設計方法、及びレイアウト設計プログラム

【課題】

複数階層を有する半導体集積回路の階層レイアウトを行なう際に、複数個所で使用される下位モジュールについての各配置箇所における下位モジュール近傍の上位階層の配線状況を考慮して、下位モジュールのレイアウト設計を行なうことを課題とする。

【解決手段】

上記課題を解決するために、本発明に係るレイアウト設計装置は、複数階層を有する半導体集積回路のレイアウト設計装置であって、複数個所で使用される下位モジュールについて、前記下位モジュールが配置される上位モジュール内のそれぞれの配置箇所近傍の上位階層の配線情報を抽出し、抽出した上位階層の配線情報を、前記下位モジュールのレイアウト設計を行なう際の配線禁止領域として設定し、前記下位モジュールのレイアウトを行なう。

(もっと読む)

モデル生成装置、生成方法、プログラムおよびシミュレーションシステム

【課題】電子部品を解析するためのシミュレーションでの解析精度の低下を抑制しつつ、解析に必要なメモリ量と解析時間を低減できるシミュレーションモデルを生成するための技術を提供する。

【解決手段】本発明のモデル生成装置は、シミュレーションの解析領域に含まれる各物質の比率を解析対象の電子部品のレイアウト情報に基づいて算出し、算出した比率に基づいてその解析領域に含まれる各物質の物性値を合成した合成値を算出し、その解析領域がその合成値を物性値とする一種類の物質からなるものとしてシミュレーションモデルを生成する。

(もっと読む)

レイアウト作成支援システム、レイアウト作成支援方法及びレイアウト作成支援プログラム

【課題】動線の混雑状況から効率のよい区画案を把握するためのレイアウト作成支援システム、レイアウト作成支援方法及びレイアウト作成支援プログラムを提供する。

【解決手段】レイアウト作成支援システム20の制御部21は、郵便物移動関係レコードから郵便物の移動作業における移動元のエリア及び移動先のエリアを特定し、エリア間の移動距離を算出する。制御部21は、取扱量から各移動作業の搬送回数を算出する。制御部21は、各エリア間の移動距離と搬送回数とを乗算して移動作業別の総移動距離を算出する。制御部21は、移動作業別の総移動距離をすべて加算することにより、全体総移動距離を算出する。制御部21は、移動元のエリアと移動先のエリアとを結ぶ動線を、搬送回数に応じた幅で、区画案表示領域の配置図上に表示する。

(もっと読む)

ガードリング設計装置、ガードリング設計方法、プログラム及び記録媒体

【課題】半導体集積回路の素子及び配線のレイアウトにおけるガードリングの設計の自由度を高める。

【解決手段】設計装置は、デザインルールを記憶するデザインルール記憶部11、予め設計されたレイアウトを記憶するレイアウト記憶部12、デザインルールに適合したガードリング幅を設定幅として設定するガードリング幅設定部21、レイアウト上にガードリングの形成経路を指定するための経路指定部32、指定経路に基づいてガードリング形成経路を認識する経路認識部22、ガードリング形成用のレイヤーリストを記憶するガードリング形成用レイヤー記憶部13、認識経路の下地レイヤーに応じたガードリング形成用のレイヤーを設定するガードリング形成用レイヤー設定部23及び認識経路に設定幅で設定レイヤーを反映させてガードリングを生成するガードリング生成部24を備えている。

(もっと読む)

回路設計支援装置およびプログラム

【課題】 制約条件が設定された回路図の設計において,回路図を編集した場合に,関連する制約条件を更新する装置を提供する。

【解決手段】 回路設計支援装置10は,回路図毎に,回路の要素,要素の接続,制約条件へのリンクを含む回路データを記憶する回路データ記憶部3,回路図毎に,設計上の制約条件を示す制約条件データを記憶する制約条件データ記憶部4,ユーザ操作をもとに回路データを入力・編集して,編集対象となった要素を保持する回路編集制御部11,ユーザ操作をもとに制約条件データを入力・編集する制約条件編集制御部12,回路データが編集された場合に,編集対象の要素に設定された制約条件データの内容を,制約の種別,設定された要素の種別をもとに更新する制約条件更新部13,回路データ等を表示する表示部14および出力する回路データ等を生成する出力データ生成部15を備える。

(もっと読む)

実装設計支援装置、実装設計支援方法及びプログラム

【課題】電子部品間の配線距離を視覚的に把握することで、電子部品の最適な配置を支援することができる実装設計支援装置、実装設計支援方法及びプログラムを提供する。

【解決手段】画面表示された複数の電子部品101〜105の中の一の電子部品101と、電子部品101に接続すべき電子部品102,103,104それぞれとの配線距離を算出する。算出した配線距離、及び、電子部品101に対応する制約条件に基づいて表示色を決定し、決定した表示色で、ラッツネストL1,L2,L3それぞれを表示する。

(もっと読む)

分電盤の設計方法

【課題】 ボックス内における機器ユニットの組み合わせ自由度を高め、スペースと部品の無駄を少なくし、分電盤を簡易に設計できる方法を提供する。

【解決手段】 ブレーカに関連部品を組み合わせた機器ユニットの縦寸法をボックスに内蔵したレールやパネル等の取付穴ピッチを基準寸法として規格化し、電気回路仕様が異なる複数の機器ユニットの寸法情報をデータベース34に登録する。機器ユニットの寸法情報には、ブレーカのハンドルを露出させる開口部の位置と大きさを配線覆い上に定義するための寸法情報も含まれている。コンピュータ31は、入力された分電盤の電気回路仕様を解釈し、今回使用する機器がユニット対応機器である場合に、電源およびブレーカの種類に適合する寸法の機器ユニットをデータベース34から選出し、この寸法情報に基づいて、ボックスおよび配線覆いの寸法を求める。

(もっと読む)

プロセスシミュレーションをコンピュータに実行させるプログラム

【課題】短い計算時間で不純物分布精度の高いプロセスシミュレーションを行う。

【解決手段】元々の計算では考慮されていたが、計算時間を削減するための領域限定により計算領域から除外された隣接領域と同一材質の仮想膜を界面に付加して不純物拡散の計算を実行し、計算結果から元の構造の不純物濃度を更新し、後続のプロセスに移る際に仮想膜のデータを破棄する。

(もっと読む)

フロアプランデータ生成装置及び方法

【課題】チップの設計期間を短縮する。

【解決手段】CPU1は、設計対象の回路を構成するセルのうち、所定のサイズより大きいセルサイズを有するセルのみの回路情報をゲートレベルで記述した簡易ネットリスト43と、所定のサイズより大きいセルサイズを有するセルのみの仕様データを含むセルリスト44とを用いてフロアプランを行い、仮フロアプランデータ47を生成する。CPU1は、ユーザによって回路全体のフロアプランが行われるときに、回路を構成するセルの仕様データである全体ライブラリ42と、回路を構成するセルの回路情報をゲートレベルで記述した全体ネットリスト45と、仮フロアプランデータ47と、簡易ネットリスト43を全体ネットリスト45に整合させるためのセルリスト44とを出力する。

(もっと読む)

電磁界解析用データ生成装置、電磁界解析用データ生成方法

【課題】AV機器等の3次元CADデータを用いて電磁界解析用データを作成する際に、解析精度を落とすことなく、データ量を減らし解析時間を短縮することができる電磁界解析用データ生成装置および生成方法を提供すること。

【解決手段】電磁界解析用データを生成する際に、3次元CAD抽出手段で部材を抽出後、電磁界解析に必要な導体部材のみを選択する。そして、選択された部材に設定された導通確保エリア情報に基づき導通確保エリアと最も近接した部材との間に導通を確保する追加導体を生成する。

(もっと読む)

設計支援方法

【課題】開発期間の短縮を図ること。

【解決手段】設計支援装置は、実回路レイアウト25から認識したデバイスのレイアウトデータについて、そのデバイスを含む所定領域内の着目パターンのエッジを格子分割し、各格子に含まれるエッジの有効無効を判定する。次に、設計支援装置は、判定結果に応じて着目パターンに対する形状情報を含む格子テーブルを生成する。そして、設計支援装置は、評価レイアウト22に基づいてエッジ位置に対するデバイスの特性変動に対応する重み付け情報を格子位置に関連付けた形状依存テーブル24と、格子テーブルとに基づいてデバイスの形状に応じた特性変動量を算出する。

(もっと読む)

ワイヤハーネス導通検査方法およびワイヤハーネス導通検査プログラム

【課題】正否判定工程に要する時間を短縮することができるワイヤハーネス導通検査方法およびワイヤハーネス導通検査プログラムを提供すること。

【解決手段】第1の分割領域Aに必要とみなされる第1の仕様と、第2の分割領域Bに必要とみなされる第2の仕様と、を比較し、共通する仕様の有無を判別し、共通する仕様が少なくとも一つある場合、第1の分割領域Aに配索可能な第1のワイヤハーネスのいずれか一つと、第2の分割領域Bに配索可能な第2のワイヤハーネスのいずれか一つと、について記述された部位毎コネクタ・配線情報を、該第1のワイヤハーネスと該第2のワイヤハーネスの組合せだけ作成する。

(もっと読む)

半導体集積回路及びそのタイミング調整方法

【課題】従来技術の半導体集積回路では、タイミング調整に工数がかかるという問題があった。

【解決手段】本発明にかかる半導体集積回路は、外部メモリと接続される複数の信号線に対応して個別に設けられ前記対応する信号線のタイミングを決定する回路ブロックをマクロ化した論理セル群11〜15と、論理セル群11〜15のそれぞれに対応して設けられたIOバッファ21〜26と、を有する。そして、論理セル群11〜15と対応するIOバッファ21〜26とを結合する配線のそれぞれが略同じ長さを有することを特徴とする。

(もっと読む)

クロックツリー形成システム、クロックツリー形成方法及びプログラム

【課題】タイミング収束のイタレーションを削減する。

【解決手段】半導体集積回路600のクロックツリー700Aが、分周器752が追加されたクロックツリー700Bで置換されない場合について、モジュール761及び762に関するホールドエラー値HEV1を算出する(S105)。クロックツリー700Aがクロックツリー700Bで置換された場合について、モジュール761及び762に関するホールドエラー値HEV2を算出する(S107)。ホールドエラー値HEV1及びHEV2に基づいて、クロックツリー700Aをクロックツリー700Bで置換することで半導体集積回路600のホールドエラーが削減されるか判定する(S108)。半導体集積回路600のホールドエラーが削減されると判定された場合、クロックツリー700Aがクロックツリー700Bで置換された半導体集積回路600を記述する回路データを生成する(S109)。

(もっと読む)

プリント配線板設計製造支援システム及び方法

【課題】プリント配線板の設計作業を簡略化して、低コストかつ短時間で所望のプリント配線板を得ることを課題とする。

【解決手段】予め既製化されて用意された複数種のプリント配線板モジュールがライブラリーとしてデータベース4に保存登録され、データベース4に登録保存されたプリント配線板モジュールは顧客1に提示され、顧客1は提示された複数種のプリント配線板モジュールの中から1または複数のプリント配線板モジュールを選択し、選択した複数のプリント配線板モジュールを組み合わせて1つのプリント配線板を設計構成し、設計構成されたプリント配線板の設計データは、顧客1から事業者2に送付され、送付された設計データに基づいてプリント配線板を製造する際のマスクフィルムが作画され、作画されたマスクフィルムに基づいてプリント配線板製造工場3でプリント配線板が製造されることを特徴とする。

(もっと読む)

モデルベースの性能予測システム

【課題】組み込みシステムの開発において、設計の上流段階でリアルタイム性など時間的要素を検証することを可能とする。

【解決手段】機能と遅延とを少なくとも属性として持つ要素演算ブロックの集合である基本ブロックデータベースを備え、上記基本ブロックのデータベースを用いて開発したモデルを記憶する設計モデル記憶部と、一つ以上の基本ブロックの組み合わせからなる上記モデルに含まれる全てのタスクについての、基本ブロックの組み合わせ構成や実行優先度などが定義されたタスク定義記憶部と、CPU、ROM/RAMなど実装リソースの情報を記憶するリソース情報記憶部と、一部または全てのタスクのデッドラインを記憶するデッドライン記憶部を備える。

(もっと読む)

設計支援システム

【課題】設計者のスキルに応じて動作環境を切り替えることができる設計支援システムを提供する。

【解決手段】設計者各々の設計スキルに関する条件情報を記憶する個人データ記憶手段と、条件情報を入力し、個人データ記憶手段に記憶する個人データ入力手段と、設計スキルのランクに応じた設計支援システムのプログラムを記憶するプログラムデータ記憶手段と、設計支援システムのプログラムの使用者の認証時に、個人データ記憶手段に記憶されている使用者の条件情報から該使用者の設計スキルのランクを決定するランク決定手段と、ランク決定手段により決定された設計スキルのランクに応じた設計支援システムのプログラムをプログラムデータ記憶手段から読み出して、該プログラムを実行するアプリケーションサーバにロードして、設計者のクライアント端末において該プログラムを使用して設計業務が行える状態にするプログラム管理手段とを備えた。

(もっと読む)

ファシリティマネージメント支援装置および方法

【課題】通常ドキュメント化されない什器等の物品の所在に到るまで現状に忠実な情報に基づくレイアウトの検討が可能であり、且つ、平生は壁面内部等に隠蔽されている、配管、バルブ、端子ボックス等のようなレイアウト変更に際して考慮されるべき重要なファクタを見逃さずに考慮することが出来るファシリティマネージメント支援装置および方法を提供する。

【解決手段】ファシリティマネージメントの対象とされる室内各部の現状を撮影して取得した現状画像データ(141)と、現状では隠蔽されている部位が未だ露呈していた施工段階での当該室内各部を予め撮影して取得した施工段階画像データ(142)とに基づいて、現状画像データによる室内各部の現状の画像を透過するように施工段階画像データによる施工段階画像が目視される透視画像を表す透視画像データを合成して出力する。

(もっと読む)

集積回路における相互接続レイアウトのための方法および装置

実施形態は、集積回路(IC)を設計する方法(たとえば、コンピュータで実現される方法)に関する。この実施形態において、基板(402)上の集積回路の導電層(404−1,404−2,404−3,404−4,404−5)を記述するレイアウトデータ(400)が、集積回路のための設計仕様データに従って生成される。導電層は、ボンディングパッド(406)の最上層を含む。レイアウトデータにおける金属構造体(408)が変更されて、各々のボンディングパッド(406)の下の閾値体積内の導電層(404−1,404−2,404−3,404−4,404−5)の重畳した平面内における金属密度を最大化する。レイアウトデータ(400)の記述は、集積回路を製造するための1以上のマスクに生成される。重畳した平面内における金属密度を最大化することにより、相互接続体における誘電性材料(412)を通る縦方向チャネルが減少される、あるいはなくなる。したがって、α粒子が容易に相互接続体を貫通して下部の基板(402)に達することができなくなり、メモリセルにおけるシングルイベントアップセットのようなソフトエラーを減少させる。  (もっと読む)

(もっと読む)

レイアウト設計支援装置および方法

【課題】レイアウト設計において広く不特定多数の顧客(顧客となる蓋然性のある人物)からレイアウトの選択に関する情報を収集し、この情報をレイアウト設計に資することが出来るようにしたレイアウト設計支援装置および方法を提供する。

【解決手段】インターネット上のサーバコンピュータ100が保有するバーチャルリアリティデータによるバーチャルリアリティ空間(バーチャル室内)に対する操作状況を把握できるようにシステムを構築し、広く、不特定多数の顧客(将来の顧客候補者)からのレイアウト変更に関するニーズとこの変更操作を行ったユーザの属性に関するデータとを得て(レイアウト変更データ収集部131、変更主体データ収集部32)、これらのデータを分析してユーザニーズの傾向を把握する(ユーザニーズデータ構築部133)。

(もっと読む)

161 - 180 / 1,078

[ Back to top ]