Fターム[5C094DB04]の内容

要素組合せによる可変情報用表示装置 (81,180) | 電気的接続 (3,264) | 素子同士の接続 (1,011)

Fターム[5C094DB04]に分類される特許

61 - 80 / 1,011

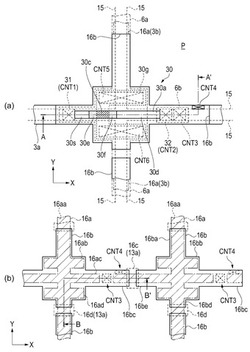

電気光学装置および電子機器

【課題】画素が高精細になっても所望の電気容量を有する保持容量を実現可能な電気光学装置およびこれを備えた電子機器を提供すること。

【解決手段】本適用例の電気光学装置は、データ線6a及び走査線3aと、データ線6aと走査線3aとの交差に対応して設けられたトランジスター30と、トランジスター30に電気的に接続され、第1容量電極16aと第2容量電極16bとが誘電体層を介して対向配置される保持容量と、を備え、第1容量電極16aは、第1導電膜と第1導電膜の上面及び側面を覆う第2導電膜とを有し、第2容量電極16bは、第1容量電極16aの上面及び側面において誘電体層を介して第1容量電極16aと対向して保持容量を形成している。

(もっと読む)

トランジスタ、その製造方法および表示装置

【課題】ソース電極およびドレイン電極からのオーミックコンタクト膜の延在部分の表面を介したリーク電流、およびオーミックコンタクト膜と半導体能動膜との接合側面部での欠陥を介したリーク電流を増大させないことが可能な薄膜トランジスタを提供することにある。

【解決手段】オーソミックコンタクト層8の一方は、電極9,10の一方に接触して覆われた接触部分81と、接触部分81よりも厚さ方向D2において薄く、厚さ方向D2から見て電極9,10の一方からはみ出して電極9,10の他方へと延在して半導体能動膜7の少なくとも一部71を避けて覆う延在部分82とを有する。

(もっと読む)

液晶表示装置の製造方法及び液晶表示装置

【課題】層数を低減し、製造コストを抑え、かつ点灯異常を抑制して製造歩留まりの向上を図ることのできる液晶表示装置の製造方法を提供する。

【解決手段】画素部(a)と周辺部(c)とを有する基板を用いた液晶表示装置の製造方法において、ゲート絶縁膜3上に半導体層4と画素電極5を形成した後、基板上に導電膜を平面ベタに形成し、ホトレジストパターンをマスクとして、画素部(a)の半導体層4と画素電極5とを電気的に接続するドレイン電極を形成すると共に、画素部(a)と周辺部(c)における半導体層4を露出させ、周辺部の半導体層4をエッチング量の指標として用いて画素領域(a)の半導体層4をエッチングする。

(もっと読む)

電気光学装置の制御方法、電気光学装置の制御装置、電気光学装置、及び電子機器

【課題】例えばマトリクス駆動方式の電気光学装置において、消費電力を低減する。

【解決手段】電気光学装置の制御方法は、第1の選択期間において低電位(VL)が供給されるとともに第2の選択期間において高電位(VH)が供給されるデータ線の数と、第1の選択期間において高電位が供給されるとともに第2の選択期間において低電位が供給されるデータ線の数との和である第1の和(N2V)が、第1の選択期間において低電位が供給されるとともに第2の選択期間において低電位が供給されるデータ線の数と、第1の選択期間において高電位が供給されるとともに第2の選択期間において高電位が供給されるデータ線の数との和である第2の和(N0)よりも大きい場合には、第1の選択期間と第2の選択期間との間の期間において、複数のデータ線の全てに基準電位(GND)が供給されるように、駆動部を制御する。

(もっと読む)

電気光学装置、投射型表示装置、および電子機器

【課題】蓄積容量の形成領域を広げても、表示光の出射光量の低下や画素電極の端部付近での電位分布の乱れが発生しにくい電気光学装置、投射型表示装置、および電子機器を提供すること。

【解決手段】液晶装置100において各画素では、透光の誘電体層40に対して基板本体10wが位置する側に第1電極層7が設けられ、誘電体層40に対して画素電極9aが位置する側に透光性の第2電極層8aが設けられている。このため、透光性の第1電極層7、透光性の誘電体層40、および透光性の第2電極層8aによって蓄積容量55が構成されている。また、蓄積容量55と画素電極9aとの間に透光性の層間絶縁膜44が設けられている。このため、画素電極9aを研磨により平坦化した平坦面上に形成することができるとともに、共通電位が印加された第1電極層7と画素電極9aの端部との間に余計な電界が発生しない。

(もっと読む)

電気光学装置、電子機器、電気光学装置の製造方法

【課題】所望の保持容量を有すると共に、画素電極の表面における凹凸に起因する表示ムラが低減された電気光学装置、これを備えた電子機器、電気光学装置の製造方法を提供すること。

【解決手段】本適用例の電気光学装置としての液晶装置は、素子基板10上に、トランジスターと、トランジスターに対応して設けられた画素電極15と、素子基板10と画素電極15との間に、画素電極15と一部が対向するように設けられ、画素電極15と誘電体層14を介して保持容量を構成する容量配線3bと、を備え、容量配線3bは、素子基板10と画素電極15との間に設けられた絶縁膜13に埋め込まれるように形成されており、絶縁膜13と共に画素電極15側の面が平坦化されてなる。

(もっと読む)

表示装置および電子機器

【課題】表示画素に有機電界発光素子を用いた場合に、装置全体の厚みを増大させることなくタッチセンサ機能を付加することが可能な表示装置を提供する。

【解決手段】ボトムエミッション方式による有機EL表示装置1は、光取り出し面を有する透明基板11上に、複数の画素電極19Aと、発光層を含む有機層21と、上部電極22と、封止用基板24とをこの順に備える。透明基板11と封止用基板24との間に、透明基板11の側から順に、検出電極12と、この検出電極12との間に容量素子C1を形成するセンサ用駆動電極19Bとを備える。有機層21から発せられた光は透明基板11側から取り出される(透明基板11側に画像が表示される)一方で、その透明基板11の表面に接触または近接する物体の検出がなされる。

(もっと読む)

表示装置および電子機器

【課題】画質劣化を抑制することが可能な表示装置および電子機器を提供する。

【解決手段】有機EL表示装置1Aは、駆動側基板10上に、有機EL素子10Aと、トランジスタ10Bと、映像信号に対応する電荷を保持する保持容量素子10Cとを備えたものである。保持容量素子10Cは、駆動側基板10の側から順に、導電膜27A、酸化物半導体よりなる半導体層11、絶縁膜12Bおよび導電膜13Bを積層してなる。保持容量素子10Cでは、導電膜27A,13B間において容量形成がなされ、印加電圧に依存する容量変動が抑制される。

(もっと読む)

表示装置および電子機器

【課題】表示画質を向上させることが可能な表示装置および電子機器を提供する。

【解決手段】表示装置1は、表示素子(液晶素子LC)を含む複数の画素10と、互いに異なる階調電位を保持する複数種類の電位線(黒電位線LBおよび白電位線LW)と、複数種類の電位線のうちの選択された1種の電位線の階調電位が表示素子に対して供給されるように、映像信号に基づいて各画素10の表示駆動を行う駆動部とを備えている。表示素子への印加電圧または印加電流の変動量に対する表示輝度の変動量に対応する輝度勾配が相対的に急峻である階調電位(例えば黒階調電位)を保持する第1の電位線(例えば黒電位線LB)の抵抗値が、輝度勾配が相対的に緩やかである階調電位(例えば白階調電位)を保持する第2の電位線(例えば白電位線LW)の抵抗値と比べて低くなっている。

(もっと読む)

電気光学装置、投射型表示装置、電子機器、および電気光学装置の製造方法

【課題】コンタクトホールに起因する画素電極の凹凸を緩和することができる電気光学装置、投射型表示装置、電子機器および電気光学装置の製造方法を提供すること。

【解決手段】液晶装置の素子基板において、第2電極層7aと画素電極9aとを導通させるにあたって、コンタクトホール45aの底部45a1を避けて、コンタクトホール45aの側壁45a2およびコンタクトホール45aの外部に第2絶縁膜47を設ける。このため、コンタクトホール45aは、コンタクトホール45aの側壁45a2に設けられている第2絶縁膜47の厚さ分は、平面サイズが小さくなっている。かかる構造は、コンタクトホール45aを形成した後、第2絶縁膜47を形成し、第2絶縁膜47に対して異方性エッチングを行うことにより実現できる。

(もっと読む)

表示装置およびその製造方法

【課題】TFTの特性劣化を抑制しつつクロス容量を低下することが可能な表示装置およびその製造方法を提供する。

【解決手段】基板11上にゲート電極12および第1配線層21を形成したのち、全面にゲート絶縁膜13を形成する。次に、ゲート絶縁膜13上に半導体層14Aを形成したのち、半導体層14A上に第1保護膜15を形成する。第1配線層に対向する領域の半導体層14および第1保護膜15の除去およびその他の領域をエッチングにより加工する。次いで、全面に第2保護膜23を形成および加工したのち、ソース・ドレイン電極17および第2配線層24を形成する。これにより、チャネル層14表面の損傷が防止されると共に、配線部20のクロス容量が低減される。

(もっと読む)

有機エレクトロルミネッセンス素子および表示装置

【課題】光取り出し効率が向上し、もって、高輝度化且つ低消費電力化が実現可能な有機EL素子、およびそれを用いた表示装置を提供することを目的とする。

【解決手段】透明電極であるカソード電極25と、光を透過する金属層である透明金属層243および光を反射する金属層である反射性金属層241で少なくとも構成され、透明金属層243および反射性金属層241が積層された第1領域と、光を透過する絶縁層である透明絶縁層242が透明金属層243および反射性金属層241の間に形成された第2領域とを有するアノード電極24と、カソード電極25およびアノード電極24の間に形成され、カソード電極25を介して出射される光を発光する有機EL層23と、を備え、有機EL層23は、前記第2領域における透明金属層243と接して形成され、反射性金属層241は、前記第2領域において、有機EL層23からの発光を反射する。

(もっと読む)

ルーティングのための高いランド領域を有するMEMSを作製する方法及びそれによって作製されたデバイス

【課題】マスキングを減少させた微小電子機械システム(MEMS)デバイスを製作する方法と、その方法によって形成されたMEMSデバイスを提供する。

【解決手段】アレイ領域と周辺領域とを有する前面基板1000であって、アレイ領域内に複数の下側領域をその間に定める複数の支持体1011a−1011d,1013a−1013cを有し、周辺領域内にランドをさらに有し、ランドの少なくとも一部が、アレイ領域内の支持体と実質的に同じ高さを有する、前面基板と、周辺領域内のランド上に重ねて形成された複数の導体であって、導体が互いに電気的に絶縁される、複数の導体と、前面基板の下側領域上に形成された導電層とを有する。

(もっと読む)

電子装置

【課題】 信頼性及び色再現性の高い電子装置を提供する。

【解決手段】 単結晶半導体基板11上にスイッチング用FET201及び電流制御用FET202を形成し、電流制御用FET202にEL素子203が電気的に接続された画素構造とする。電流制御用FET202は画素間での特性ばらつきが極めて小さく、色再現性の高い画像を得ることができる。電流制御用FET202にホットキャリア対策を施すことで信頼性の高い電子装置が得られる。

(もっと読む)

電気光学装置

【課題】電気光学装置の基板間導通端子の導通不良を原因とする不具合が発生している場合において、導通不良となっている基板間接続端子を効率よく探し出せるようにする。

【解決手段】対向基板12の4隅とTFT基板11との間には基板間導通端子1,2,3,4がある。TFT基板11における基板間導通端子1,2と外部回路接続端子8との間には配線L18及びL28がある。基板間導通端子1及び2間、基板間導通端子1及び3間、基板間導通端子3及び4間、基板間導通端子2及び4間には配線L12,L13,L34,及びL24がある。配線L18と配線L23の間には基板間導通端子1を迂回する配線LDTR1がある。配線L28と配線L24の間には基板間導通端子2を迂回する配線LDTR2がある。

(もっと読む)

電気光学装置および電子機器

【課題】データ線114の電位変動に起因するノイズの影響を受けにくくして、発光素子150に流す電流を制御する。

【解決手段】互いに交差する走査線112およびデータ線114と、これらの交差に対応して設けられた画素回路110と、シールド配線81a、81bとを有する。画素回路110は、発光素子150と、発光素子150に流れる電流を制御するトランジスター140と、トランジスター140のゲートノードgとデータ線114との間で、走査線112に供給される走査信号にしたがって導通状態が制御されるトランジスター130と、を備え、シールド配線81a、81bは、平面視したときにデータ線114とトランジスター140との間に設けられている。

(もっと読む)

トランジスタアレイ、およびその製造方法

【課題】簡略化された構成を有するトランジスタアレイを、簡易的に製造することが可能なトランジスタアレイの製造方法を提供することを主目的とする。

【解決手段】金属基板を用い、上記金属基板上に、絶縁性材料からなり、貫通孔を有する絶縁層を形成する絶縁層形成工程と、上記絶縁層上に、ドレイン電極が上記絶縁層に形成された貫通孔を介して上記金属基板に接続されるように薄膜トランジスタを形成する、薄膜トランジスタ形成工程と、上記金属基板をパターニングすることにより、上記金属基板を画素電極とする画素電極形成工程と、を有することを特徴とする、トランジスタアレイの製造方法を提供することにより、上記課題を解決する。

(もっと読む)

液晶表示装置

【課題】横電界方式で液晶層を駆動する液晶表示装置において、その画像表示性能を向上させる。

【解決手段】画素領域のそれぞれには、ドレイン信号線DLに接続された薄膜トランジスタTFTと、複数のスリットを有し且つ透明導電膜で形成される第1の電極と、前記薄膜トランジスタと前記第1の電極を接続する接続領域を有し、透明導電膜で形成される平面状の第2の電極を有し、前記第2の電極は、前記第1の電極と前記第1の基板間に形成され、且つ、前記第1の電極とゲート信号線GLに重畳し、さらに、隣接する前記画素領域の第2の電極と接続されていることを特徴とする液晶表示装置である。

(もっと読む)

EL表示装置

【課題】動作性能および信頼性の高いEL表示装置を提供する。

【解決手段】第1のチャネル形成領域と、第1のソース領域及び第1のドレイン領域と、ゲート絶縁膜と、第1のゲート電極とを備えた第1のTFTと、第2のチャネル形成領域と、第2のソース領域及び第2のドレイン領域と、ゲート絶縁膜と、第2のゲート電極とを備えた第2のTFTと、第1のTFT及び第2のTFT上に設けられた第1の絶縁膜と、第1のソース領域及び第1のドレイン領域の一方と接続されたソース配線と、第1のソース領域及び第1のドレイン領域の他方と接続し、且つ第2のゲート電極に接続された第1のドレイン配線と、第1の絶縁膜上に設けられ、第2のソース領域及び第2のドレイン領域の一方に接続された第2のドレイン配線と、第1の絶縁膜上に設けられ、第2のソース領域及び第2のドレイン領域の他方に接続された電流供給線と、を有する。

(もっと読む)

発光装置および電子機器

【課題】電源線の抵抗を抑制しながら各要素を電源線と同層から形成する。

【解決手段】基板10の面上には駆動トランジスタTdrと素子導通部71と初期化トランジスタTintと接続部61とが配置される。駆動トランジスタTdrは、電源線15から発光素子Eに供給される電流量を制御する。素子導通部71は、駆動トランジスタTdrと発光素子Eとを電気的に接続する。初期化トランジスタTintは、オン状態に遷移することで駆動トランジスタTdrをダイオード接続する。接続部61は、駆動トランジスタTdrと初期化トランジスタTintとを電気的に接続する。電源線15はX方向に延在する。素子導通部71および接続部61は、電源線15と同層から形成され、基板10に垂直な方向からみて、駆動トランジスタTdrを挟んで電源線15の幅方向(Y方向)における一方の側に位置する。

(もっと読む)

61 - 80 / 1,011

[ Back to top ]