Fターム[5C094DB04]の内容

要素組合せによる可変情報用表示装置 (81,180) | 電気的接続 (3,264) | 素子同士の接続 (1,011)

Fターム[5C094DB04]に分類される特許

41 - 60 / 1,011

表示装置

【課題】信号の遅延が抑制された表示装置を提供する。また、低消費電力駆動が可能な表示装置を提供する。

【解決手段】複数の画素に共通電位を与える共通配線と、画素を駆動する信号を入力するための信号線との間の寄生容量を無くせばよい。具体的には、外部から信号が入力される外部入力端子よりも外側に共通配線を引き回し、信号線と共通配線との交差部を無くすことにより、共通配線と信号線との間の寄生容量がなくなり、表示装置の高速駆動と低消費電力駆動が実現できる。

(もっと読む)

表示装置

【課題】アクティブマトリクス型EL表示装置において、EL材料を成膜する前にTFT

基板の動作の確認をおこない、最終製品の良品率を向上させ、原価を低減すること。

【解決手段】各画素に、駆動用TFTのドレイン領域に電気的に接続し、さらにEL素子

と電気的に並列接続している容量を設け、容量の充放電を確認することによって、駆動用

TFTが正常に動作するかどうかの判断をおこなう。こうして、不良品をEL材料の成膜

前に除去可能であり、製造費用の削減がはかれる。

(もっと読む)

薄膜トランジスタアレイ基板、有機発光表示装置、及び薄膜トランジスタアレイ基板の製造方法

【課題】薄膜トランジスタアレイ基板、有機発光表示装置、及び薄膜トランジスタアレイ基板の製造方法を提供する。

【解決手段】基板10上に配置され、活性層212、ゲート電極214、ソース電極218a、ドレイン電極218b、活性層とゲート電極との間に配置された第1絶縁層13、及びゲート電極とソース電極及びドレイン電極との間に配置された第2絶縁層15を含む薄膜トランジスタと、第1絶縁層及び第2絶縁層上に配置され、ソース電極及びドレイン電極のうち一つと連結される画素電極117と、ゲート電極と同一層で形成された下部電極314及び画素電極と同一材料を含む上部電極317を含むキャパシタと、第2絶縁層と画素電極との間及び下部電極と上部電極との間に直接配置された第3絶縁層116と、ソース電極、ドレイン電極及び上部電極を覆って画素電極を露出させる第4絶縁層19と、を含む薄膜トランジスタアレイ基板。

(もっと読む)

電気光学装置および電子機器

【課題】画素を透過する光の透過率が高く、光源から発する光を有効に利用可能な電気光学装置および電子機器を提供すること。

【解決手段】本適用例の電気光学装置としての液晶装置は、素子基板10と、画素に配置された透光性の画素電極15と、素子基板10と画素電極15との間に設けられ、誘電体層16bを介して対向配置された一対の透光性電極を有する蓄積容量16と、蓄積容量16と画素電極15との間に設けられた第3層間絶縁膜14と、を備え、画素を透過する光の分光分布が、少なくとも赤、緑、青の各波長範囲に対応して透過率のピークを有するように、画素電極15、一対の透光性電極としての第1電極16aおよび第2電極16c、ならびに第3層間絶縁膜14のそれぞれの膜厚が設定されている。

(もっと読む)

表示装置およびその製造方法

【課題】容易に製造することが可能な構造を備える表示装置を提供する。

【解決手段】各サブピクセルは、1つの有機EL素子が設けられる素子形成領域と、コンタクトスペーサーが設けられる素子非形成領域とから構成され、複数のピクセルは、前記第2基板の表面上において、第1方向に延在する複数本の直線に沿ってそれぞれ配置され、第2基板上の1つのピクセルにおいて、当該ピクセルを構成する複数のサブピクセルの素子非形成領域は、前記第1方向に沿って配置され、第2基板上の1つのピクセルにおいて、当該ピクセルに設けられる複数のサブピクセルの素子形成領域は、第2方向に沿って配置され、第2基板上の1つの直線上に配列される複数のピクセルにおいて、全てのサブピクセルの素子非形成領域は前記第1方向に沿って配置され、同種類の光を放射するサブピクセルの素子形成領域は前記第1方向に沿って配置される、表示装置。

(もっと読む)

電気光学装置および電子機器

【課題】画素を透過する光の透過率が高く、光源から発する光を有効に利用可能な電気光学装置および電子機器を提供すること。

【解決手段】本適用例の電気光学装置としての液晶装置は、第1基板としての素子基板が、複数の画素電極を有し、第2基板としての対向基板20が、第1透光性導電層23aと、第1透光性導電層23aの複数の画素電極と対向する第1領域E1に配置された第2透光性導電層23cと、第1透光性導電層23aと第2透光性導電層23cとの間に配置された第1絶縁膜23bと、を有し、対向基板20の第1領域E1を透過する光の分光分布が、可視光波長範囲でほぼフラットとなるように、第1透光性導電層23a、第1絶縁膜23b、第2透光性導電層23cの膜厚がそれぞれ設定されている。素子基板と対向基板20とを接着するシール材40が設けられる対向基板20の第2領域E2には、第1透光性導電層23aが配置されている。

(もっと読む)

アクティブマトリクス基板

【課題】本発明は、アクティブマトリクス基板にマトリクス状に配列された各々の有機半導体トランジスタの形成面積が小さく、かつ表示装置に用いた場合に均一で視認性に優れた画像表示を行うことを可能とするアクティブマトリクス基板を提供することを主目的とする。

【解決手段】樹脂製基材と、上記樹脂製基材上に形成され、ゲート電極、ソース電極、ドレイン電極、および有機半導体材料を含む有機半導体層を備える有機半導体トランジスタとを有し、上記有機半導体トランジスタがマトリクス状に複数配列されているアクティブマトリクス基板であって、隣接する2つの上記有機半導体トランジスタが、1つの上記有機半導体層のみを共有していることを特徴とするアクティブマトリクス基板を提供することにより上記課題を解決する。

(もっと読む)

有機発光表示装置の製造方法

【課題】単純化された有機発光表示装置の製造方法を提供する。

【解決手段】基板本体上にゲート絶縁膜を形成する段階と、ゲート絶縁膜上に透明導電層及びゲート金属層を順次に形成する段階と、透明導電層及びゲート金属層を共にパターニングして透明導電層部及びゲート金属層部を含む複層構造を有する画素電極中間体、及び、ゲート電極を形成する段階と、画素電極中間体及びゲート電極上に層間絶縁膜を形成する段階と、層間絶縁膜に画素電極中間体の一部を露出する開口部を形成する段階と、層間絶縁膜上にデータ金属層を形成する段階と、データ金属層をパターニングしてソース電極及びドレイン電極を形成し、層間絶縁膜の開口部を通して露出された画素電極中間体のゲート金属層部を除去して画素電極を形成する段階と、を含む。

(もっと読む)

液晶表示装置

【課題】液晶表示装置の消費電力を低減すること及び表示の劣化を抑制すること。また、温度などの外部因子による表示の劣化を抑制すること。

【解決手段】各画素に設けられるトランジスタとして、チャネル形成領域が酸化物半導体層によって構成されるトランジスタを適用する。なお、酸化物半導体層を高純度化することで、トランジスタの室温におけるオフ電流値を10aA/μm以下且つ85℃におけるオフ電流値を100aA/μm以下とすることが可能である。そのため、液晶表示装置の消費電力を低減すること及び表示の劣化を抑制することが可能になる。また、上述したようにトランジスタは、85℃という高温においてもオフ電流値を100aA/μm以下とすることが可能である。そのため、温度などの外部因子による液晶表示装置の表示の劣化を抑制することができる。

(もっと読む)

電気光学装置、及び電子機器

【課題】不良の発生が抑制され高いコストパフォーマンスを有する電気光学装置、及び電子機器を提供する。

【解決手段】素子基板上に設けられた、TFT30と、TFT30に対応して設けられた画素電極15と、TFT30と画素電極15との間に設けられたデータ線6aと、データ線6aと画素電極15との間に設けられた第1容量電極16aと、第1容量電極16aと画素電極15との間に設けられ、第1容量電極16aの一部に誘電体層を介して対向配置されると共に、電気的にTFT30と画素電極15とに接続された第2容量電極16bと、を備え、第2容量電極16bは、アモルファスタングステンシリサイド膜からなる。

(もっと読む)

表示装置及び電子機器

【課題】信号線駆動回路が有するスイッチ回路を画素部と同じ基板上に配置する構成において、スイッチ回路を構成するトランジスタサイズを縮小し、データを供給することによる信号線の充放電を行う際の回路内の負荷を削減する

【解決手段】映像信号が入力される画素部と、映像信号の画素部への出力を制御するためのスイッチ回路部を有する信号線駆動回路を有し、スイッチ回路部は、絶縁基板上において、電界効果移動度が少なくとも80cm2/Vs以上であるトランジスタを有し、トランジスタは、酸化物半導体層を有する。

(もっと読む)

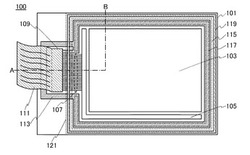

表示装置および電子機器

【課題】封止性能を低減させることなく狭額縁化を実現することが可能な表示装置を提供する。

【解決手段】液晶表示装置1Aは、駆動側基板10および対向基板18間に設けられると共に、複数の画素を有する画素部10Aと、駆動側基板10上において、画素部10Aの周辺の額縁領域10Bに配設されたトランジスタTFT11と、額縁領域10Bにおいて、トランジスタTFT11を被覆して設けられた平坦化膜13(絶縁膜)と、画素部10Aを封止すると共に平坦化膜13の端縁部13eを覆って設けられたシール層19とを備えたものである。

(もっと読む)

電気光学装置の製造方法

【課題】層間絶縁膜のコンタクトホールの内部にコンタクト用導電膜および埋め込み膜を設けた場合でも、コンタクトホールの外部で画素電極とコンタクト用導電膜とを確実に導通させることができる電気光学装置の製造方法を提供すること。

【解決手段】電気光学装置100を製造するにあたって、層間絶縁膜45上にコンタクトホール45aの底部45eおよび内壁45fに重なるコンタクト用導電膜90をITO膜により形成した後、コンタクトホール45aの内部を埋める埋め込み膜48をシリコン酸化膜により形成し、その後、埋め込み膜48に対して反応性イオンエッチングを行い、コンタクト用導電膜90を露出させる。また、コンタクトホール45aの内部には埋め込み膜48を残す。その際、埋め込み膜48とコンタクト用導電膜90とのエッチング選択比を利用して埋め込み膜48を選択的に除去してコンタクト用導電膜90を露出させる。

(もっと読む)

薄膜トランジスタ基板およびその製造方法

【課題】高い表示品位を有する表示装置用の薄膜トランジスタ基板およびこれらを生産効率よく実現することができる製造方法を提供する。

【解決手段】基板1上の複数の部分に配設された半導体膜2と、半導体膜2上に、該半導体膜2と接し互いに離間して配設されたソース電極およびドレイン電極4と、半導体膜2、ソース電極3およびドレイン電極4を覆うゲート絶縁膜6と、ゲート絶縁膜6を介して、ソース電極3およびドレイン電極4の間に跨るように配設された、ゲート電極7とを有した薄膜トランジスタ201と、半導体膜2上に、該半導体膜と接して配設された補助容量電極10と、下層に半導体膜2を有してソース電極から延在するソース配線31と、ゲート電極7から延在するゲート配線71と、ドレイン電極4に電気的に接続された画素電極9と、隣り合う画素の補助容量電極10どうしを電気的に接続する、補助容量電極接続配線12とを備えている。

(もっと読む)

半導体装置及びその作製方法

【課題】半導体装置をより少ない工程で作製する。

【解決手段】トランジスタと、画素電極とを有し、トランジスタは、第1のゲート電極と、第1のゲート電極上の第1の絶縁層と、第1の絶縁層上の半導体層と、半導体層上の第2の絶縁層と、第2の絶縁層上の第2のゲート電極とを有し、第1のゲート電極は、第1の絶縁層を介して、半導体層と重なる領域を有し、第2のゲート電極は、第2の絶縁層を介して、半導体層と重なる領域を有し、画素電極は、第2の絶縁層上に設けられ、第1の領域は、第2のゲート電極の少なくとも一部が、半導体層の少なくとも一部と重なる領域のうちの、少なくとも一部の領域であり、第2の領域は、画素電極が設けられた領域のうちの、少なくとも一部の領域であり、第1の領域における第2の絶縁層は、第2の領域における第2の絶縁層よりも薄い。

(もっと読む)

半導体装置

【課題】電気的特性が向上した、酸化物半導体を用いた半導体装置を提供することを目的

の一とする。

【解決手段】13族元素および酸素を含む第1の絶縁膜と、第1の絶縁膜と一部が接する

酸化物半導体膜と、酸化物半導体膜と電気的に接続するソース電極およびドレイン電極と

、酸化物半導体膜と重畳するゲート電極と、酸化物半導体膜とゲート電極の間の、酸化物

半導体膜と一部が接する第2の絶縁膜と、を有する半導体装置である。また、13族元素

および酸素を含む第1の絶縁膜には、化学量論的組成比より酸素が多い領域が含まれる構

成とする。

(もっと読む)

アクティブマトリクス型有機発光表示装置

【課題】 有機発光ダイオードの色毎に異なる発光効率や電圧-電流特性を補正することができ、有機発光ダイオードの陽極の電位変化に伴う駆動トランジスタのゲート電極−ソース電極間の電圧の変化のばらつきを低減することができるアクティブマトリクス型有機発光表示装置を提供する。

【解決手段】 アクティブマトリクス型有機発光表示装置は、複数色の何れか1色を発光可能な複数の画素PXR、PXG、PXBを備える。駆動トランジスタDRは、発光色毎にチャネル幅Wとチャネル長Lとの比が異なる。駆動トランジスタDRは、発光色毎にそれぞれ、1つのトランジスタ、又は直列に接続された2つ以上のトランジスタで形成される。駆動トランジスタDR内の有機発光ダイオードの陽極側のトランジスタのチャネル幅及びチャネル長は、全ての発光色の画素で等しい。

(もっと読む)

ディスプレイデバイス

【課題】向上した発光効率を有する、低電力のディスプレイを提供する。

【解決手段】前部および後部反射面の両方を有する光キャビティを利用する、空間光変調のための改良された装置および方法が開示される。光を空間変調するために、前部反射面内に、光透過領域が形成される。意図される見る人に面した前面と、光源に面した後面とを有する基板と、基板の前面の上に配置された誘電体材料層と、複数のアパーチャを含む、誘電体材料層の上に配置された金属層と、金属層の上に配置された複数の光変調シャッタ組立体102とを備え、複数のアパーチャは、複数の光変調シャッタ組立体102による変調のために、金属層を光源からの光が通過するのを許可する、ディスプレイデバイス。

(もっと読む)

半導体装置およびその製造方法、並びに表示装置

【課題】3層以上の配線を接続する際に、最も効率的にかつ最小面積で接続を行えるコンタクト構造を実現可能な半導体装置およびその製造方法、並びに表示装置を提供する。

【解決手段】基板201上に3層以上のn層の導電層202〜204が積層して形成され、n層の導電層がコンタクトパターンを介して接続され、コンタクトパターンが形成される一つの主コンタクト領域には、(n−1)個の導電層202,203を接続する(n−1)個の接続領域211,212を有し、(n−1)個の導電層のうち基板201に対する積層方向(基板201の主面に対する法線方向)において第1層より上層の導電層は、その終端部がコンタクトパターンCPTNの縁の一部に臨むように形成され、(n−1)個の導電層は、第n層の導電層により電気的に接続されている。第n層の導電層は、コンタクトパターンCPTNであるコンタクト孔を埋めつくよう形成されている。

(もっと読む)

画素チップ、表示パネル、照明パネル、表示装置および照明装置

【課題】発光素子の誤点灯を防止することの可能な画素チップと、そのような画素チップを画素として備えた表示パネルおよび照明パネルと、そのような表示パネルを備えた表示装置と、そのような照明パネルを備えた照明装置とを提供する。

【解決手段】画素チップは、1または複数の発光素子と、発光素子を駆動するドライバICと、発光素子とドライバICとの間に配置された接続部および遮光部とを備えている。接続部は、発光素子とドライバICとを互いに電気的に接続するものである。遮光部は、発光素子から発せられた光が直接にドライバICに入射するのを接続部とともに遮るものである。

(もっと読む)

41 - 60 / 1,011

[ Back to top ]