Fターム[5E070CB02]の内容

通信用コイル・変成器 (13,001) | コイル−プリントコイル(基板に印刷するもの) (2,690) | コイルパターンの印刷 (1,086) | 基板(グリーンシート)の片面に印刷するもの (808)

Fターム[5E070CB02]の下位に属するFターム

Fターム[5E070CB02]に分類される特許

61 - 80 / 440

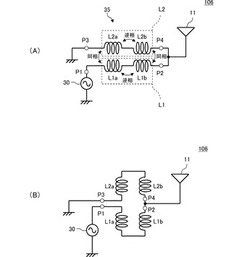

高周波トランス、電子回路および電子機器

【課題】製造が容易で小型化しやすい、低損失でエネルギーを伝送できる高結合度トランスを構成する。

【解決手段】高結合度トランス35はアンテナ素子11と給電回路30との間に接続される。高結合度トランス35は、給電回路30に接続された第1インダクタンス素子L1と、第1インダクタンス素子L1に結合した第2インダクタンス素子L2とを備え、第1インダクタンス素子L1の第1端は給電回路30に、第2端はアンテナ素子11にそれぞれ接続されていて、第2インダクタンス素子L2の第1端はアンテナ素子11に、第2端はグランドにそれぞれ接続される。

(もっと読む)

周波数安定化回路、アンテナ装置及び通信端末機器

【課題】放射体や筺体の形状、近接部品の配置状況などに影響されることなく、高周波信号の周波数を安定化させることのできる周波数安定化回路、アンテナ装置及び通信端末機器を構成する。

【解決手段】周波数安定化回路25は4つのコイル状導体L1〜L4を備え、第1のコイル状導体L1と第2のコイル状導体L2とが直列に接続されて第1の直列回路が構成され、第3のコイル状導体L3と第4のコイル状導体L4とが直列に接続されて第2の直列回路が構成され、アンテナポートと給電ポートとの間に第1の直列回路が接続され、アンテナポートとグランドとの間に第2の直列回路が接続されている。第1のコイル状導体L1と第2のコイル状導体L2は第1の閉磁路(磁束FP12で示すループ)が構成されるように巻回されていて、第3のコイル状導体L3と第4のコイル状導体L4は、第2の閉磁路(磁束FP34で示すループ)が構成されるように巻回されている。

(もっと読む)

フェライト積層電子部品の製造方法

【課題】内部導体の周囲のフェライトに残留する応力を低減して、良好な特性を備えたフェライト積層電子部品を効率よく製造することが可能なフェライト積層電子部品の製造方法を提供する。

【解決手段】Fe2O3粉末およびNiO粉末と、有機バインダーとを含む配合物を用いてグリーンシートを作製し、このグリーンシートを用いて、未焼成の内部導体を内蔵するグリーンシート積層体を形成した後、所定の条件で熱処理して、グリーンシート積層体の脱脂を行い、得られる脱脂後積層体を焼成することによりフェライト積層電子部品を製造するにあたって、Fe2O3粉末として、平均粒径が0.1〜0.5μm、比表面積が10m2/g以上のFe2O3粉末を用いる。

脱脂後積層体中の残留カーボン量が、重量基準で550〜1000ppmとなるような条件で脱脂を行う。

上記グリーンシートの作製に用いられる配合物として、仮焼工程を経ていない配合物を用いる。

(もっと読む)

ESD保護デバイス

【課題】複数のESD保護素子を備えたESD保護デバイスにおいて、あるESD保護素子を流れた静電気がグランドラインを介して他のESD保護素子に流れることを抑制できるESD保護素子を提供する。

【解決手段】絶縁体層20,22,24,26,28が積層された本体12内に、2組の入力端子14a,14cと出力端子16a,16cの間に接続された第1及び第2の信号ライン30,32と、第1及び第2のグランド電極40,42との間に、一定以上の電圧が加わると導通する第1及び第2のESD保護素子部60a,60cが形成されている。第1及び第2のグランド電極40,42の間を接続するグランド電極間配線58のインダクタンスは、グランド電極40,42とグランド端子18s,18tとを接続する第1及び第2のグランド配線50,52のインダクタンスよりも大きい。

(もっと読む)

インダクタを含む積層型電子部品

【課題】スルーホール等の貫通接続導体を用いずに積層体内部に複数層に亘ってインダクタを形成することにより製造工程の簡略化と電気特性の向上を図る。

【解決手段】第一積層体と、表面配線層を備えかつ第一積層体に接合した第二積層体とを含む積層型電子部品で、第一積層体と第二積層体の配線層は互いに直交し、第一積層体は、第一配線層に配した第一インダクタ用導体と、第二配線層に配した第二インダクタ用導体とを有し、第二積層体は、第一インダクタ用導体と第二インダクタ用導体がコイル状のインダクタを形成するように第一積層体との接合面において第一インダクタ用導体の端部と第二インダクタ用導体の端部を電気的に接続する接続導体を有する。

(もっと読む)

積層型コイル

【課題】 コイルパターンの径を大きくし、かつ積層体の外周面に絶縁膜を形成した積層型コイルにおいて、絶縁性をより確実にする。

【解決手段】 積層型コイル100は、絶縁層1と、コイルパターン2とが、所望の順番に積層され、一体化されてなる積層体3と、層の異なるコイルパターン2が相互に接続されて形成されたコイル5と、積層体3の両端に形成された1対の外部電極6a、6bと、積層体3の外周面に形成された絶縁膜7とを備え、コイルパターン2の少なくとも1つは、外周縁の少なくとも一部分が、絶縁層1の外周縁に接しているが、絶縁層1の4つの角部Cには接しないようにした。すなわち、コイルパターン非形成部Nを設けた。

(もっと読む)

コイル装置の製造方法

【課題】 高周波回路等に使用されるコイル装置製造方法に関して、L値を悪化させることなく、高周波性能の向上が可能なコイル装置の製造方法を提供する。

【解決手段】 第1絶縁層を形成する第1工程と、前記第1絶縁層上に、第1導電配線パターンを形成する第2工程と、前記第1導電配線パターン上に、パッドとして機能する第2導電配線パターンを形成する第3工程と、前記第1、第2導電配線パターンを含む第1絶縁層上に、感光性材料からなる第2絶縁層を形成する第4工程と、前記第2絶縁層における前記パッドと対応する位置に、ビアホールをフォトリソグラフィにより形成する第5工程と、前記第2絶縁層上に、第3導電配線パターンを形成するとともに、ビアホールの内部に導電材を充填してビアを形成する第6工程を実行する。これらの工程で形成した積層体を基材から剥離し、カット、脱脂、焼成を経て、外部電極を形成しチップ型コイル装置を得る。

(もっと読む)

コイル部品及びその製造方法

【課題】所望のフィルタ性能を確保しつつ、小型化且つ低背化され、低コストで製造可能なコイル部品を提供する。

【解決手段】コイル部品100は、磁性セラミック材料からなる磁性基板11と、磁性基板11の一方の主面に形成されたコイル導体を含む薄膜コイル層12と、薄膜コイル層12の主面にめっきにより形成された肉厚なバンプ電極13a〜13dと、バンプ電極13a〜13dの形成位置を除いた薄膜コイル層12の主面に形成された磁性樹脂層14とを備えている。バンプ電極13a〜13dの厚さは磁性樹脂層14の厚さと同等かそれ以上であり、積層体の底面及び隣接する2つの側面に露出面を有している。薄膜コイル層12は端子電極24a〜24dを含み、それらは対応するバンプ電極13a〜13dと一体的に形成されている。端子電極24a〜24dは薄膜コイル層12に埋め込まれており、且つ、積層体の隣接する2つの側面に露出面を有している。

(もっと読む)

コイル型電子部品およびその製造方法

【課題】 低コストにて生産でき、かつ、高い透磁率と高い飽和磁束密度の両方の特性を兼ね備えた磁性体を用いたコイル型電子部品を提供する。

【解決手段】 素体の内部あるいは表面にコイルを有するコイル型電子部品であって、コイル型電子部品での素体は、鉄、ケイ素および鉄よりも酸化しやすいを含有する軟磁性合金の粒子群から構成され、各軟磁性体粒子の表面は当該粒子が酸化した酸化層が形成され、当該酸化層は当該合金粒子に比較して鉄よりも酸化しやすいを多く含み、粒子同士は、当該酸化層を介して結合されている。

(もっと読む)

スパイラル型のインダクタ及び半導体装置

【課題】インダクタ上に形成する導電性接着材によるインダクタのL値の変動のばらつきを抑えることを目的としている。

【解決手段】本発明のスパイラル型のインダクタ10は、半導体基板20上に螺旋状に形成したスパイラルコイル30と、前記半導体基板20上に形成し、前記スパイラルコイル30の両端と電気的に接続する一対の端子と、前記半導体基板20上の前記一対の端子を露出させて、前記スパイラルコイル30の保護層36上の全面を覆う遮蔽層40と、を備えたことを特徴とする。

(もっと読む)

積層型電子部品及びその製造方法

【課題】インダクタ素子部における内部電極の主成分をAgにしても、高密度であり且つインダクタ素体の劣化が十分に抑制されたインダクタ素体を備える積層型電子部品を提供すること。

【解決手段】インダクタ素体10とインダクタ素体10の内部に配置された内部電極16とを有するインダクタ素子部6を備える積層型電子部品100であって、インダクタ素体10がフェライト組成物及びホウ素酸化物を含有するフェライト焼結体からなり、内部電極16におけるAgの含有率が85質量%以上であり、隣接する内部電極16の間におけるフェライト焼結体のAg含有率が0.18質量%以下である積層型電子部品100である。

(もっと読む)

複合電子部品の製造方法

【課題】静電容量が小さく且つ放電特性、耐熱性及び耐候性に優れた静電気対策素子とコモンモードフィルタとを組み合わせて構成された小型で高性能な複合電子部品の製造方法を提供する。

【解決手段】複合電子部品の製造方法は、第1及び第2の磁性基体11a、11bの間に静電気対策素子層12b及びコモンモードフィルタ層12aを形成する工程を備え、静電気対策素子層12bを形成する工程は、下地絶縁層27を形成する工程と、下地絶縁層27の表面においてギャップを介して相互に対向位置された電極を形成する工程と、少なくとも電極間に静電気吸収層30を形成する工程を含む。静電気吸収層30は、絶縁性無機材料のマトリックス中に導電性無機材料が不連続に分散したコンポジットであって、電極が形成された下地絶縁層の表面に島状に点在した導電性無機材料の層と、導電性無機材料を覆う絶縁性無機材料の層との積層構造である。

(もっと読む)

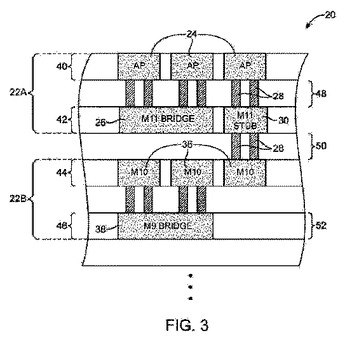

直列接続のインダクターを有する集積回路

集積回路インダクターは、直列に接続されている上部ループ形状のライン部分と下部ループ形状のライン部分とを有し得る。上部部分および下部部分は、45°曲がりを有し得、6角形または8角形のループを形成する。各ループ部分は、1つ以上のターンを有し得る。金属ルーティング層の介在する金属フリー領域が、容量性カップリングを低減させるために、2つの層の間に形成され得る。各ループ部分は、ビアによって並列にショートされた2つ以上の金属ラインのセットを有し得る。上部ループおよび下部ループは、容量性カップリングを低減させるために、横にオフセットされ、または入れ子にされ得る。  (もっと読む)

(もっと読む)

コモンモードノイズフィルタ

【課題】本発明は、インピーダンスを向上させ、かつインピーダンスを調整することが容易なコモンモードノイズフィルタを提供することを目的とするものである。

【解決手段】本発明のコモンモードノイズフィルタは、第1の導体12と第2の導体13とを第2の絶縁層11bに形成された第1のビア電極16aで接続し、かつ第3の導体14と第4の導体15とを第4の絶縁層11dに形成された第2のビア電極16bで接続し、さらに少なくとも第3の絶縁層11cを非磁性体で構成するとともに、前記第3の絶縁層11cにおいて前記第2の導体13、第3の導体14の内側に磁性材料からなる磁性体部17を2つ設け、上面視にて前記2つの磁性体部17の間に第1のビア電極16a、第2のビア電極16bが位置するようにしたものである。

(もっと読む)

複合電子部品

【課題】静電容量が小さく且つ放電特性に優れた静電気対策素子とコモンモードフィルタとを組み合わせて構成された小型で高性能な複合電子部品を提供する。

【解決手段】複合電子部品100は、第1及び第2の磁性基体11a、11bに挟まれたコモンモードフィルタ層12a及び静電気対策素子層12bによって構成されている。コモンモードフィルタ層12aは互いに磁気結合された略矩形状のスパイラル導体17,18を備えている。静電気対策素子層12bは、下地絶縁層27の表面に形成されたギャップ電極28,29と、ギャップ電極を覆う静電気吸収層30とを備えている。ギャップ電極28,29のギャップはインダクタンス素子の導体パターンと重ならない位置に配置されており、ギャップの長手方向は第1及び第2のスパイラル導体の直線部分と平行である。静電気吸収層30は静電気保護材料として機能し、過電圧が印加された際に初期放電が確保される。

(もっと読む)

電子部品及びその製造方法

【課題】本発明の目的は、内蔵される回路素子を大きく形成することができると共に、簡単な製造工程により製造できる電子部品及びその製造方法を提供することである。

【解決手段】積層体12は、複数の絶縁体層が積層されてなる。コイルLは、積層体12に内蔵され、かつ、絶縁体層間から積層体12の側面から外部に露出している露出部19を有している。フェライト膜20は、露出部19を覆うように積層体12の側面に設けられている。

(もっと読む)

半導体装置

【課題】 2巻きの渦巻き状であって1箇所において立体的に交差する薄膜インダクタ素子を備え、該薄膜インダクタ素子の両端部側から見たときの特性がほぼ均等となるようにする。

【解決手段】 薄膜インダクタ素子13は、絶縁膜上に1箇所が欠けた環状に設けられた外側上層配線14と、絶縁膜上において外側上層配線14の内側に同一側の1箇所が欠けた環状に設けられた内側上層配線15と、絶縁膜下に外側上層配線14の一端部及び内側上層配線15の一端部に接続されて設けられた下層配線16とを有する。この場合、外側上層配線14の長さと内側上層配線15の長さは同じかほぼ同一で、その差が小さいので、薄膜インダクタ素子13の両端部側から見たときの特性をほぼ均等とすることができる。

(もっと読む)

積層型電子部品の製造方法

【課題】 素体の端面と端面に隣接する面に導体ペーストを塗布し、焼き付けるため、導体ペーストを素体の端面と端面に隣接する面に塗布する工程と導体ペーストを焼き付ける工程が必要になると共に、高価な装置が必要となる。また、素体の上面に外部端子が形成されているので、シールドが施された回路や電子機器に実装する場合、素体の上面に絶縁体を設ける必要がある。

【解決手段】 絶縁体層と導体パターンを積層し、上面に導体パターンに接続された複数の引出し導体が露出した積層体を形成する。次に、積層体の上面に引出し導体に接続された複数の外部端子電極を形成し、複数の外部端子電極が形成された積層体の上面に有機物質膜を形成する。続いて、有機物質膜が形成された積層体を切断し、それぞれの素体に分割する。さらに、素体を焼成することにより、有機物質膜を焼失させて外部端子電極を露出させ、素体底面にのみ外部端子を形成する。

(もっと読む)

ノイズ対策構造

【課題】コモンモードノイズ抑制効果を劣化させることなく、差動伝送路上に容易に構築することができるノイズ対策構造を提供する。

【解決手段】コモンモードチョークコイル2の外部電極6−1,6−4を差動伝送路101,102にそれぞれ直付けした。また、外部電極6−2,6−3は、パターン106,106,コンデンサ7,7を通じてグランドパターン121,121に接続した。これにより、差動信号のグランドパターン121,121側への流出を、コモンモードチョークコイル2によって阻止し、コモンモードノイズだけをグランドパターン121,121に流出する。このとき、コモンモードチョークコイル2と差動伝送路101,102との間に余分なパターンがないので、ノイズを効率よくグランドパターン121,121側に流出させることができる。

(もっと読む)

積層バランスフィルタ

【課題】小型化が容易であり、入出力間で所定のインピーダンス変換を行えるようにした積層バランスフィルタを構成する。

【解決手段】第1のキャパシタ電極121とグランド電極120とが対向することによって不平衡側のキャパシタが構成される。誘電体層271には不平衡側コイル131が形成されている。誘電体層271,241,242には平衡側コイル141,142,143が形成されている。平衡側コイル141、142,143はヘリカル状に形成されており、かつ、各コイルの巻き方向も同じ方向となるように形成されている。この3つの平衡側コイル141,142,143のうち中央のコイル142は不平衡側コイル131に近接配置されることにより、中央のコイル142は不平衡側コイル131と電磁界結合する。

(もっと読む)

61 - 80 / 440

[ Back to top ]