Fターム[5F004DB07]の内容

半導体のドライエッチング (64,834) | 被エッチング物 (6,778) | Si3N4 (525)

Fターム[5F004DB07]に分類される特許

21 - 40 / 525

基板処理方法

【課題】処理対象の基板に対し、半導体デバイスの小型化要求を満たす寸法の開口部であって、エッチング対象膜に転写するための開口部をマスク膜又は中間膜に形成する基板処理方法を提供する。

【解決手段】アモルファスカーボンの下層レジスト膜71、ハードマスクとしてのSiON膜72、反射防止膜73及びフォトレジスト膜74が順に積層されたシリコン基材70において、CF3IガスとH2ガスとの混合ガスから生成されたプラズマによってフォトレジスト膜74の開口部75の側壁面にデポ76を堆積させて開口部75の開口幅を縮小させるシュリンク工程と、反射防止膜73及びSiON膜72をエッチングするエッチング工程とを1ステップで行う。

(もっと読む)

複合材料の目標エッチングプロセス特性を達成するためのガスクラスタイオンビームエッチングプロセス

【課題】種々の材料のガスクラスタイオンのビーム(GCIB)エッチングプロセスを実行するための方法及び装置を提供する。

【解決手段】第1の材料、第2の材料及び前記第1の材料及び/又は第2の材料を曝露する表面を持つ基板を保持するための基板ホルダ回りを減圧環境に維持し、1又はそれ以上の目標エッチングプロセス特性を選択し、少なくとも1つのエッチングガスを含む加圧ガスからガスクラスタイオンビーム(GCIB)を形成し;前記1又はそれ以上の目標エッチングプロセス特性を達成するために前記GCIBについてのGCIBプロセス条件の1又はそれ以上のGCIB性質を設定し;前記減圧環境を通じて前記GCIBを加速し;及び前記基板の前記表面の少なくとも1部分に前記GCIBを照射して、前記第1の材料及び前記第2の材料の少なくとも1部分をエッチングする。

(もっと読む)

キャビティをシールする方法

【課題】標準的なCMOSプロセスに適合し、かつゲッタ材料又は反応性ガスに依存しないでキャビティをシールする方法を提供する。

【解決手段】キャビティ910は犠牲材料をエッチングにより除去することで形成され、キャビティのシールはキャビティより下側の材料がスパッタエッチングされ、キャビティに通じる通路の上及び中に再堆積されることでシールされる。キャビティに通じる通路の上に堆積された材料904も再びスパッタエッチングされ、キャビティに通じる通路内に再堆積される。スパッタエッチングを不活性雰囲気で行うことにより、スパッタエッチングの後にはキャビティ内は不活性ガスで充填される。

(もっと読む)

クリーニング方法、半導体デバイスの製造方法および基板処理装置

【課題】従来のエッチングガス供給の問題を解決し、均一なエッチング、延いては均一な反応管内のクリーニングを行なうこと。

【解決手段】反応室内にクリーニングガスを供給する前の所定時点から反応室内にクリーニングガスを供給開始から数秒経過する時点までに、完全に排気を停止もしくはクリーニングガスの均一な拡散に影響がない程度の排気量で排気させ、反応室内の圧力が10Torr以上となるまでクリーニングガスを供給する第1段階と、反応室内の圧力が下がるよう反応室内を排気する第2段階と、を有し、第1段階と第2段階とを1サイクル以上行う。

(もっと読む)

ドライエッチング剤

【課題】地球環境に対する影響が小さく、かつ必要とされる性能を有するドライエッチング剤を提供する。

【解決手段】(A)式:CaFbHc(式中、a、b及びcは、それぞれ正の整数を表し、2≦a≦5、c<b≧1、2a+2>b+c、b≦a+cの関係を満たす。但し、a=3、b=4、c=2の場合を除く。)で表される含フッ素不飽和炭化水素と、(B)O2、O3、CO、CO2、COCl2、COF2、F2、NF3、Cl2、Br2、I2及びYFn(但し、YはCl、Br又はIを表す。nは1〜5整数を表す。)からなる群より選ばれる少なくとも1種のガスと、(C)N2、He、Ar、Ne、Xe及びKrからなる群より選ばれる少なくとも1種のガスとを、それぞれ特定の体積%で含む、ドライエッチング剤を提供する。

(もっと読む)

半導体光素子を作製する方法、及び半導体光素子

【課題】導波路メサを含む半導体光素子の作製において、へき開経路の乱れを低減可能な、半導体光素子を作製する方法を提供する。

【解決手段】半導体バーBAR1及び基板生産物SP1は、それぞれ、単一のへき開動作により生成されたへき開面CL1、CL2を有する。へき開面CL1には転写マース及び残留マークが現れる。転写マース及び残留マークがしっかりと案内して、このへき開面が形成される。へき開により、残留マーク35aは第1窪み51a及び第2窪み53aに分離され、残留マーク35bは第1窪み51b及び第2窪み53bに分離される。転写マーク37aは第1窪み55a及び第2窪み57aに分離され、転写マークは37b第1窪み55b及び第2窪み57bに分離される。半導体バーBAR1のへき開面CL1は、残留マークからの第1窪み51a、51b及び転写マークからの第1窪み55a、55bを有する。

(もっと読む)

アンテナ、誘電体窓、プラズマ処理装置及びプラズマ処理方法

【課題】基板表面処理量の面内均一性も改善することができるアンテナ、誘電体窓、プラズマ処理装置及びプラズマ処理方法を提供する。

【解決手段】アンテナは、誘電体窓と、前記誘電体窓の一方面に設けられたスロット板とを備えている。前記誘電体窓の他方面は、環状の第1凹部147に囲まれた平坦面146と、平坦面146の重心位置を囲むように、平坦面146内に形成された複数の第2凹部153とを有している。前記スロット板の主表面に垂直な方向からみた場合、前記スロット板におけるそれぞれのスロット133内に、それぞれの第2凹部153の重心位置が重なって位置している。

(もっと読む)

プラズマ処理方法

【課題】本発明は、堆積性のガスを用いたプラズマ処理において、被処理体の処理枚数の増加による異物を抑制できるプラズマ処理方法を提供する。

【解決手段】本発明は、処理室内に導入された堆積性ガスからプラズマを生成し、当該処理室内に設けられた試料台上に載置される被処理体を、高周波電力を印加した状態で前記プラズマに曝すことにより前記被処理体のエッチングを行うプラズマ処理方法において、前記被処理体を前記プラズマに曝す第一の期間と、前記被処理体を前記プラズマに曝し当該第一の期間よりも前記被処理体に対するエッチングレートの低い第二の期間とを繰り返すことにより、前記処理室内壁面への堆積膜がアモルファスになるエッチング条件で前記被処理体をエッチングすることを特徴とする。

(もっと読む)

化合物半導体装置

【課題】 電流コラプスを抑制するとともに、高耐圧動作が可能な化合物半導体装置及びその製造方法を提供する。

【解決手段】 SiC基板10上に形成されたi−GaNバッファ層12と、i−GaNバッファ層12上に形成されたn−AlGaN電子供給層16と、n−AlGaN電子供給層16上に形成されたn−GaNキャップ層18と、n−GaNキャップ層18上に形成されたソース電極20及ドレイン電極22と、ソース電極20とドレイン電極22との間のn−GaNキャップ層18上に形成されたゲート電極26と、ソース電極20とドレイン電極22との間のn−GaNキャップ層18上に形成された第1の保護層24と、ゲート電極26とドレイン電極22との間の第1の保護層24に形成されたn−GaNキャップ層18に達する開口部28に埋め込まれ、第1の保護層24とは異なる絶縁層よりなる第2の保護層30とを有する。

(もっと読む)

シリコンに対する誘電材料の選択エッチング方法及びシステム

【課題】 本発明はドライプラズマエッチングを用いた基板のエッチング方法に関する。

【解決手段】 ドライプラズマエッチングシステム内で誘電体層をシリコン及びポリシリコンに対して選択的な均一エッチングを行う方法及びシステムが記載されている。エッチング用化学は、たとえばCH2F2やCHF3のようなフルオロハイドロカーボンを有する。高いエッチング選択性及び受容可能な均一性は、CH2F2の流速やドライプラズマエッチングシステムと結合する出力を含むプロセス条件を選択することによって実現されて良い。それにより、エッチングプラズマ中での活性エッチングラジカルとポリマー生成ラジカルとの適切なバランスがとられる。

(もっと読む)

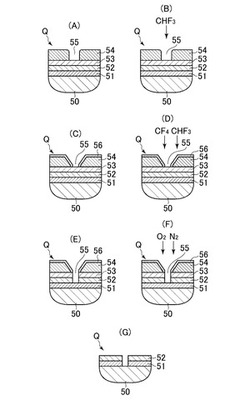

炭化珪素半導体装置の製造方法

【課題】不純物領域の自己整合的な形成を精度よく行うことができる、炭化珪素半導体装置の製造方法を提供する。

【解決手段】マスク層31の開口部OPを介して炭化珪素基板90上に第1導電型不純物が注入される。第1および第2の材料のそれぞれから作られた第1および第2の膜32、33が成膜される。異方性エッチング中に第1の材料のエッチングが生じたことが検知され、異方性エッチングが停止される。第1および第2の膜32、33によって狭められた開口部OPを介して、炭化珪素基板90上に第2導電型不純物が注入される。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】ゲート電極の側壁側にサイドウォールを精度よく形成することが可能な半導体装置の製造方法及び半導体装置を提供することを目的とする。

【解決手段】まず、SOI基板5の一方面側においてゲート電極34上及びゲート電極34の周囲の領域に第1絶縁膜40を形成する。次に、第1絶縁膜40上に積層させる構成で第1絶縁膜40とは材質の異なる第2絶縁膜42を形成する。そして、第1絶縁膜40及び第2絶縁膜42におけるゲート電極34の側壁34a側の部分を残しつつ、第2絶縁膜42よりも第1絶縁膜40のほうが、エッチング速度が遅くなるように第1絶縁膜40及び第2絶縁膜42を除去し、ゲート電極34の側壁34a側にサイドウォール45を形成する。

(もっと読む)

プラズマ処理装置および処理方法

【課題】従来のプラズマ処理では、ウエハ外周周辺部の等電位面が湾曲し、ウエハ外周部周辺のエッチングレートが不均一であるという課題がある。

【解決手段】ウエハ載置用電極111の段差部に、ウエハ載置用電極111と同電位となるように設けたリング状部材303が配置され、かつ前記リング状部材303の上面をウエハ載置用電極111の上面より高くすることでウエハ外周部周辺の等電位面301の湾曲を改善し、ウエハ外周周辺部のエッチングレートを高均一化するプラズマ処理装置および処理方法。

(もっと読む)

加工装置および加工条件算出方法

【課題】装置保守によって装置状態が大きく変わった場合に、その装置状態に適合するモデルを短時間で導出する手法を提供することを目的とする。

【解決手段】実績データの加工量と、この時の加工条件とを用いて加工量予測重回帰式を調整し、

得られた加工量予測重回帰式を用いて、加工対象の加工目標値と加工量予測重回帰式に含まれる加工条件以外の説明因子とから加工条件を算出する手段を備え、

得られた加工条件で加工することを特徴とする加工装置。

(もっと読む)

回折格子を作製する方法

【課題】 モールドパターンに樹脂を充填できると共に、余剰の樹脂によって除去困難な厚さのバリが形成されることを防止できる回折格子作製方法を提供する。

【解決手段】 プライマ層60上に樹脂Uを配置した後に、モールド1押し付ける。プライマ層60は、モールド1よりも濡れ性が低い。モールドパターンMPの溝部Maに樹脂Uが充填される。プライマ層60は、第1の部分P1上に形成される。また、プライマ層60は、第2の部分P2には形成されない。第2の部分P2上では絶縁膜30が露出している。絶縁膜30はプライマ層60よりも濡れ性が高い。樹脂Uにモールド1を押し付けたときに、モールド1とプライマ層60との間からはみだした余剰樹脂Uaが絶縁膜30に広がる。余剰樹脂Uaが、突出部3の側面3bに沿って盛り上がらない。余剰樹脂Uaによって除去困難な厚さのバリが形成されない。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】良好な側壁形状の開口を有する半導体装置の製造方法および半導体装置を提供する。

【解決手段】GaAs基板101上に形成された誘電体膜102の一部を誘電体膜102の表面から所定の深さまでエッチングする第1のエッチング工程と、第1のエッチング工程により誘電体膜102がエッチングされた第1のエッチング領域11において誘電体膜102をエッチングしてGaAs基板101の表面を露出し、かつ、第1のエッチング領域11を包含する第2のエッチング領域12において第1のエッチング領域11以外の領域に配置された誘電体膜102を所定の膜厚までエッチングする第2のエッチング工程とを含む。

(もっと読む)

シリコン含有物のエッチング方法

【課題】被処理物が有機物にて汚染されている場合でも、シリコン含有物を効率良くエッチングする。

【解決手段】原料ガスを大気圧近傍のプラズマ空間23に導入してエッチングガスを生成する(生成工程)。エッチングガスを、温度を10℃〜50℃とした被処理物90に接触させる(エッチング反応工程)。原料ガスは、フッ素含有成分と、水(H2O)と、窒素(N2)と、酸素(O2)と、キャリアガスを含む。原料ガス中の窒素と酸素とキャリアガスの合計体積流量(A)とフッ素含有成分の体積流量(B)との比は、(A):(B)=97:3〜60:40である。原料ガス中の窒素と酸素の合計体積流量は、窒素と酸素とキャリアガスの合計体積流量の2分の1以下である。窒素と酸素の体積流量比は、N2:O2=1:4〜4:1である。

(もっと読む)

プラズマ処理装置及びプラズマ処理方法

【課題】広範囲の繰り返し周波数帯域で高精度に制御可能な時間変調された間欠的な高周波電力を供給する高周波電源を備えるプラズマ処理装置及び前記プラズマ処理装置を用いたプラズマ処理方法を提供する。

【解決手段】真空容器と、該真空容器内にプラズマを生成するプラズマ生成手段と、前記真空容器内に設置され試料を載置する試料台と、時間変調された間欠的な高周波電力を前記試料台に印加する高周波電源とを備えるプラズマ処理装置において、前記高周波電源は、2つ以上の異なる周波数帯域を有し、前記周波数帯域のそれぞれが使用するアナログ信号の範囲が同じである繰り返し周波数によって高周波電力を時間変調することを特徴とするプラズマ処理装置である。

(もっと読む)

シリコン基板のエッチング方法、及びシリコン基板のエッチング装置

【課題】シリコン絶縁層とシリコン基板とを貫通する孔の加工の精度を配線が含まれる領域にて高めることのできるシリコン基板のエッチング方法、及びシリコン基板のエッチング装置を提供する。

【解決手段】ダミー配線13d,15dの埋め込まれた凹部を有して該凹部の内面にはバリアメタル層13b,15bが形成されたシリコン絶縁層13a,15aを有するシリコン基板11に対して、シリコン絶縁層13a,15aとシリコン基板11とを貫通する孔をダミー配線13d,15dが含まれる領域に形成する。ダミー配線13d,15d、バリアメタル層13b,15b、シリコン絶縁層13a,15aをエッチングした後にシリコン基板11をエッチングする。加えて、シリコン基板11のエッチングを終了する前に、シリコン絶縁層13a,15a及びシリコン基板11の少なくとも1つを希ガスでスパッタする。

(もっと読む)

基板処理方法および基板処理装置

【課題】より安価に基板表面の窒化膜をエッチングできる基板処理方法および基板処理装置を提供する。

【解決手段】表面に窒化膜が形成された基板Wは、処理室11内においてヒータユニット13上で保持される。処理流体導入口25から過熱水蒸気が導入され、この過熱水蒸気が基板Wに導かれる。この過熱水蒸気によって、基板W上の窒化膜がエッチングされる。処理室11の内壁は、処理室ヒータユニット50によって加熱される。均熱リング40は、基板Wの周縁部に接し、基板Wの温度を均一化する。

(もっと読む)

21 - 40 / 525

[ Back to top ]