Fターム[5F004EB03]の内容

半導体のドライエッチング (64,834) | エッチング対象部の機能 (2,366) | 層間絶縁膜 (379)

Fターム[5F004EB03]に分類される特許

21 - 40 / 379

エッチング方法

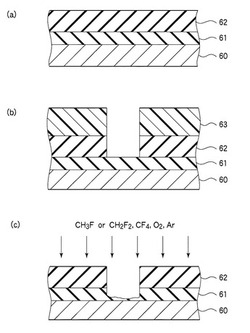

【課題】 有機Si系低誘電率膜をマスクとして被処理体のSiC部分をエッチングガスのプラズマによりエッチングする場合に、エッチングレートおよび有機Si系低誘電率膜に対するエッチング選択比を高くしてエッチングすることができるエッチング方法を提供すること。

【解決手段】 SiC膜61と、その上に形成された有機Si系低誘電率膜62とを有する構造において、有機Si系低誘電率膜62をマスクとしてSiC膜61をエッチングガスのプラズマによりエッチングするに際し、エッチングガスとして、CH2F2を含有するガスまたはCH3Fを含有するガスを用いる。

(もっと読む)

半導体装置の製造方法

【課題】 接続孔のホールサイズについて制御性良い半導体装置の製造方法を提供する。

【解決手段】 実施形態の半導体装置の製造方法では、半導体基板上に上層絶縁膜が形成され、前記上層絶縁膜上にSiを含む非晶質膜が形成される。前記非晶質膜上に第1のレジスト膜が形成され、前記第1のレジスト膜に第1のレジストパターンが形成される。前記第1のレジスト膜をマスクとして、前記非晶質膜が加工され、前記上層絶縁膜が露出される。前記第1のレジストパターンが除去され、前記非晶質膜および露出した前記上層絶縁膜上に遷移金属膜が形成される。前記非晶質膜および前記遷移金属膜の熱反応により、前記非晶質膜よりも体積が大きいシリサイド膜が形成される。前記遷移金属膜が除去され、前記シリサイド膜をマスクとして、前記上層絶縁膜を加工し、前記上層絶縁膜に第1の溝が形成される。

(もっと読む)

BCN系の絶縁膜及びその製造方法並びに半導体装置

【課題】従来のBCl3ガスに代わる、腐食性のない有機アミノボロン系ガスを用いてB

CN膜を成膜ことが特徴である。その例として、トリスジメチルアミノボロンを用いて、

プラズマCVDにより成膜を行うことで、安定した低誘電率と高い硬度(ヤング率)を有

するBCN膜が形成できる半導体装置の製造方法が提供すること。

【解決手段】 有機アミノボロン系ガスを用いて窒化ホウ素炭素(BCN)系絶縁膜を形

成する絶縁膜の製造方法。前記有機アミノボロン系ガスはトリスジメチルアミノボロンで

ある。比誘電率が2.5以下で弾性率(ヤング率)が8GPa以上であるBCN系の絶縁

膜。

(もっと読む)

基板処理方法および基盤処理装置

【課題】平行平板型RIE装置において、チャージアップダメージとパターンノッチングが軽減された効率的な処理を可能とする基板処理方法および基板処理装置を提供する。

【解決手段】チャンバ11と、前記チャンバ11内に配置される第1の電極13と、前記チャンバ11内に前記第1の電極13と対向して配置され、基板15を保持する第2の電極16と、前記第2の電極16に50MHz以上の周波数のRF電圧を印加するRF電源19と、前記第2の電極16に、前記RF電圧と重畳して負電圧パルスおよび正電圧パルスを含む電圧波形を繰り返し印加するパルス電源21から成る基板処理装置1を用いたエッチング処理において、前記パルス電源21から負パルス電圧を印加し、続いて正パルス電圧を印加する間に浮遊電位を出力する。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】選択メタルキャップを用いることなしに、生産性の高いエアギャップ配線を形成する。

【解決手段】ウエハ14上の絶縁膜200にCuダマシン配線210を形成する第1の工程と、ウエハ14上に第1のバリア膜220を形成する第2の工程と、後続する接続孔242を開口する工程において、接続孔242の孔底部244に露出するCu配線206と隣接する絶縁膜200、及び最小寸法スペースの3倍以上の幅をもつ幅広スペース200aを保護するように、第1のバリア膜220をパターニングする第3の工程と、第1のバリア膜220をマスクとして絶縁膜200を除去する第4の工程と、ウエハ14上に第2のバリア膜224を形成する第5の工程と、Cu配線206間にエアギャップ232を残しつつ絶縁膜230を形成する第6の工程と、を有する。

(もっと読む)

半導体装置の製造方法

【課題】加工膜と非加工膜をRIE法で選択的に加工するときに、非加工膜の加工量を低減させる半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、下地層1,7,8の上に非加工膜14を形成する工程と、非加工膜14および下地層1,7,8に溝4を形成する工程と、溝内を埋め込むように加工膜5を形成する工程と、非加工膜14を露出させるように加工膜5を平坦化する工程とを備える。更に、加工膜5および非加工膜14の上に保護膜16を形成する工程と、RIE法を用いて、保護膜16をエッチングすると共に、加工膜5を選択的にエッチングして溝内の加工膜5を落とし込む工程とを備える。

(もっと読む)

エッチング方法、エッチングシステムおよびエッチング装置

【課題】シリコン酸化膜にコンタクト部に到達する高アスペクト比のホールを形成する際に、ホール内のコンタクト材料とコンタクト部との間で十分なコンタクトがとれるようなホールを形成すること。

【解決手段】基板上にBおよびPの少なくとも一方を含むシリコン酸化物からなる第1の酸化膜と、その上に形成された、BおよびPを含まないシリコン酸化物からなる第2の酸化膜とを有し、さらに第1の酸化膜および第2の酸化膜の界面より下方に形成されたコンタクト部を有する被処理体を準備し(ステップ1)、第2の酸化膜と前記第1の酸化膜をエッチングしてコンタクト部に到達するホールを形成し(ステップ2)、HFガスおよび不活性ガスを用いたドライプロセスにより第1の酸化膜をエッチングし、第1の酸化膜のコンタクト部上方領域のホール部分を広げる(ステップ3)。

(もっと読む)

半導体素子用パターン構造物の形成方法

【課題】ラインパターン構造物の形成方法を提供すること。

【解決手段】ラインパターン構造物及びその形成方法において、ラインパターン構造物は切断部位を含むライン形状を有する少なくとも1つの第1ラインパターンを含む。最外郭に位置する前記第1ラインパターンと隣り合って前記第1ラインパターンと平行した延在ラインと、前記第1ラインパターンの切断部位と隣接する領域で前記第1ラインパターン方向へ向かうように前記延在ラインから突出された少なくとも1つの突出パターンを含む2つの第2ラインパターンを含む。前記ラインパターン構造物は不良が減少し、簡単な工程を通じて形成されてもよい。

(もっと読む)

半導体装置の作製方法

【課題】下地に対する選択比が大きく、テーパー形状の配線を形成するドライエッチング

方法を提供する。

【解決手段】基板上に導電性材料からなる膜を形成し、ICPエッチング装置を用いて前

記導電性材料からなる膜をドライエッチングして、テーパー角が60°以下の配線を形成

する。また、基板上に導電性材料からなる膜を形成し、ICPエッチング装置を用いて前

記導電性材料からなる膜をドライエッチングして、テーパー角が60°以下のゲート配線

を形成し、前記ゲート配線上にゲート絶縁膜を形成し、前記ゲート絶縁膜上に活性層を形

成する。

(もっと読む)

半導体装置及びその製造方法

【課題】D−RAMのキャパシタを形成するシリンダのドライエッチ加工において、従来技術の製造方法ではアスペクト比が高いシリンダやコンタクトの形状がボーイング形状となり隣接するホール間ショートの問題やホール内に形成する電極成膜のカバレッジ異常などの問題が発生する。

【解決手段】本発明ではシリコン酸化膜4aにコンタクトホールを形成する際にボーイングが発生する部分にLow−k膜の炭化シリコン酸化膜5を挿入して積層構造とし、ドライエッチでシリコン酸化膜4aのエッチング速度に対し、炭化シリコン酸化膜5のエッチング速度が1/5〜1/10と遅い条件にすることでボーイング形状の抑制を可能にした。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】ビア深さのバラツキを抑制することができる半導体装置の構造およびその製造方法を提供する。

【解決手段】半導体装置の製造方法は、基板上に、SiおよびCを含むキャップ絶縁膜を形成する工程と、キャップ絶縁膜上に、キャップ絶縁膜と比較して、シリコン原子数に対する炭素原子数の組成比が高い、有機シリカ膜を形成する工程と、不活性ガス、Nを含むガス、フッ化炭素ガスおよび酸化剤ガスを含む混合ガスを用いたプラズマ処理により、有機シリカ膜に、異なる開口径を有する2以上の凹部を形成する工程と、を含む。

(もっと読む)

基板洗浄方法及び基板洗浄装置

【課題】異種金属が露出した基板表面の洗浄において卑金属の溶解を防止する。。

【解決手段】基板保持台26に保持された基板24表面の周縁部の上方にノズル21を配置し、カーボン電極23Aを通じて電圧発生装置29により電圧を印加された薬液213をノズル21から基板24表面の周縁部に供給する。次に、薬液213をノズル21から供給しながら、基板24表面の中央部の上方にノズル21を移動させた後、薬液213をノズル21から基板24表面の中央部に供給する。

(もっと読む)

基板の製造方法、半導体装置の製造方法、電気光学装置

【課題】任意の方向に傾斜した開口部を形成可能な基板の製造方法、半導体装置の製造方法、およびこれを適用した半導体装置を備えた電気光学装置を提供すること。

【解決手段】本適用例の素子基板101の製造方法は、素子基板101上に設けられた半導体装置としてのTFT110を覆うと共に第1開口部としての孔104aが設けられた第2絶縁膜としての層間絶縁膜104をマスクとして、素子基板101の面法線101aと交差する一の方向からドライエッチングを第1絶縁膜としてのゲート絶縁膜103に施して、孔104aに連通すると共にTFT110のドレイン電極110dに開口する第2開口部としての孔103aを形成する。

(もっと読む)

半導体装置の製造方法

【課題】配線溝パターンの深さを精密に制御でき、かつ当該配線溝パターンのダメージ形成を抑制できる半導体装置の製造方法を提供する。

【解決手段】拡散防止膜ADF上に、第2の低誘電率膜LOWK2c、第3の低誘電率膜LOWK3c、マスク層となるべき膜がこの順に積層される。マスク層となるべき膜をエッチングし、底面が第3の低誘電率膜LOWK3cの表面により構成される配線溝パターンを形成することにより、マスク層SIO2dが形成される。アッシング処理により第1のレジストマスクが除去される。マスク層の配線溝パターンを用いて、底面が第2の低誘電率膜LOWK2cとなるように、配線溝TRCHが形成される。充填される銅金属CUaの頂面から第3の低誘電率膜LOWK3cまでの層がCMP法により除去される。上記各低誘電率膜はFSGよりも誘電率が低く、第2の低誘電率膜LOWK2cは第3の低誘電率膜LOWK3cよりも誘電率が低い。

(もっと読む)

プラズマエッチング方法

【課題】従来技術ではデュアルダマシン構造Via工程のLow−K膜エッチング後の孔底部のエッチングにおいて、ストッパ膜のエッチングが進行しない課題があった。

【解決手段】本発明はプラズマエッチングするデュアルダマシンプロセスにおいて、デュアルダマシンプロセスのVia加工方法は、Viaパターニングされた上層レジスト膜をマスクとして反射防止膜をエッチングする第1ステップと、上層レジスト膜及び反射防止膜をマスクとして下層レジスト膜をエッチングする第2ステップと、下層レジスト膜をマスクとして前記Low−K膜をエッチングする第3ステップと、ストッパ膜のエッチング前にプラズマ処理を行う第4ステップと、ストッパ膜をエッチングする第5ステップとを有することである。

(もっと読む)

半導体装置の製造方法

【課題】ビアや配線形成のために層間絶縁膜をレジストマスクにより開口エッチングした後、レジストアッシング中に異物が発生する事を抑制する。

【解決手段】半導体基板上に、SiO2膜40、Nを含むストッパ膜50、反射防止膜60、および、レジストパターン70をこの順に積層する積層工程と、レジストパターン70をマスクとして、Fを含むエッチングガスで、反射防止膜60、ストッパ膜50およびSiO2膜40をエッチングし、開口を形成するエッチング工程と、該エッチング工程の後に行われ、酸素ガスおよび不活性ガスを含むガスを(酸素ガスラジカル)/(不活性ガスラジカル)≦5となる条件で用いて、レジストパターン70をアッシングし除去するアッシング工程と、を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】製造コストの増加および歩留まりを低下させることなく、配線抵抗を下げることのできる半導体装置及びその製造方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板100上の絶縁膜104上にマスク材料膜106を形成した後、第1のトレンチ形成用開口と第2のトレンチ形成用開口とを有するマスクパターン109をマスク材料膜106に形成する工程と、マスク材料膜106上に、第1のトレンチ形成用開口を露出する第3のトレンチ形成用開口112を有し、且つ、第2のトレンチ形成用開口部を覆うレジストパターン113を形成する工程と、レジストパターン113及びマスクパターン109を用いて、絶縁膜104内に第1のトレンチ115を形成する工程と、レジストパターン113を除去した後、マスクパターン109を用いて、絶縁膜104内に第2のトレンチを形成する工程とを備えている。

(もっと読む)

ハードマスク材料

【課題】集積回路製造工程のバックエンドプロセス、およびフロントエンドプロセスにおいて利用することができる、高硬度、且つ低応力のハードマスク膜を提供する。

【解決手段】ハードマスク膜は、応力が約−600MPaから600MPaの範囲内であり、硬度は少なくとも約12Gpaである。ハードマスク膜は、PECVD処理チャンバにおいて、高密度化プラズマ後処理を複数回行うことによって、ドープ済または未ドープのシリコンカーバイドの副層を複数成膜することによって得られる。ハードマスク膜は、SixByCz、SixByNz、SixByCzNw、BxCy、およびBxNyから成る群から選択される高硬度のホウ素含有膜を含む。ハードマスク膜は、ゲルマニウム含有率が少なくとも約60原子パーセントと、ゲルマニウム含有率が高いGeNxハードマスク材料を含む。

(もっと読む)

半導体装置の製造方法

【課題】低誘電率層間絶縁膜と多層配線とを備える半導体装置において、低誘電率層間絶縁膜の表面が雰囲気に露出して吸湿するのを防止し、また、金属配線の界面及び低誘電率層間絶縁膜がコンタクトホール内に露出してオーバーエッチングされるのを防止することを目的とする。

【解決手段】水分の透過を防止しつつエッチングストッパとしても機能するエッチング防止膜14を低誘電率層間絶縁膜3の表面に形成し、更に、水分の透過を防止しつつエッチングストッパとしても機能するエッチング防止膜6を形成して、吸湿防止効果を有するエッチング防止膜を二重にする。

(もっと読む)

ドライエッチングガス及びそれを用いたドライエッチング方法

【課題】半導体デバイスの製造プロセスにおいて、シリコン酸化膜、窒化シリコン膜、シリコン含有低誘電率膜等のシリコン含有膜のエッチング速度の低下を防ぎ、レジストや下地のシリコンなどに対して、選択的にエッチングすることができるドライエッチングガス及びそれを用いたエッチング方法を提供する。

【解決手段】CF3CF=CH2を含むドライエッチングガス。CF3CF=CH2の含有率は、流量比5〜100%であることが好ましい。

(もっと読む)

21 - 40 / 379

[ Back to top ]