Fターム[5F033HH32]の内容

半導体集積回路装置の内部配線 (234,551) | 単一配線層の材料,層間接続の上層配線層の材料 (33,767) | 化合物 (5,420) | 窒化物 (4,637)

Fターム[5F033HH32]の下位に属するFターム

Fターム[5F033HH32]に分類される特許

201 - 220 / 1,823

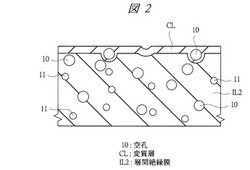

半導体装置の製造方法

【課題】ポーラスLow−k膜の信頼性を向上させる。

【解決手段】プラズマCVD法によって層間絶縁膜IL2を形成する際にCVD装置内に供給するポロジェンの流量を、ポロジェンおよびメチルジエトキシシランの合計の流量の30%以上60%以下とすることで、層間絶縁膜IL2内に形成される空孔10の大きさを小さくし、プロセスダメージによって層間絶縁膜IL2の表面に変質層CLが形成されることを防ぐ。また、水分を含む変質層CLの形成を抑えることで、各配線を構成するバリア膜および主導体膜の酸化を防ぎ、各配線間の耐圧の劣化を防ぐ。これにより、層間絶縁膜IL2に隣接して形成される配線のEM寿命および前記配線の線間TDDB寿命の劣化を防ぐ。

(もっと読む)

半導体装置の製造方法

【課題】ボイドとヒロックの発生の双方を抑制してCu配線を形成する。

【解決手段】半導体基板上の層間絶縁膜に溝パターンを形成する工程(S1)、めっき法によりCu膜を形成する工程(S2,S3)、130〜180℃で第1アニールを行う工程(S4)、CMPにより溝パターン以外の銅膜を除去する工程(S5)、300〜350℃でグレイン成長のための第2アニールを行う工程(S6)とを備える。

(もっと読む)

半導体装置およびその製造方法ならびに半導体ウエハ

【課題】ダイシングブレードの寿命を延ばすことができるとともに、半導体装置のエッジ部へのダメージを低減できる半導体装置を提供する。

【解決手段】機能素子領域2においては、第3層間絶縁膜27表面とパッシベーション膜33との間には、下配線25に接続される上配線29およびキャップメタル層32が形成されている。下配線25はCu以外の配線材料からなり、上配線29はCuからなる。このキャップメタル層32におけるパッシベーション膜33のパッド開口34から露出した部分が第1パッド6である。一方、スクライブ領域3においては、第3層間絶縁膜27表面とパッシベーション膜33との間には、下配線25に接続されるキャップメタル層32が形成されている。このキャップメタル層32におけるパッシベーション膜33のパッド開口44から露出した部分が第2パッド10である。

(もっと読む)

半導体装置及び電子機器

【課題】マスク数を増加させることなく、ブラックマスクを用いずに反射型または透過型の表示装置における画素開口率を改善する。

【解決手段】画素間を遮光する箇所は、画素電極167をソース配線137と一部重なるように配置し、TFTはTFTのチャネル形成領域と重なるゲート配線166によって遮光することによって、高い画素開口率を実現する。

(もっと読む)

半導体素子、及びその形成方法

【課題】 信頼性が向上する半導体素子、及びその形成方法を提供する。

【解決手段】 半導体素子の形成方法は、半導体基板100の上にゲート電極120及びゲート電極120の両側にスペーサー110を形成する段階、ゲート電極120の上にキャッピングパターン170を形成する段階、ゲート電極120の間にメタルコンタクト195を形成する段階を含み、キャッピングパターン170の幅はゲート電極120の幅より大きく形成される。これにより、形成された半導体素子は、メタルコンタクト195とゲート電極120との間での電気的な短絡を效果的に防止することができる。

(もっと読む)

液晶表示装置の製造方法

【課題】配線破断を軽減する構造を有する液晶表示装置の製造方法を提供する。

【解決手段】基板上にゲート配線及び信号配線、ゲート絶縁膜、半導体パターン、データ配線、保護膜、ドレーン電極を露出させる第1接触孔及び信号配線を露出させ、側辺の長さが幅より大きく形成される複数の第2接触孔、第1及び第2接触孔を通じてドレーン電極に連結される画素電極及び信号配線に連結される信号配線補助パッドを形成する液晶表示装置の製造方法であって、信号配線を形成する段階では、信号配線に一対一に対応する複数の信号リードを有する信号伝送用フィルムを含み、信号伝送用フィルムには複数の信号リードのうちの高電圧信号を伝送する第1信号リードと低電圧信号を伝送する第2信号リードとの間にダミーリードが形成され、ダミーリードに対応するダミー配線が基板に形成され、ダミー配線は信号配線より酸化傾向が小さい特性を有する導電物質で形成される。

(もっと読む)

半導体装置およびその製造方法

【課題】SOI基板上に形成されたMOSFETを有する半導体装置の信頼性を向上させる。また、半導体装置の製造工程を簡略化する。

【解決手段】SOI基板SB上に形成された複数のnチャネル型MOSFETQnを有する半導体装置において、BOX膜の下部の支持基板の上面に拡散層であるn+型半導体領域を形成し、n+型半導体領域と電気的に接続され、素子分離領域1を貫くコンタクトプラグCT2を形成することで、支持基板の電位を制御する。SOI基板SBの平面において、各nチャネル型MOSFETQnは第1方向に延在しており、第1方向に複数形成されて隣り合うコンタクトプラグCT2同士の間に配置された構造とする。

(もっと読む)

半導体装置の製造方法

【課題】バリア金属膜の膜厚を薄膜化でき、金属配線やビア内にボイドの無い配線を形成可能な半導体装置の製造方法を提供する。

【解決手段】半導体構造は、相互接続トレンチ又はビア305に薄いバリア金属層307が、トレンチやビアの開口が相互接続トレンチやビアへの銅の配置を疎外する張り出しにより妨害されないように形成される。銅の相互接続配線314を形成するための材料は、銅とマンガンを含んでいる。アニールにより、銅の拡散に対してバリア特性を有する酸化マンガン層315が形成される。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】ビア深さのバラツキを抑制することができる半導体装置の構造およびその製造方法を提供する。

【解決手段】半導体装置の製造方法は、基板上に、SiおよびCを含むキャップ絶縁膜を形成する工程と、キャップ絶縁膜上に、キャップ絶縁膜と比較して、シリコン原子数に対する炭素原子数の組成比が高い、有機シリカ膜を形成する工程と、不活性ガス、Nを含むガス、フッ化炭素ガスおよび酸化剤ガスを含む混合ガスを用いたプラズマ処理により、有機シリカ膜に、異なる開口径を有する2以上の凹部を形成する工程と、を含む。

(もっと読む)

半導体装置およびその製造方法

【課題】パッド電極に荷重または衝撃力が加わっても、周囲の絶縁膜にクラックが発生しにくい構造の半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、平面形状が、略円形、略楕円形、少なくとも1つの内角が90°より大きい略多角形、および、少なくとも1つの角部に面取りや丸みをつけた略多角形、ならびに、これらの少なくとも一部分を含む形状の組合せからなる群から選ばれた平面形状となるような凹部を形成する凹部形成工程と、前記凹部の内面に少なくとも一部を被覆する下敷膜を形成する下敷膜形成工程と、絶縁膜で覆われた前記凹部に導電性の電極材質を埋め込むパッド部形成工程とを含み、前記凹部形成工程は、第1の凹部を形成する工程と、前記第1の凹部の一部分においてさらに深く凹む第2の凹部を形成する工程とを含む。

(もっと読む)

半導体装置及びその製造方法

【課題】抵抗変化素子を半導体装置に組み込む際の必要なフォトマスクを削減しても高密度化が可能な抵抗変化素子を搭載した半導体装置及びその製造方法を提供すること。

【解決手段】配線溝を有する層間絶縁膜14と、配線溝に埋め込まれた配線16aと、配線16aを含む層間絶縁膜14上に形成されるとともに、配線16aに通ずる下穴を有する層間絶縁膜18と、少なくとも下穴が配置された領域における配線16a上に形成されるとともに、抵抗が変化する抵抗変化膜19aと、下穴が配置された領域における抵抗変化膜19a上に形成されたバリアメタル20aと、下穴が配置された領域におけるバリアメタル20a上に形成されたプラグ21aと、を備え、抵抗変化素子5は、第1電極と第2電極との間に抵抗変化膜19aが介在した構成となっており、配線16aは、第1電極を兼ね、バリアメタル20aは、第2電極を兼ねる。

(もっと読む)

カーボンナノチューブの形成方法及びカーボンナノチューブ成膜装置

【課題】被処理体上のビアホールや配線用溝等の開口部に高密度にカーボンナノチューブ膜を埋め込むことができるカーボンナノチューブの形成方法を提供する。

【解決手段】表面に1又は複数の開口部を有し、当該開口部底面に触媒金属層が形成された被処理体を準備し(STEP1)、触媒金属層に酸素プラズマ処理を施し(STEP2)、酸素プラズマ処理後の触媒金属層に水素含有プラズマ処理を施して、触媒金属層の表面を活性化し(STEP3)、その後、触媒金属層の上にプラズマCVDによりカーボンナノチューブを成長させて、被処理体の開口部内をカーボンナノチューブで充填する(STEP5)。

(もっと読む)

半導体装置の製造方法

【課題】有機シロキサン系絶縁膜を用いて電気的特性に優れた半導体装置を製造する方法を提供する。

【解決手段】下層配線の上にこの順で形成された第1〜第3の絶縁膜をドライエッチングして該下層配線に至る開口部を形成し、該開口部の内面と該第3の絶縁膜の上にバリアメタル膜を形成し、該バリアメタル膜の上に該開口部を埋める導電層を形成し、該第3の絶縁膜上の該導電層と該バリアメタル膜、及び該第2、第3の絶縁膜の一部を除去し該下層配線に電気的に接続する上層配線を形成し、露出した該第2の絶縁膜と該導電層の表面を還元性プラズマ処理し、

該第2の絶縁膜は下記式で表されるアルキルアルコキシシランと非酸化性ガスとを用い、500Pa以下でプラズマCVD法により形成する

RwSixOy(OR´)z

R及びR´はCH3、wxzは正の整数、yは0または正の整数、(w/x)=2である。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体基板の主面上に素子形成領域を取り囲むように形成されたスリットを有する半導体装置の信頼性を向上させることのできる技術を提供する。

【解決手段】ボンディングパッドBPに用いる第6層目の配線M6の上面を露出するように形成された開口部31の側面と、ガードリングGRの周りを囲み、その底部がバリア絶縁膜22を突き抜けないように第1パッシベーション膜30、接着用絶縁膜29、および層間絶縁膜23に形成されたスリットSLの内壁(側面と底面)とを第2パッシベーション膜32により覆う。

(もっと読む)

制御された気孔を形成するための材料及び方法

【課題】基材の内部に空隙を形成するための方法を提供する。

【解決手段】基材を用意する工程;少なくとも1つの犠牲材料前駆体の堆積によって犠牲材料を堆積する工程;複合層を堆積する工程;該複合層中のポロゲン材料を除去して多孔質層を形成する工程;及び積層基材を除去媒体と接触させて前記犠牲材料を実質的に除去し、前記基材の内部に空隙を与える工程を含み、前記少なくとも1つの犠牲材料前駆体が、有機ポロゲン、シリコン、極性溶媒に可溶な金属酸化物、及びそれらの混合物からなる群より選択される方法が提供される。

(もっと読む)

空隙組込みの構造体及び方法

【課題】 空隙を組み込んだ構造体及びその形成方法を提供する。

【解決手段】 VLSI及びULSI用の空隙含有金属・絶縁体相互接続構造体を、光パターン化可能低k材料を用いて作成する方法、及び形成した空隙含有金属・絶縁体相互接続構造体を開示する。より具体的には、本明細書で説明する方法は、内部に種々異なる深さの空隙がフォトリソグラフィにより画定された光パターン化可能低k材料の内部に構築される相互接続構造体を提供する。本発明の方法においては、空隙を形成するのにエッチ・ステップは必要としない。光パターン化可能低k材料内部の空隙を形成するのに、エッチ・ステップを必要としないで、本発明において開示する方法は、高信頼性の相互接続構造体を提供する。

(もっと読む)

低k誘電体と導電材料との接着改善

【課題】銅ダマシン配線上への誘電体層の形成において、導電材料と誘電体層間の密着性を向上する半導体装置の製造方法を提供する。

【解決手段】オルガノシロキサンからなる第2誘電体層118に、TaNからなる金属バリア層124とCuからなる導電性金属特徴部126を形成する。平坦化後アンモニアプラズマ処理還元により表面の酸化物を除去する。連続して真空を破壊せずに、トリメチルシランからなる有機ケイ素化合物を導入し、プラズマプロセスによりSiCN膜130を形成し、さらに連続してSiC膜132を堆積する。酸化物の除去から誘電体層の形成までインサイチュで行うことが可能である。

(もっと読む)

半導体集積回路装置およびその製造方法

【課題】多層配線構造を使って、キャパシタンスが大きく、かつキャパシタンス値が安定なキャパシタ素子を半導体基板上に集積化する。

【解決手段】多層配線構造18は、少なくとも第1層目の層間絶縁膜16と、第1層目の層間絶縁膜中に埋設された第1配線層と、を含み、第1配線層は、第1の電源に接続され前記第1の層間絶縁膜中に埋設された第1の配線パタ―ン15C1と、第2の電源に接続され前記第1の層間絶縁膜中に埋設された第2の配線パタ―ン15C2と、を含み、第1の配線パタ―ンと前記第2の配線パタ―ンとは容量結合して第1のキャパシタを形成し、第1の配線パタ―ンは積層配線パタ―ン13C上に形成されて、前記第4の電極パターン13Gと容量結合して第2のキャパシタを形成し、第4の電極パターンは第2の配線パタ―ンに電気的に接続されている。

(もっと読む)

半導体デバイス及びマスク設計方法

【課題】アクティブフィーチャの容量カップリングを低減する。

【解決手段】本発明は、研磨ダミーフィーチャパターンの無差別な配置ではなく、研磨ダミーフィーチャパターンの選択的な配置を使用する。トポグラフィ変化の低周波数(数百ミクロン以上)及び高周波数(10ミクロン以下)の両方が検討された。研磨ダミーフィーチャパターンは半導体デバイス及び半導体デバイスの作製に使用される研磨条件に特に適合されている。集積回路をデザインする場合にはアクティブフィーチャの研磨効果が予測可能である。研磨ダミーフィーチャパターンが例図とに配置された後、局部的な(デバイスの全てではなく一部)レベルにおいて、及びさらに広域的なレベル(全デバイス、デバイスとは、レチクルフィールド、或いはさらにはウェハ全体に対応する)平坦性が検査される。

(もっと読む)

半導体集積回路装置および半導体集積回路装置の製造方法

【課題】TSVを形成した後の工程においては、Cuの拡散防止膜である絶縁膜形成後に、当該絶縁膜に割れが発生し、その後のエッチングやアッシングなどのパターン加工を行う工程において、露出したCuが変色する問題が発生する場合がある。これは、拡散防止膜の成膜工程における熱履歴によりCuが体積膨張したことが問題の要因と考えられる。このような、膜割れが発生した場合には、Cu拡散防止膜の機能破壊、TSV上部のCuの酸化による上部配線との導通不良等の種々の問題を誘発する。

【解決手段】本願の一つの発明は、貫通電極を有する半導体集積回路装置において、プリメタル配線層形成よりも後に貫通ビアを形成する場合において、貫通電極の上端に当たる層間絶縁膜の界面に、メタル拡散防止絶縁膜として、窒化シリコン系絶縁膜を使用し、それ以外の層間絶縁膜の界面に、メタル拡散防止絶縁膜として、炭化シリコン系の絶縁膜を使用するものである。

(もっと読む)

201 - 220 / 1,823

[ Back to top ]