Fターム[5F033HH32]の内容

半導体集積回路装置の内部配線 (234,551) | 単一配線層の材料,層間接続の上層配線層の材料 (33,767) | 化合物 (5,420) | 窒化物 (4,637)

Fターム[5F033HH32]の下位に属するFターム

Fターム[5F033HH32]に分類される特許

121 - 140 / 1,823

半導体装置および半導体装置の製造方法

【課題】本発明は、銅合金配線とビアとの接続面に、窒素を含むバリヤメタル膜が形成されている構造を有する半導体装置であって、銅合金配線とビアとの間における電気抵抗の上昇を抑制することができる半導体装置等を提供する。

【解決手段】本発明に係る半導体装置では、第一の層間絶縁膜内に配設されており、主成分であるCuにAlを添加した第一の銅合金配線と、第一の層間絶縁膜上に形成される第二の層間絶縁膜と、第二の層間絶縁膜内に配設されており、主成分であるCuにAlを添加した第二の銅合金配線とを、備えている。そして、第二の銅合金配線のAlの濃度は、第一の銅合金配線の前記Alの濃度未満である。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の性能と信頼性を向上させる。

【解決手段】nチャネル型MISFETQn1,Qn2を覆うように半導体基板1上に引張応力膜としての窒化シリコン膜5を形成する。窒化シリコン膜5は窒化シリコン膜5a,5b,5cの積層膜である。窒化シリコン膜5a,5bの膜厚の合計は、サイドウォールスペーサSW1とサイドウォールスペーサSW2との間の間隔の半分よりも小さく、窒化シリコン膜5a,5bは、成膜後に紫外線照射処理を行って引張応力を増大させる。窒化シリコン膜5a,5b,5cの膜厚の合計は、サイドウォールスペーサSW1とサイドウォールスペーサSW2との間の間隔の半分以上であり、窒化シリコン膜5cに対しては紫外線照射処理を行わない。

(もっと読む)

金属層の結晶粒径及び粒径分布評価方法並びにそれを用いた半導体集積回路装置の製造方法

【課題】非破壊かつオンラインで金属層の結晶粒径及び粒径分布を評価する方法を実現する。

【解決手段】結晶組織を有し特定の面方位においてX線に対して回折ピークを持つ金属層にX線を照射して得られる回折ピークを入手するステップA、回折ピークに基づいて面積平均コラム長及び体積平均コラム長を求めるステップB、面積平均コラム長及び体積平均コラム長から結晶粒径の対数正規分布を求めるステップCを具備する。

(もっと読む)

半導体装置

【課題】銅ヒューズに起因する故障または特性悪化を抑制または防止できる半導体装置を提供する。

【解決手段】半導体装置は、半導体基板1と、銅ヒューズ4と、半導体基板1と銅ヒューズ4との間に配置された銅膜からなるシール膜7,8と、銅ヒューズ4よりも上の層に形成された銅以外の金属材料膜からなり、銅ヒューズ4の両端にそれぞれに接続された最上層配線501,502と、シール膜7,8に結合され、銅ヒューズ4の周囲を取り囲む筒状に形成された銅シールリング6とを含む。

(もっと読む)

半導体記憶装置

【課題】さらなるDRAMの大記憶容量化を図る。

【解決手段】半導体記憶装置が、単結晶半導体材料を含む基板の一部を有する駆動回路と、当該駆動回路上に設けられる多層配線層と、当該多層配線層上に設けられるメモリセルアレイ層とを有する。すなわち、当該半導体記憶装置においては、駆動回路と、メモリセルアレイとが重畳して設けられる。したがって、単結晶半導体材料を含む基板に駆動回路及びメモリセルアレイを同一平面に設ける場合と比較して、当該半導体記憶装置の集積度を高めることが可能となる。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】論理回路の動作特性に優れた半導体装置を提供する。

【解決手段】半導体装置は、半導体基板1と、多層配線層と、第1能動素子3a、容量素子19および周辺回路を有する記憶回路200と、第2能動素子3bを有する論理回路100と、記憶回路領域200に形成されており、能動素子3aと容量素子19とを電気的に接続する容量コンタクト13cと、論理回路領域100に形成されており、能動素子3bと第1配線8aとを電気的に接続する接続コンタクト13aと、を備え、第1配線8aは、容量素子19が埋め込まれた配線層のうち最下層の配線層の層間絶縁膜7aに位置しており、接続コンタクト13aは、容量コンタクト13cと同一層に設けられており、第1配線8aと接続コンタクト13aは、デュアルダマシン構造を有している。

(もっと読む)

半導体装置

【課題】封止される被対象物に段差部を備えているが、封止部を設けた際に該段差部に起因したボイドの発生が抑制され、ひいては優れた耐食性を備える半導体装置と、その製造方法を提供する。

【解決手段】本発明に係る半導体装置1は、導電性を有する剛体からなる基板2と、該基板の少なくとも一方の面に絶縁部3を介して配された導電部5と、該絶縁部及び該導電部を覆うように配された感光性樹脂からなるフィルム6と、を備えている。前記基板2は、一方の面に開口する凹部及び/又は貫通孔2aを備え、該凹部及び/又は該貫通孔はその内部が略全域にわたって、前記フィルム6により充填されている形態をなす。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】容量素子の容量の増大が実現される半導体装置を提供する。

【解決手段】半導体装置は、基板(半導体基板1)と、半導体基板1上に形成されており、配線および絶縁層により構成された配線層が複数積層された多層配線層と、平面視において、半導体基板1内の記憶回路領域に形成されており、多層配線層内に設けられた凹部40内に埋め込まれた少なくとも1以上の容量素子19および周辺回路を有する記憶回路200と、平面視において、半導体基板1内の記憶回路領域とは異なる領域である論理回路領域に形成された論理回路100と、当該凹部40内において、下部電極14、容量絶縁膜15、及び上部電極16から構成される前記容量素子19上に積層している上部接続配線18と、容量素子19が埋め込まれている配線層のうち最上層に設けられた論理回路100を構成する配線8bの上面に接するように設けられたキャップ層6cと、を備え、上部接続配線18の上面30とキャップ膜6cの上面34とが、同一面を構成している。

(もっと読む)

半導体装置の製造方法

【課題】配線形成時に配線形成用溝の間口を閉塞させないで配線形成用溝内に連続したCu膜を形成できる半導体装置の製造方法を提供する。

【解決手段】配線形成用溝形成工程では、層間絶縁膜10に配線形成用溝31を形成する。バリアメタル膜形成工程では、配線形成用溝31が形成された層間絶縁膜10上の全面にバリアメタル膜14を形成する。Cu膜形成工程では、配線形成用溝31間の層間絶縁膜10上の膜厚に比して配線形成用溝31内の底部の方が厚くなるように、バリアメタル膜14上にCu膜15を形成する。リフロー工程では、バリアメタル膜14上のCu膜15をリフローさせ、配線形成用溝31内に埋め込む。そして、除去工程では、少なくとも配線形成用溝31間の層間絶縁膜10上のバリアメタル膜14をCMP法によって除去する。

(もっと読む)

半導体装置

【課題】隣接するビット線同士の短絡が抑制されており、かつ層間絶縁膜が平坦に研磨された半導体装置を提供する。

【解決手段】磁気抵抗素子MRDが複数配置されたメモリセル領域と、平面視においてメモリセル領域の周囲に配置された周辺回路領域とを備える。磁気抵抗素子MRDは、磁化固定層と磁化自由層とトンネル絶縁層とを含んでいる。磁気抵抗素子MRDの上方には、主表面に沿った方向に向けて延びる複数の第1の配線BLを有している。上記周辺回路領域には、第1の配線BLと同一レイヤにより構成される第2の配線BL2と平面視において重なるように、磁化自由層と同一材質の層、トンネル絶縁層と同一材質の層および磁化固定層と同一材質の層が積層された積層構造DMMが配置されている。積層構造DMMは、周辺回路領域にて平面視において隣接する1対の第2の配線BL2の両方と重ならない。

(もっと読む)

半導体装置の製造方法及び製造装置

【課題】半導体装置のエッチングを精度良く行い、再生率を低減させる

【解決手段】基板にトランジスタを形成し、トランジスタを覆うように第1層間絶縁膜22を形成する。さらに、第1層間絶縁膜22の上方に形成したレジスト膜27を用いて第1層間絶縁膜22をエッチングし、トランジスタのソース/ドレイン領域に到達するコンタクトホール31を形成する。この際、レジスト膜27の開口部27Aの半径rと、開口部27Aが設計位置からずれている位置ずれ量ΔXとを測定し、コンタクトホール31に必要な半径Rxと、コンタクトホール31を形成可能な限界距離Sとから、r+ΔX−S<ES<r−Rxを満たす半径差ESを決定し、半径差ESからエッチング条件を決定する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】実効誘電率が低く、かつ信頼性の高いバリア絶縁膜を有する半導体装置を提供することができる。

【解決手段】半導体装置100は、層間絶縁膜10と、層間絶縁膜10中に設けられた配線20と、層間絶縁膜10上および配線20上に設けられたSiN膜30と、を備え、FTIRによって測定したSiN膜30のSi−N結合のピーク位置が845cm−1以上860cm−1以下である。これにより、配線金属の拡散を防ぐためのバリア絶縁膜である窒化シリコン膜において、リーク電流を抑制することができる

(もっと読む)

組成物

【課題】低い誘電率及び改良された機械的性質、熱的安定性及び化学的耐性を有する多孔質有機シリカガラス膜を提供する。

【解決手段】式SivOwCxHyFz(ここで、v+w+x+y+z=100%、vは10〜35原子%、wは10〜65原子%、xは5〜30原子%、yは10〜50原子%、及びzは0〜15原子%)で表わされる多孔質有機シリカガラス膜を製造する。オルガノシラン及びオルガノシロキサンからなる群より選ばれる前駆体並びにポロゲンを含むガス状試薬を真空チャンバに導入し、ガス状試薬にエネルギーを加え、ガス状試薬の反応を生じさせて基体上に予備的な膜を堆積させる。その予備的な膜は細孔を持ち、誘電率が2.6未満である多孔質膜を得るために、実質的にすべてのポロゲンを除去される。

(もっと読む)

半導体装置

【課題】基板の大型化に対応し得る金属配線を作製する。

【解決手段】絶縁表面上に少なくとも一層の導電膜12,13を形成し、前記導電膜12,13上にレジストパターンを形成し、前記レジストパターンを有する導電膜にエッチングを行い、バイアス電力密度、ICP電力密度、下部電極の温度、圧力、エッチングガスの総流量、エッチングガスにおける酸素または塩素の割合に応じてテーパー角αが制御された金属配線を形成する。このようにして形成された金属配線は、幅や長さのばらつきが低減されており、基板10の大型化にも十分対応し得る。

(もっと読む)

側壁イメージ転写からパターンを作る改善された方法

【課題】実施の容易な、側壁イメージ転写により部分的に定義されるパターンを生成する方法を提供する。

【解決手段】基板1には、第1の材料2の層と、第1のエッチングマスク4と、カバリング層3と、第2のエッチングマスクとが設けられている。カバリング層3は、覆われた主領域と、覆われていない副領域とを有する。カバリング層3の副領域は、第2のエッチングマスクを介して部分的にエッチングされ、突出パターンが形成される。第3のエッチングマスクを定義する突出パターンの周囲に、横スペーサが形成される。第2のエッチングマスクは除去される。カバリング層3は、第3のエッチングマスクを用いてエッチングされ、カバリング層3における突出パターンが形成され、第1のエッチングマスク4および第1の材料2が露出される。第1の材料2の層は、エッチングされ、第1の材料2から作られるパターンが形成される。

(もっと読む)

半導体装置及びその製造方法

【課題】同層配線間の容量及び、上下層配線間の容量を低減し、配線間領域の実効誘電率を低減できる半導体装置及びその製造方法を提供する。

【解決手段】半導体装置は、基板上に形成された第1の絶縁膜101と、第1の絶縁膜101の上部に埋め込まれた複数の第1の配線120と、第1の絶縁膜101上及び複数の第1の配線120上に形成され、開口部を有するライナー絶縁膜104と、ライナー絶縁膜104上に形成された第2の絶縁膜107と、第2の絶縁膜107の上部に埋め込まれた複数の第2の配線110とを備える。第1の絶縁膜101における、第1の配線120の間であって、ライナー絶縁膜104の開口部と重なる部分には、絶縁膜によって塞がれたエアギャップ108が形成されており、第2の絶縁膜107の比誘電率は2.5以下である。

(もっと読む)

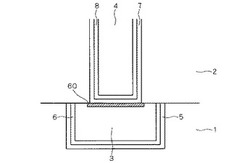

三次元積層構造を持つ半導体装置の製造方法

【課題】 三次元積層構造を持つ半導体装置において、積層された半導体回路層間の積層方向の電気的接続を、埋込配線を使用して容易に実現する半導体装置の製造方法を提供する。

【解決手段】 第1半導体回路層1aの半導体基板11の表面に、絶縁膜14で内壁面が覆われたトレンチ13を形成し、トレンチ13の内部に導電性材料を充填して導電性プラグ15を形成する。次に、トレンチ13とは重ならないように所望の半導体素子を基板11の表面または内部に形成し、その上に層間絶縁膜19を介して多層配線構造30を形成してから、多層配線構造30の表面にプラグ15に電気的に接続されたバンプ電極37を形成する。そして、電極37を用いて基板11を支持基板40に固定してから基板11をその裏面側から選択的に除去し、絶縁膜14を基板11の裏面側に露出させる。基板11の裏面側に露出せしめられた絶縁膜14を選択的に除去してプラグ15を露出させ、その端に電極42を形成する。

(もっと読む)

コア付きインダクタ素子およびその製造方法

【課題】半導体基板上に形成するインダクタのインダクタンスを大きくすること。

【解決手段】半導体基板上に形成された少なくとも1層からなるコイル配線のコイル中央孔に別基板に形成されたコアを挿入する。コアをコイル中央孔に固定した後、別基板は分離する。コアは別基板に接合材を介してコア材(磁性体)の薄板を付着させて、パターニングする。半導体基板上に形成されたコイル中央孔は流動性接着剤が入っていて、コアを挿入した後に流動性接着剤が硬化してコアが固定される。コアが固定された後に接合剤の接着力を低下させて別基板を分離する。コア材はバルクと同じ高透磁率を有するので、非常に大きなインダクタンスを持つインダクタを形成できる。

(もっと読む)

半導体装置

【課題】工程数の増大を抑制しつつ、チップ上に形成された再配線または突出電極の信頼性を向上させる。

【解決手段】配線2bおよびパッド電極2aが形成された半導体基板と、半導体基板上に形成された応力緩和層4と、応力緩和層4上に合金シード膜5を形成した後、応力緩和層4と合金シード膜5とを熱処理にて反応させることで、応力緩和層4と合金シード膜5との間に反応性バリア絶縁膜6を形成する。再配線8または突出電極は合金シード膜5上に形成する。

(もっと読む)

半導体装置の製造方法

【課題】 製造工程の増加を招くことなく、タングステン配線の低抵抗化できる半導体装置の製造方法を提供する。

【解決手段】 本発明は、基板表面に、微細形状を有する絶縁層を形成した後、この微細形状を含む絶縁層表面に、Ta膜またはTaN膜からなる下地層を形成する工程と、下地層の表面に、タングステンから膜なる配線層を形成する工程とを含む。

(もっと読む)

121 - 140 / 1,823

[ Back to top ]