Fターム[5F033HH32]の内容

半導体集積回路装置の内部配線 (234,551) | 単一配線層の材料,層間接続の上層配線層の材料 (33,767) | 化合物 (5,420) | 窒化物 (4,637)

Fターム[5F033HH32]の下位に属するFターム

Fターム[5F033HH32]に分類される特許

81 - 100 / 1,823

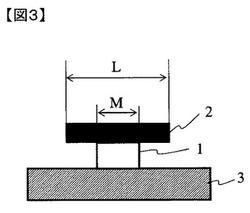

パターン状金属膜の製造方法

【課題】レジスト膜の厚みを比較的小さくしてかつオーバーエッチングするパターン状金属膜の製造方法において、所望パターンの金属膜を安定的に製造することができる製造方法を提供する。

【解決手段】金属膜上にパターン状のレジスト膜を形成する工程(A)、前記金属膜をエッチングする工程(B)を順次有するパターン状金属膜の製造方法であって、前記レジスト膜は厚みが5μm以下でかつ鉛筆硬度がB以下であり、前記工程(B)において前記レジスト膜の線幅100%に対してパターン状金属膜の線幅が80%以下となるようにオーバーエッチングする、パターン状金属膜の製造方法。

(もっと読む)

ボンディングパッドを有する半導体デバイス及びその製造方法

【課題】 ボンディングパッドを有する半導体デバイス及びその製造方法を提供する。

【解決手段】 表面側及び裏面側を有するデバイス基板、前記デバイス基板の前記表面側に配置され、n層数の金属層を有する相互接続構造、及び前記相互接続構造を通過して延伸し、前記n層数の金属層の前記第n番目の金属層に直接接触するボンディングパッドを含む半導体デバイス。半導体デバイスは、前記デバイス基板の前記裏面側に配置された遮蔽構造、及び、前記デバイス基板の前記表面側に配置され、前記デバイス基板の前記裏面側から前記放射線検出領域に向けて投射された放射線を検出することができる放射線検出領域をさらに備える。

(もっと読む)

半導体装置

【課題】 より信頼性の高い接合界面を有する半導体装置を提供する。

【解決手段】 半導体装置100を、第1半導体部と、第2半導体部とを備える構成とする。第1半導体部には、接合界面側の表面に形成されかつ第1の方向に延在する第1電極16を設ける。そして、第2半導体部には、接合界面で第1電極16と接合されかつ第1の方向と交差する第2の方向に延在する第2電極26を設ける。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】基板を実装する際の温度負荷によって絶縁層と下地金属層の側面との接点領域に加わる応力を緩和させ、応力に起因した絶縁層のクラックの発生を抑えるように構成された半導体装置を提供する。

【解決手段】半導体基板101の一面101aに、絶縁層102、下地金属層103、金属端子が設けられるためのランド部104を順に積層してなる半導体装置109であって、ランド部104は、絶縁層102と対向する面の中央部において、下地金属層103と接合する接合領域と、絶縁層102と対向する面において、接合領域を除いた非接合領域と、を有し、下地金属層103は、ランド部104側から絶縁層102側にかけて外向きに傾斜した側面を有していること、を特徴とする半導体装置109。

(もっと読む)

半導体装置およびその製造方法

【課題】ダイシング工程で発生する膜剥離やクラックがチップ内部に伝播するのを防ぐ。

【解決手段】半導体装置100は、基板102と、ビア層130および配線層132が形成される素子形成領域であるチップ内部202と、平面視においてチップ内部202を囲むようにチップ内部202の外周に形成されたシールリング部204と、を含む。シールリング部204において、シールリングは、平面視においてチップ内部202を囲むように形成された貫通孔122aを有する第1のメタル層122と、第1のメタル層122上に第1のメタル層122に接して形成された第2のメタル層124と、を含み、第1のメタル層122の貫通孔122aの下部分には絶縁性材料(層間絶縁膜106)が形成され、貫通孔122aの上部分には第2のメタル層124を構成するメタル材料がくい込んで形成される。

(もっと読む)

半導体装置、半導体装置の製造方法、回路基板および電子機器

【課題】電極パッドと貫通電極との接続面積を確保しつつ、下地膜が確実に形成される半導体装置、半導体装置の製造方法、回路基板および電子機器を提供する。

【解決手段】半導体基板10の能動面10a側に設けられた第一絶縁膜22と、第一絶縁膜22上に設けられた電極パッド12と、電極パッド12の形成位置に対応し、半導体基板10および第一絶縁膜22に形成された貫通孔H3と、貫通孔H3の少なくとも側面に設けられた第二絶縁膜23と、第二絶縁膜23と電極パッド12とを覆うように設けられた下地膜24と、下地膜24の内側で、貫通孔H3に埋め込まれた導電材料からなる貫通電極30と、を具備した半導体装置100において、貫通孔H3の側面と電極パッド12の裏面との角部23aに、第二絶縁膜23がフィレット状に形成されている。

(もっと読む)

半導体装置の製造方法

【課題】貫通電極の形成過程で、余分な酸化膜を確実に除去する。

【解決手段】貫通電極を形成するビアホール25の内面に酸化膜26を形成した後、Cu膜28を埋め込む。第1層間絶縁膜22の上に形成された余分なCu膜28をCMP法による研磨で除去するときに、酸化膜26も研磨されて膜厚が薄くなる。膜厚が薄くなった酸化膜26Bをハードマスクとして第1層間絶縁膜14に配線溝を形成する。このとき、酸化膜26Bの膜厚が薄くなる。配線溝に導電材を埋め込んだ後、余分な導電材を研磨によって除去する。このとき、残りの酸化膜26Bが全て研磨により除去される。

(もっと読む)

半導体装置の製造方法

【課題】 低k膜と金属マスクとの間の界面に歪みを引き起こすことなく、高い精度の望ましいパターンを得ること。

【解決手段】 半導体装置を製造する方法では、金属マスクと絶縁マスクをと備える多層ハードマスクを用いて形成される配線層を含む半導体装置が形成される。第1パターンにアラインされた第2開口パターンを形成するために、第1ステップで多層ハードマスクが使用された後、金属マスクが除去され、絶縁マスクが、第2のステップで絶縁層中に第1のパターン構造を形成するために使用される。

(もっと読む)

無電解薄膜析出法により平坦化銅相互接続層を形成する方法および装置

【課題】基板に定形された形態部の内部に、表面が平坦化された導電性材料を形成する方法を提供する。

【解決手段】平坦化表面を形成する方法であって、狭小形態部と幅広形態部が形成された基板上に、第1のプロセスでは電気めっき法により狭小形態部および幅広形態部の少なくとも一部を充填し、第1の層を形成し、第2のプロセスでは無電解めっき法により幅広形態部のに対応する第1の層中の孔および第1の層上に第2の層を充填形成し、表面が平坦な上層部110を形成する。

(もっと読む)

複数の開口部を備える基板上への層の蒸着方法

【課題】多孔性低誘電率絶縁膜のトレンチおよびビア内にカバレージ良くライニング層を形成する半導体装置の製造方法を提供する。

【解決手段】第1パルス期間に供給される第1反応物と、第2パルス期間に供給される第2反応物とを利用する原子層堆積(ALD)プロセスにより成膜する。まずシーリング層を低コンフォマリティーを有する条件で成膜し、ポアをブロックする。この後、接着層を高いコンフォマリティーを有する条件で成膜する。

(もっと読む)

Cu配線の形成方法および成膜システム

【課題】Cuめっきを用いることなくPVDのみでトレンチまたはホールCuを埋め込んでCu配線を形成すること。

【解決手段】ウエハWに形成されたトレンチ203を有する層間絶縁膜202の全面にバリア膜204を形成する工程と、バリア膜204の上にRu膜205を形成する工程と、Ru膜205の上にPVDによりCuがマイグレーションする条件でトレンチ203内に第1のCu膜206を形成する工程と、第1のCu膜206の上に、第1のCu膜206よりも大きな成膜速度でPVDにより第2のCu膜207を形成する工程と、CMPにより全面を研磨する工程とを有する。

(もっと読む)

プラズマ処理方法およびプラズマ処理装置

【課題】段差を有する膜構造を高精度にエッチングするプラズマ処理装置またはドライエッチング方法を提供する。

【解決手段】真空容器107と、この真空容器内部の処理室内に配置されその上面にエッチング対象のウェハ112が載せられる下部電極113と、下部電極113にバイアス電位を形成するための高周波電力を供給するバイアス印加装置118,120と、前記処理室内に反応性ガスを導入するガス供給手段111と、前記処理室内にプラズマを生成するための電界を供給する電界供給手段101〜103と、前記高周波電力により前記ウェハ112に入射する前記プラズマ中のイオンのエネルギーの分布を調節する調節装置127とを備えたプラズマ処理装置。

(もっと読む)

配線構造、表示装置、および半導体装置

【課題】Cu合金層と半導体層との間に通常設けられるバリアメタル層を省略しても優れた低接触抵抗を発揮し得、さらに半導体層との密着性に優れており、且つ電気抵抗率が低減された配線構造を提供すること。

【解決手段】本発明の配線構造は、基板の上に、基板側から順に、半導体層と、Cu合金層とを備えた配線構造であって、前記Cu合金層は、基板側から順に、合金成分としてMnと、X(Xは、Ag、Au、C、W、Ca、Mg、Al、SnおよびNiよりなる群から選択される少なくとも一種)を含有する第一層と、純Cu、またはCuを主成分とするCu合金であって前記第一層よりも電気抵抗率の低いCu合金からなる第二層、とを含む積層構造である。

(もっと読む)

半導体素子

【課題】不良品の発生を容易に防止出来て歩留まりの向上と製造条件の確認の容易な半導体素子を実現する。

【解決手段】半導体素子本体の外表面を覆って設けられた絶縁膜と、この絶縁膜に設けられ前記半導体素子本体に一端側が接する外部接続用端子と、前記絶縁膜に穿設され一端側が前記外部接続用端子に接する配線取出し孔と、を具備する半導体素子において、前記外部接続用端子の前記配線取出し孔に接する面全体に一面が接し他面が前記絶縁膜に接して設けられ前記外部接続用端子の色と前記絶縁膜の色と異なる色を有し前記配線取出し孔の穿設時に除去されることにより前記配線取出し孔の穿設完了を識別する識別膜とを具備したことを特徴とする半導体素子である。

(もっと読む)

半導体装置の製造方法及びめっき装置

【課題】めっき膜の成膜が進んでも、被めっき面の表面電位と所望する表面電位との誤差が生じることを抑制できる半導体装置の製造方法を提供する。

【解決手段】この半導体装置の製造方法は、半導体基板1に形成されたシード膜20を、めっき液32に接触させる工程と、シード膜20にカソード電極54を接続し、シード膜20とめっき液32中のアノード電極40との間で電流を流すことにより、シード膜20上にめっき膜22を形成する工程と、を備え、めっき膜22を形成する工程において、めっき液20中に挿入された参照電極34とカソード電極54との間の電位差、またはカソード電極54とアノード電極40の電位差を、時間の経過と共に徐々に下げる工程を有する。

(もっと読む)

液晶表示装置及び液晶表示装置の作製方法

【課題】新規な電極構造を有する、横電界方式の液晶表示装置とその作製方法の提案。

【解決手段】絶縁表面を有する第1基板と、絶縁表面上の第1導電膜及び第2導電膜と、第1導電膜上の第1絶縁膜と、第2導電膜上の第2絶縁膜と、第1基板と対峙する第2基板と、第1基板と第2基板の間に位置する液晶層と、を有し、第1導電膜の一部は第1絶縁膜の側部にも位置し、なおかつ、第2導電膜の一部は第2絶縁膜の側部にも位置し、液晶層は、ブルー相を示す液晶を含んでいる液晶表示装置。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】デュアルダマシン法を用いて層間絶縁膜内にCu配線を形成する際、硬度が低い層間絶縁膜および硬度が高い層間絶縁膜のそれぞれに形成されたビアホール内に配線材料を良好に埋め込むことができるようにする。

【解決手段】第2層間絶縁膜17には、配線溝30aとビアホール28aとが形成されている。また、ビアホール28aの開口部には、第2層間絶縁膜17を斜め下方に後退(リセス)させることによって、テーパ状の断面形状を有するリセス部31が形成されている。これにより、ビアホール28aの開口部の直径は、開口部よりも下方の領域の直径に比べて大きくなり、ビアホール28aの直径が微細な場合であっても、ビアホール28aの内部に配線材料を良好に埋め込むことができる。

(もっと読む)

半導体装置、電子デバイス、及び、半導体装置の製造方法

【課題】 より信頼性の高いCu−Cu接合界面を有する半導体装置及びその製造方法を提供する。

【解決手段】 半導体装置1を、第1の配線18を含む第1半導体部10と、第1半導体部10と貼り合わせて設けられ、第1の配線18と電気的に接合された第2の配線28を含む第2半導体部20とを備える構成とする。さらに、半導体装置1は、酸素に対して水素よりも反応し易い金属材料と酸素とが反応して生成された金属酸化物17bを備える。そして、この金属酸化物17bを、第1の配線18及び第2の配線28の接合界面Sj、並びに、第1の配線18及び第2の配線28の少なくとも一方の内部を含む領域に拡散させた構成とする。

(もっと読む)

半導体装置

【課題】LSIチップの製造コストを低減することが可能な半導体装置を提供する。

【解決手段】半導体装置は、半導体基板と、前記半導体基板に形成され、第1の電源配線を含む第1の電源配線層を備える複数のLSI領域と、前記半導体基板に形成された第1の電源端子と、前記LSI領域の間のダイシングライン領域に、前記LSI領域と前記ダイシングライン領域とを区画するダイシングラインに沿って形成され、前記第1の電源配線と前記第1の電源端子とを電気的に接続する第2の電源配線を含む第2の電源配線層と、を備える。少なくとも前記LSI領域において、前記第1の電源配線と前記第2の電源配線との境界にバリアメタル膜が形成されている。

(もっと読む)

半導体装置の製造方法

【課題】 金属部材の表面に、再現性よくバリア膜を形成する技術が望まれている。

【解決手段】 基板の上に、下部バリア膜を形成する。下部バリア膜の上にシード膜を形成する。シード膜の一部の領域上に、導電部材を形成する。導電部材をエッチングマスクとして、シード膜をエッチングし、導電部材の形成されていない領域において、下部バリア膜を露出させる。下部バリア膜の表面には堆積しない条件で、導電部材の表面に選択的に上部バリア膜を成長させる。上部バリア膜をエッチングマスクとして、下部バリア膜をエッチングする。

(もっと読む)

81 - 100 / 1,823

[ Back to top ]