Fターム[5F033JJ09]の内容

半導体集積回路装置の内部配線 (234,551) | 層間接続のコンタクト層の材料 (22,060) | 金属及びその合金(シリサイドを除く) (14,566) | Al (1,778) | Al合金 (426)

Fターム[5F033JJ09]の下位に属するFターム

Si,Cu以外を含むもの (69)

Fターム[5F033JJ09]に分類される特許

61 - 80 / 357

半導体装置およびその製造方法

【課題】 炭化珪素の半導体装置において、電極材料と、内部配線の材料とが異なるとき、これら異種金属の接触界面における不具合のおそれを無くして、長期間使用後にも高い信頼性を得ることができる、半導体装置等を提供する。

【解決手段】 炭化珪素14,18に接触する接触電極16と、該接触電極と導通する配線19とを備え、接触電極16が、チタン、アルミニウム、および珪素を含有する合金で形成され、配線19は、アルミニウムまたはアルミニウム合金で形成され、該配線は接触電極と接触することで該接触電極と導通をとることを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】保護素子としてSBDを搭載したMOSFETにおいては、SBDの特性を確保するためアルミニウム・ソース電極下のアルミニウム拡散バリア・メタル膜として、TiW(タングステンを主要な成分とする合金)膜が使用される。しかし、本願発明者らが検討したところによると、タングステン系バリア・メタル膜はTiN等のチタン系バリア・メタル膜と比べて、バリア性が低い柱状粒塊を呈するため、比較的容易にシリコン基板中にアルミニウム・スパイクが発生することが明らかとなった。

【解決手段】本願発明は、アルミニウム系メタル層と下層のシリコン系半導体層の間のバリア・メタル層として、タングステン系バリア・メタル膜をスパッタリング成膜によって形成する際、その下層をウエハ側にバイアスを印加したイオン化スパッタにより成膜し、上層をウエハ側にバイアスを印加しないスパッタにより成膜するものである。

(もっと読む)

半導体装置及びその製造方法

【課題】 貫通電極を有する半導体装置の信頼性及び歩留まりの向上を図る。

【解決手段】 本発明の半導体装置は、半導体チップ10Aと、前記半導体チップ10Aの表面上に第1の絶縁膜11を介して形成されたパッド電極12と、前記パッド電極12の一部上及び前記第1の絶縁膜11上に形成され、かつ前記パッド電極12を露出する開口部14を有した第2の絶縁膜13と、前記開口部14を通して前記パッド電極12と電気的に接続されて前記第2の絶縁膜11の一部上に延びる第1の配線層15と、前記パッド電極12を介して前記開口部14に対峙し、前記半導体チップ10Aの裏面から当該パッド電極12に到達し、かつ前記開口部14と実質的に同等の開口径を有するビアホール16と、前記ビアホール16内に形成され、かつ当該ビアホール16を通して前記パッド電極12と電気的に接続された貫通電極20と、を備えることを特徴とする。

(もっと読む)

半導体装置

【課題】第1回路と第2回路の信号電圧が異なる場合でも、第1回路と第2回路の間の絶縁を容易に確保することができるようにする。

【解決手段】半導体チップ10は、第1回路100、及び第1インダクタ302を有している。半導体チップ20は、第2回路200、及びチップ側接続端子545を有している。 配線基板60は、半導体チップ10上から半導体チップ20に渡って取り付けられている。配線基板60は、第2インダクタ304、及び基板側接続端子610を有している。第2インダクタ304は第1インダクタ302の上方に位置している。チップ側接続端子545と2つの基板側接続端子610は、第1ハンダボール700を介して接続している。

(もっと読む)

半導体装置

【課題】外部から侵入する水分に起因した再配線どうしのショートが防止された半導体装置を提供する。

【解決手段】本発明の半導体装置10は、半導体基板12と、半導体基板12上に形成された第1樹脂層30と、第1樹脂層30の上面に形成されてパッド部44を構成する再配線48と、この再配線48および第1樹脂層30の上面を被覆する第2樹脂層32とを備えている。そして、パッド部44は、第2樹脂層の開口部13から露出する露出領域44Aと、第2樹脂層32により被覆される被覆領域44Bとから成り、この被覆領域44Bの幅(L1)を10μm以上としている。

(もっと読む)

半導体装置の製造方法

【課題】最新の0.15μmパワーMOSFETにおいては、微細化によるセル・ピッチの縮小のためトレンチ部(ソース・コンタクト用の溝)において、アルミニウム・ボイド(アルミニウム系電極内に形成されるボイド)が多発することが、本願発明者らによって明らかにされた。この欠陥の発生は、主にアスペクト比が前世代の0.84から一挙に2.8に上昇したことによると考えられる。

【解決手段】本願の一つの発明は、アスペクト比の大きい繰り返し溝等の凹部をアルミニウム系メタルで埋め込む際に、アルミニウム系メタル・シード膜の形成から埋め込みに至るまで、イオン化スパッタリングにより、実行するものである。

(もっと読む)

半導体装置

【目的】プロービング試験での導電パッド下に配置された金属配線上の絶縁膜のクラック発生を抑制することが可能な半導体装置を提供することを目的とする。

【構成】本発明の一態様の半導体装置は、導電パッドと、前記導電パッド上に配置され、前記導電パッドの一部が露出するように開口領域が形成された第1の絶縁膜と、前記導電パッドの下方に配置された第2の絶縁膜と、銅(Cu)を用いた配線を有し、前記第2の絶縁膜を介して前記導電パッドの下方に配置され、前記開口領域と重なる領域での最上層における前記配線の最大配線幅w(nm)と前記配線の被覆率R(%)とがある条件を満たすように配置された少なくとも1層の配線層と、を備えたことを特徴とする。

(もっと読む)

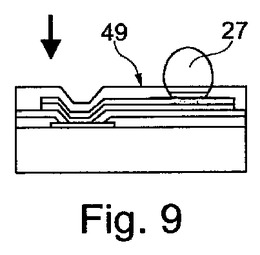

基板接触のためのコンタクト配置

この発明は、基板接触、特に半導体基板(21)の端子面を接触させるためのコンタクト配置(47,48,49,50,55,56,57)に関し、基板の底部端子面によって基板表面に形成された、コンタクト配置の少なくとも1つの内側コンタクト(25)と、内側コンタクトの外側端縁領域と周辺部とを少なくとも被覆するパッシベーション層(34,35)と、内側コンタクト(25)から横方向に離れるようにパッシベーション層(34,35)の上に延在する少なくとも1つの下側コンタクトストリップ(36)と、下側コンタクトストリップの上に延在するもう1つの上側のコンタクトストリップ(37,38,39)とを含み、このもう1つのコンタクトストリップは、コンタクトメタライゼーションによって形成されており、このコンタクトメタライゼーションは、ニッケル(Ni)層からまたはニッケルとパラジウム(Pd)とを含有する層構造(38,39)から実質的に構成される。  (もっと読む)

(もっと読む)

半導体装置とその製造方法、電気光学装置とその製造方法、回路基板とその製造方法、及び電子機器

【課題】フォトリソグラフィー法及びエッチング法を用いることなく導電層間を接続することができる半導体装置の製造方法を提供する。

【解決手段】本発明の半導体装置の製造方法は、基板上に第1導電層と層間絶縁膜と第2導電層とを順に積層形成する導電層工程と、前記第2導電層の表面から物理的加工を施すことで、前記第2導電層と前記層間絶縁膜とを貫通して前記第1導電層に達する凹部を形成するコンタクトホール形成工程と、を有することを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】微細化に対応可能であり、不純物拡散領域上に形成したコンタクトプラグが近傍の導電材料とショートすることを防止する配線構造を有する半導体装置を提供する。

【解決手段】半導体基板内の不純物拡散領域22上に選択エピタキシャル成長法により、第1の層16aを形成する工程と、第1の層16a上に、選択エピタキシャル成長法により第2の層18を形成する工程と、第2の層18上に導電材料を充填することにより、コンタクトプラグ21を形成する工程と、を有する。

(もっと読む)

半導体装置

【課題】コンタクトホールの加工時において配線のダメージを受けにくく、信頼性の低下を抑制できる構造の接続部を有する半導体装置を提供すること。

【解決手段】接続部1は、第1導電層2と第2導電層4とが、その交差個所に設けられたコンタクトホール5を介して接続されたものである。矩形状のコンタクトホール5は第2導電層4の幅方向の略中央に配置されている。そして、コンタクトホール5のパターンを囲むように矩形状の半導体層3が設けられている。半導体層3は、コンタクトホール5の底部において第1導電層2上に形成されている。この半導体層3は、第1導電層2とのエッチング選択比が高く、第1導電層2に対するエッチング効率が充分に高いものである。

(もっと読む)

半導体装置の製造方法及び半導体基板

【課題】表面に段差部分を有する構造物を覆う上部絶縁膜を基板全面に亘って均一に表面平坦化し、上部絶縁膜の表面平坦化及び膜厚均一化を共に実現して、所期の半導体素子を安定且つ確実に形成する。

【解決手段】半導体基板1上に、多層配線構造の下層部分2を適宜形成した後、半導体基板1のベベル部1aを覆うように、下層部分2と略同等の膜厚に縁部絶縁膜14を形成し、上部絶縁膜11aをCMPで表面研磨して平坦化する。

(もっと読む)

マスクを使用せずに導電性ビアに対して裏面位置合わせを行うことによる半導体構成部品の製造方法

半導体構成部品(90)を製造する方法が、回路面(54)と、裏面(56)と、導電性ビア(58)とを有する半導体基板(52)を提供するステップと、導電性ビア(58)の端子部分(76)を露出するために、基板(52)の一部分を裏面(56)から除去するステップと、端子部分(76)を封入するポリマー層(78)を裏面(56)に堆積するステップと、次いで、ポリマー層(78)および端子部分(76)の端部を平坦化して、ポリマー層(78)に埋め込まれた自己整合導体を形成するステップとを含む。導電性ビア(58)に電気的に接触させて、端子接点(86)や裏面再分配導体(88)等の追加の裏面要素を形成することもできる。半導体構成部品(90)は、半導体基板(52)と、導電性ビア(58)と、およびポリマー層(78)に埋め込まれた裏面導体とを有する。積重ね半導体構成部品(96)が、電気的に互いに通じる位置の整合した導電性ビア(58)を有する複数の構成部品(90-1、90-2、90-3)を有する。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】シード膜の酸化を抑制して、電気的信頼性の低下を抑制することができる半導体装置の製造方法を提供する。

【解決手段】本発明の一の態様によれば、表面に凹部1aを有する基板100の少なくとも凹部1aの内面1b上に、シード膜5を形成する工程と、シード膜5上に、シード膜5の構成材料より酸化されやすい材料からなる保護膜6を形成する工程と、保護膜6に熱処理を施す工程と、熱処理が施された保護膜6の少なくとも一部を除去し、シード膜5の少なくとも一部を露出させる工程と、少なくとも一部が露出したシード膜5に電流を供給して、シード膜5上に凹部1aに埋め込まれるように電解めっきによりめっき膜7を形成する工程と、凹部1aに埋め込まれた部分以外のめっき膜7を除去する工程とを具備することを特徴とする、半導体装置の製造方法が提供される。

(もっと読む)

ヒューズ式スルー・シリコン・ビアを有する3Dチップ・スタック

【課題】シリコン・チップ中のプログラム可能ヒューズ式スルーシリコン・ビア(TSV)を、同一のチップ中の非プログラム型TSVと併せ提供する。

【解決手段】該プログラム可能ヒューズ式TSVには、該TSV構造内に、チップ表面コンタクト・パッドに隣接するTSVの導電路の断面を限定する側壁スペーサを有する部域を用いることができる。プログラミング回路による十分な電流の印加により、金属のエレクトロマイグレーションが生じ、コンタクト・パッド中にボイド、しかしてオープン回路、が生成される。プログラミングは、多階層チップ・スタック中の2つの隣接するチップ上の相補的回路によって実行することができる。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】配線層に新たな機能を有する素子を設けた半導体装置を提供する。

【解決手段】半導体基板上に形成された第1配線層150、及び半導体素子200を備える。第1配線層150は、絶縁層156と、絶縁層156の表面に埋め込まれた第1配線154とを備える。半導体素子200は、半導体層220、ゲート絶縁膜160、及びゲート電極210を備える。半導体層220は、第1配線層150上に位置する。ゲート絶縁膜160は、半導体層220の上又は下に位置する。ゲート電極210は、ゲート絶縁膜160を介して半導体層220の反対側に位置する。

(もっと読む)

半導体装置及びその製造方法

【課題】Q値の高いモノリシックインダクタ素子を備える半導体装置及びその製造方法を提供する。

【解決手段】半導体装置50は、半導体基板1と、半導体基板1上に設けられた層間絶縁膜6と、層間絶縁膜6の上部に埋め込むように設けられ、スパイラルパターンを有する第1インダクタ配線層7と、層間絶縁膜6上及び第1インダクタ配線層7上を覆うように設けられ、第1インダクタ配線層7に沿って延びる少なくとも一つの溝状接続孔10を有するバリア絶縁膜9と、バリア絶縁膜10上に、第1インダクタ配線層7に沿って延びるように形成されると共に、溝状接続孔10を埋め込んで第1インダクタ配線層7に電気的に接続された第2インダクタ配線層11とを備える。第2インダクタ配線層11は、その長さ方向に延びるように上面側に設けられた少なくとも一つの溝状凹部12を有する。

(もっと読む)

配線構造

【課題】断線が発生することを抑制可能な配線構造を提供する。

【解決手段】始めに、半導体装置の表面にアルミニウム金属膜5を形成する。次に半導体装置の表面に窒化チタン膜6を形成する。そして最後に半導体装置の表面にアルミニウム金属膜7を形成する。すなわち、シリコン基板1と電極4とを接続する電気配線を金属膜の3層構造により段階的に形成する。これにより、シリコン基板1と絶縁膜2との間に形成される段差の底部部分において金属膜の被覆率が低くなることによって断線が生じることを防止できる。

(もっと読む)

半導体装置

【課題】従来の透過型液晶パネル向け半導体装置を小型化し、マイクロディスプレイを実現しようとするとき、半導体装置と透明電極とを接続するビアホールの径が縮小するため、接触抵抗が高くなるという問題があった。また、接触抵抗低減のために、半導体装置と透明電極との間に中間金属層を設けると、画素の開口率が低下し、画面が暗くなるという課題があった。

【解決手段】本発明の半導体装置は、半導体装置と透明電極との間に設ける中間金属層に切欠部を有する。この切欠部により、中間金属層の側面の面積を拡大し、透明電極との接触面積を従来よりも大きくすることができる。また、中間金属層の側面部面積を利用するため、画素表面に対する投影面積を小さく設定でき、画素の開口率を大きくすることができる。このため、十分な明るさをもつ、超小型のマイクロディスプレイを提供できる。

(もっと読む)

半導体装置及びその製造方法

【課題】パッド電極の直下でのクラックの発生を抑制できるようにした半導体装置及びその製造方法を提供する。

【解決手段】シリコン基板1と、シリコン基板1上に形成されたLOCOS膜3と、LOCOS膜3上に形成されたポリシリコン膜5と、LOCOS膜3上に形成されたILD膜7と、ILD膜7に形成され、ポリシリコン膜5を底面とする第1の開口部と、第1の開口部内に形成され、ポリシリコン膜5と接するパッド電極9と、を有する。ポリシリコン膜5は、ILD膜7よりも強度があり、衝撃に対する耐性が高いため、プローブ検査の際にクラックの発生を抑制することができる。

(もっと読む)

61 - 80 / 357

[ Back to top ]